Intel 8259 - Programmable Interrupt Controller

Download as PPTX, PDF20 likes8,037 views

The 8259 Programmable Interrupt Controller (PIC) is used to expand the number of interrupts for processors like the 8085. It can manage up to 8 interrupt requests at once and allow them to be serviced one by one. The 8259 can be programmed to determine interrupt priorities and masking. It is interfaced with the 8085 through I/O mapping and provides the interrupt acknowledge response by outputting the call opcode and address.

1 of 15

Downloaded 617 times

Recommended

Interrupts of microprocessor 8085

Interrupts of microprocessor 8085mujeebkhanelectronic

╠²

The document discusses interrupts in the 8085 microprocessor. It defines interrupts as a mechanism to suspend normal execution and service external devices or instructions. The 8085 has hardware and software interrupts. Hardware interrupts can be maskable or non-maskable. Maskable interrupts like RST 7.5, 6.5, 5.5 and INTR can be enabled and disabled, while the non-maskable TRAP interrupt cannot. Software interrupts use RST instructions to redirect execution to subroutines.8259 Programmable Interrupt Controller

8259 Programmable Interrupt Controllerabhikalmegh

╠²

PIC A special purpose integrated circuit that function as an overall manager in an interrupt driven system.

’é×It accepts request from the peripheral equipment,determines which of the incoming request is of the highest priority, ascertains whether the incoming request has a higher priority value than the level currently being serviced, and issues an interrupt to the CPU based on this determination.8051 Microcontroller PPT's By Er. Swapnil Kaware

8051 Microcontroller PPT's By Er. Swapnil KawareProf. Swapnil V. Kaware

╠²

The document describes the 8051 microcontroller, its features which include 4 I/O ports, 2 timers, serial communication interface, and interrupts. It discusses the internal architecture such as memory organization, registers, and oscillator circuit. The document also provides details on the ports, timers, serial communication, and power modes of the 8051 microcontroller.8237 dma controller

8237 dma controllerTech_MX

╠²

The 8237 DMA controller allows data transfer between I/O devices and memory without CPU intervention. It uses HOLD and HLDA signals to request and acknowledge DMA actions from the CPU. The 8237 contains registers like CAR, CWCR, CR, and SR to program DMA channel operations, addresses, counts, and status. It can perform DMA transfers at up to 1.6 MB/s across 4 channels. Modern systems integrate DMA controllers within chipsets rather than using discrete 8237 components.Microprocessor 8085 complete

Microprocessor 8085 completeShubham Singh

╠²

The document provides an overview of microprocessors and the 8085 microprocessor architecture. It discusses that a microprocessor is a programmable VLSI chip that includes an ALU, registers, and control circuits. The 8085 is an 8-bit microprocessor that can address 64KB of memory. It has three main functional blocks - a register array, ALU and logical group, and instruction decoder/timing and control circuitry. The document also describes the various registers, buses, pins and control signals of the 8085 microprocessor.UNIT 2 8086 System Bus Structure.pptx

UNIT 2 8086 System Bus Structure.pptxGowrishankar C

╠²

The document discusses the 8086 system bus structure. It describes the various signals of the 8086 microprocessor like the address/data bus, control signals, and clock. It explains the minimum and maximum modes of the 8086. The system bus consists of data, address, and control buses. Interrupt-driven and programmed I/O as well as direct memory access transfers are introduced. Multiprogramming and various multiprocessor configurations like coprocessor, closely coupled, and loosely coupled systems are summarized.8255 PPI

8255 PPIdeval patel

╠²

The document discusses interfacing concepts and the Intel 8255 Programmable Peripheral Interface chip. It provides information on:

- Memory mapped I/O and I/O mapped I/O interfacing techniques.

- The 8255 PPI chip which has 3 8-bit I/O ports (Ports A, B, and C) that can be configured as input or output ports. It operates in I/O mode or Bit Set/Reset mode.

- Control word formats for configuring the ports in different modes like Mode 0, 1, and 2 for I/O mode and Bit Set/Reset mode.

- Example programs to initialize the 8255 ports using control words for different8257 DMA Controller

8257 DMA ControllerShivamSood22

╠²

The DMA controller (8257) allows data transfer between I/O devices and memory without CPU involvement. It has 4 independent channels that can be programmed to transfer data via DMA read, write, or verify operations. The 8257 interfaces with the 8085 microprocessor by controlling address/data buses and generating control signals during DMA cycles when it acts as the bus master.3.programmable interrupt controller 8259

3.programmable interrupt controller 8259MdFazleRabbi18

╠²

The document describes the Intel 8259 programmable interrupt controller chip. It contains blocks for buffering data to and from the system data bus, controlling read/write signals, storing interrupt requests in the interrupt request register, masking interrupts in the interrupt mask register, tracking interrupts being serviced in the in-service register, resolving interrupt priorities, and cascading multiple 8259 chips. The pin diagram shows inputs for interrupt requests, read/write control, an ID comparator for cascading, and an 8-bit data bus.8253ppt

8253pptBharani Samrat

╠²

The 8253 is a programmable timer/counter chip used in Intel microcomputers. It has 3 counters and 6 programmable modes. The modes determine how the OUT signal behaves, such as pulsing low/high periodically or non-periodically. The control byte programs the counter selection, read/write mode, count mode, and binary/BCD selection. Common uses include creating time intervals and counting events.PIC 16F877A by PARTHIBAN. S.

PIC 16F877A by PARTHIBAN. S.parthi_arjun

╠²

The PIC 16F877A microcontroller uses a Harvard architecture with separate program and data buses. It has 8kB of flash memory, 368 bytes of RAM, and 256 bytes of EEPROM. It features five I/O ports, three timers, USART serial communication, and 15 interrupt sources. Instructions are in RISC format and execute in 4 machine cycles, with most instructions completing in one cycle.8259 Interrupt Controller

8259 Interrupt ControllerShivamSood22

╠²

The 8259A Programmable Interrupt Controller (PIC) handles prioritized interrupt requests from peripherals for the CPU. It accepts up to 8 interrupt requests, determines priority, and issues an interrupt to the CPU. It can be programmed and cascaded to handle more interrupts. The PIC includes registers to store incoming requests, mask bits, and service status. It uses initialization and operation command words to configure operation and interact with the CPU through control signals and data bus.8086 modes

8086 modesPDFSHARE

╠²

The document discusses the minimum and maximum mode systems of the 8086 microprocessor. In minimum mode, the 8086 generates all control signals and a single processor is used. In maximum mode, an external bus controller chip generates control signals and multiple processors can be used. It describes the components, address latching, read and write cycles, and I/O interfacing for both minimum and maximum mode 8086 systems.MICROCONTROLLER 8051

MICROCONTROLLER 8051PUNE VIDYARTHI GRIHA'S COLLEGE OF ENGINEERING, NASHIK

╠²

The document provides an overview of the 8051 microcontroller, including its history, architecture, memory organization, registers, I/O ports, and other key features. Some of the main points covered include:

- The 8051 was one of the earliest microcontrollers developed by Intel in 1980 and features 40 pins, 4K ROM, 128B RAM, and four 8-bit I/O ports.

- It has separate memory spaces for program and data memory up to 64KB each. Internal memory includes on-chip ROM and RAM, while external memory can be added.

- Special function registers (SFRs) are located at the top of internal RAM and include registers like ACC, BMinimum Modes and Maximum Modes of 8086 Microprocessor

Minimum Modes and Maximum Modes of 8086 MicroprocessorNikhil Kumar

╠²

The document discusses the minimum and maximum modes of the Intel 8086 microprocessor. In minimum mode, the 8086 generates its own control signals to interface with memory and I/O, while in maximum mode it requires an 8288 bus controller to generate the control signals. Minimum mode has limitations and does not support the 8087 coprocessor, while maximum mode allows use of the coprocessor and provides additional functions. Key signals in minimum mode include the address/data bus lines, status lines, control signals like ALE and M/IO, and interrupt lines.PPT on 8085 Microprocessor

PPT on 8085 Microprocessor DebrajJana4

╠²

The document provides information about the 8085 microprocessor. It begins with an introduction and pin diagram. It then describes the pin functions and architecture, including the arithmetic logic unit, registers, program counter, and stack pointer. It discusses the timing and states of memory read, write, and I/O cycles. It explains how to interface memory and I/O devices to the 8085 bus. It covers the different interrupt types and how the 8085 responds to interrupts. Finally, it provides a short code example to add two numbers.8259 a

8259 aMeghaditya Roy Chaudhury

╠²

The document describes the 8259 programmable interrupt controller. It has 8 interrupt request lines that can be expanded to 64. It determines the priority of incoming interrupts and issues an interrupt signal to the CPU. Upon receiving an interrupt acknowledgement from the CPU, it provides vectoring data through 3 INTA pulses to direct the CPU to the appropriate interrupt service routine. It is programmed using initialization command words and operation command words to set interrupt priorities, masks, and modes.8085 microprocessor ramesh gaonkar

8085 microprocessor ramesh gaonkarSAQUIB AHMAD

╠²

The document discusses the microprocessor 8085. It covers the following topics over 5 weeks: basic concepts of microprocessors, the architecture of the 8085, addressing modes and instruction set, interrupts, and peripherals. The 8085 is an 8-bit microprocessor that uses 246 bit patterns to form its 74 instruction set. An assembly language uses mnemonics like "INR A" to represent instructions, making programs easier for humans to understand compared to machine language.8051 instruction set

8051 instruction setAndri Prastiyo

╠²

The document describes the instruction set of the 8051 microprocessor. It is divided into 5 groups: arithmetic, logic, data transfer, boolean, and branching instructions. The arithmetic instructions include ADD, ADDC, DA for decimal adjust, and INC/DEC. Logic instructions include ANL, ORL, and SWAP. Data transfer instructions move data between registers and memory. Boolean instructions manipulate individual bits. Branching instructions include conditional jumps, calls, and returns.Interfacing with peripherals: analog to digital converters and digital to ana...

Interfacing with peripherals: analog to digital converters and digital to ana...NimeshSingh27

╠²

A MCMP presentation on Interfacing with peripherals: analog to digital converters and digital to analog converters in 8086 ARM Processors

ARM ProcessorsMathivanan Natarajan

╠²

Presents features of ARM Processors, ARM architecture variants and Processor families. Further presents, ARM v4T architecture, ARM7-TDMI processor: Register organization, pipelining, modes, exception handling, bus architecture, debug architecture and interface signals. 8086 micro processor

8086 micro processorPoojith Chowdhary

╠²

The Intel 8086 is a 16-bit microprocessor that can access up to 1 MB of memory. It has two main components: the Bus Interface Unit (BIU) handles bus operations like instruction fetching and memory access, while the Execution Unit (EU) decodes and executes instructions. The BIU contains registers for the code, data, extra, and stack segments as well as an instruction queue. The EU has registers for accumulation, base, count, data, pointers, and flags, and contains an ALU and decoder. It executes instructions from the queued bytes using a pipeline architecture.1.ppi 8255

1.ppi 8255 MdFazleRabbi18

╠²

The document provides information about the Intel 8255 Programmable Peripheral Interface chip. It includes a block diagram and descriptions of the main components. The 8255 has 3 8-bit ports (A, B, C) that can be configured in different operating modes for input/output. It describes the pin functions and how the 8255 can interface with the Intel 8085 microprocessor. The main operating modes - I/O, bit set/reset, and the various configurations for ports A, B and C in each mode - are summarized.8255 presentaion.ppt

8255 presentaion.pptkamlesh deshmukh

╠²

The 8255 Programmable Peripheral Interface chip is used to interface I/O devices with microprocessors. It has 3 ports - Port A, Port B, and Port C. Port C has two independent 4-bit ports. The 8255 can operate in I/O mode or Bit Set/Reset mode. In I/O mode, the ports can be configured for basic, strobed, or bidirectional I/O. The mode and port configurations are set using control words written to the chip.Chapter 6 hardware structure of 8086

Chapter 6 hardware structure of 8086SHREEHARI WADAWADAGI

╠²

This document discusses the hardware structure and pin configurations of the Intel 8086 and 8088 microprocessors. It describes the differences between the 8086 and 8088, including their data bus widths, instruction queues, and specific pin functions. The pin diagrams and functions of pins in both minimum and maximum modes are explained. Key concepts covered include address/data demultiplexing, bus cycles, control signals, clock generation, and interrupt handling. Wait states, direct memory access, and the roles of the bus controller IC and request/grant pins in maximum mode configurations are also summarized.Timing diagram 8085 microprocessor

Timing diagram 8085 microprocessorVelalar College of Engineering and Technology

╠²

The document discusses the timing diagram of the 8085 microprocessor. It explains that a timing diagram is a graphical representation of the execution time of each instruction. It then describes the different machine cycles of the 8085 including the opcode fetch cycle, memory read cycle, memory write cycle, I/O read cycle, I/O write cycle, and interrupt acknowledge cycle. It provides details on the T-states within each machine cycle and examples of timing diagrams for different instructions like STA, IN, OUT, MVI, INR and ADD. Finally, it lists several references used to collect information on the 8085 timing diagram.System bus timing 8086

System bus timing 8086mpsrekha83

╠²

The document summarizes the timing of the system bus for the 8086 microprocessor. It describes that a machine cycle consists of at least four clock periods called T1, T2, T3, and T4. For a read bus cycle, the address is sent out in T1, read/write signals appear in T2 along with data for a write, T3 can be a wait state if ready is low, and data is sampled in T4. A write bus cycle outputs the address in T1, data in T2, and a write signal to memory.Programmable peripheral interface 8255

Programmable peripheral interface 8255Marajulislam3

╠²

8255 is a programmable I/O device that acts as an interface between peripheral devices and the microprocessor for parallel data transfer.8259

8259Mohansonale1

╠²

The document discusses the 8259 Programmable Interrupt Controller (PIC), which simplifies interrupt handling in 8088/8086 microcomputer systems. The PIC can handle up to 8 interrupts and can be cascaded to handle up to 64 interrupts. It is programmable via initialization command words and operation command words to configure interrupt priorities, vector numbers, and other settings. The PIC includes registers to track interrupt requests, masking, and service status to properly handle interrupt processing.More Related Content

What's hot (20)

3.programmable interrupt controller 8259

3.programmable interrupt controller 8259MdFazleRabbi18

╠²

The document describes the Intel 8259 programmable interrupt controller chip. It contains blocks for buffering data to and from the system data bus, controlling read/write signals, storing interrupt requests in the interrupt request register, masking interrupts in the interrupt mask register, tracking interrupts being serviced in the in-service register, resolving interrupt priorities, and cascading multiple 8259 chips. The pin diagram shows inputs for interrupt requests, read/write control, an ID comparator for cascading, and an 8-bit data bus.8253ppt

8253pptBharani Samrat

╠²

The 8253 is a programmable timer/counter chip used in Intel microcomputers. It has 3 counters and 6 programmable modes. The modes determine how the OUT signal behaves, such as pulsing low/high periodically or non-periodically. The control byte programs the counter selection, read/write mode, count mode, and binary/BCD selection. Common uses include creating time intervals and counting events.PIC 16F877A by PARTHIBAN. S.

PIC 16F877A by PARTHIBAN. S.parthi_arjun

╠²

The PIC 16F877A microcontroller uses a Harvard architecture with separate program and data buses. It has 8kB of flash memory, 368 bytes of RAM, and 256 bytes of EEPROM. It features five I/O ports, three timers, USART serial communication, and 15 interrupt sources. Instructions are in RISC format and execute in 4 machine cycles, with most instructions completing in one cycle.8259 Interrupt Controller

8259 Interrupt ControllerShivamSood22

╠²

The 8259A Programmable Interrupt Controller (PIC) handles prioritized interrupt requests from peripherals for the CPU. It accepts up to 8 interrupt requests, determines priority, and issues an interrupt to the CPU. It can be programmed and cascaded to handle more interrupts. The PIC includes registers to store incoming requests, mask bits, and service status. It uses initialization and operation command words to configure operation and interact with the CPU through control signals and data bus.8086 modes

8086 modesPDFSHARE

╠²

The document discusses the minimum and maximum mode systems of the 8086 microprocessor. In minimum mode, the 8086 generates all control signals and a single processor is used. In maximum mode, an external bus controller chip generates control signals and multiple processors can be used. It describes the components, address latching, read and write cycles, and I/O interfacing for both minimum and maximum mode 8086 systems.MICROCONTROLLER 8051

MICROCONTROLLER 8051PUNE VIDYARTHI GRIHA'S COLLEGE OF ENGINEERING, NASHIK

╠²

The document provides an overview of the 8051 microcontroller, including its history, architecture, memory organization, registers, I/O ports, and other key features. Some of the main points covered include:

- The 8051 was one of the earliest microcontrollers developed by Intel in 1980 and features 40 pins, 4K ROM, 128B RAM, and four 8-bit I/O ports.

- It has separate memory spaces for program and data memory up to 64KB each. Internal memory includes on-chip ROM and RAM, while external memory can be added.

- Special function registers (SFRs) are located at the top of internal RAM and include registers like ACC, BMinimum Modes and Maximum Modes of 8086 Microprocessor

Minimum Modes and Maximum Modes of 8086 MicroprocessorNikhil Kumar

╠²

The document discusses the minimum and maximum modes of the Intel 8086 microprocessor. In minimum mode, the 8086 generates its own control signals to interface with memory and I/O, while in maximum mode it requires an 8288 bus controller to generate the control signals. Minimum mode has limitations and does not support the 8087 coprocessor, while maximum mode allows use of the coprocessor and provides additional functions. Key signals in minimum mode include the address/data bus lines, status lines, control signals like ALE and M/IO, and interrupt lines.PPT on 8085 Microprocessor

PPT on 8085 Microprocessor DebrajJana4

╠²

The document provides information about the 8085 microprocessor. It begins with an introduction and pin diagram. It then describes the pin functions and architecture, including the arithmetic logic unit, registers, program counter, and stack pointer. It discusses the timing and states of memory read, write, and I/O cycles. It explains how to interface memory and I/O devices to the 8085 bus. It covers the different interrupt types and how the 8085 responds to interrupts. Finally, it provides a short code example to add two numbers.8259 a

8259 aMeghaditya Roy Chaudhury

╠²

The document describes the 8259 programmable interrupt controller. It has 8 interrupt request lines that can be expanded to 64. It determines the priority of incoming interrupts and issues an interrupt signal to the CPU. Upon receiving an interrupt acknowledgement from the CPU, it provides vectoring data through 3 INTA pulses to direct the CPU to the appropriate interrupt service routine. It is programmed using initialization command words and operation command words to set interrupt priorities, masks, and modes.8085 microprocessor ramesh gaonkar

8085 microprocessor ramesh gaonkarSAQUIB AHMAD

╠²

The document discusses the microprocessor 8085. It covers the following topics over 5 weeks: basic concepts of microprocessors, the architecture of the 8085, addressing modes and instruction set, interrupts, and peripherals. The 8085 is an 8-bit microprocessor that uses 246 bit patterns to form its 74 instruction set. An assembly language uses mnemonics like "INR A" to represent instructions, making programs easier for humans to understand compared to machine language.8051 instruction set

8051 instruction setAndri Prastiyo

╠²

The document describes the instruction set of the 8051 microprocessor. It is divided into 5 groups: arithmetic, logic, data transfer, boolean, and branching instructions. The arithmetic instructions include ADD, ADDC, DA for decimal adjust, and INC/DEC. Logic instructions include ANL, ORL, and SWAP. Data transfer instructions move data between registers and memory. Boolean instructions manipulate individual bits. Branching instructions include conditional jumps, calls, and returns.Interfacing with peripherals: analog to digital converters and digital to ana...

Interfacing with peripherals: analog to digital converters and digital to ana...NimeshSingh27

╠²

A MCMP presentation on Interfacing with peripherals: analog to digital converters and digital to analog converters in 8086 ARM Processors

ARM ProcessorsMathivanan Natarajan

╠²

Presents features of ARM Processors, ARM architecture variants and Processor families. Further presents, ARM v4T architecture, ARM7-TDMI processor: Register organization, pipelining, modes, exception handling, bus architecture, debug architecture and interface signals. 8086 micro processor

8086 micro processorPoojith Chowdhary

╠²

The Intel 8086 is a 16-bit microprocessor that can access up to 1 MB of memory. It has two main components: the Bus Interface Unit (BIU) handles bus operations like instruction fetching and memory access, while the Execution Unit (EU) decodes and executes instructions. The BIU contains registers for the code, data, extra, and stack segments as well as an instruction queue. The EU has registers for accumulation, base, count, data, pointers, and flags, and contains an ALU and decoder. It executes instructions from the queued bytes using a pipeline architecture.1.ppi 8255

1.ppi 8255 MdFazleRabbi18

╠²

The document provides information about the Intel 8255 Programmable Peripheral Interface chip. It includes a block diagram and descriptions of the main components. The 8255 has 3 8-bit ports (A, B, C) that can be configured in different operating modes for input/output. It describes the pin functions and how the 8255 can interface with the Intel 8085 microprocessor. The main operating modes - I/O, bit set/reset, and the various configurations for ports A, B and C in each mode - are summarized.8255 presentaion.ppt

8255 presentaion.pptkamlesh deshmukh

╠²

The 8255 Programmable Peripheral Interface chip is used to interface I/O devices with microprocessors. It has 3 ports - Port A, Port B, and Port C. Port C has two independent 4-bit ports. The 8255 can operate in I/O mode or Bit Set/Reset mode. In I/O mode, the ports can be configured for basic, strobed, or bidirectional I/O. The mode and port configurations are set using control words written to the chip.Chapter 6 hardware structure of 8086

Chapter 6 hardware structure of 8086SHREEHARI WADAWADAGI

╠²

This document discusses the hardware structure and pin configurations of the Intel 8086 and 8088 microprocessors. It describes the differences between the 8086 and 8088, including their data bus widths, instruction queues, and specific pin functions. The pin diagrams and functions of pins in both minimum and maximum modes are explained. Key concepts covered include address/data demultiplexing, bus cycles, control signals, clock generation, and interrupt handling. Wait states, direct memory access, and the roles of the bus controller IC and request/grant pins in maximum mode configurations are also summarized.Timing diagram 8085 microprocessor

Timing diagram 8085 microprocessorVelalar College of Engineering and Technology

╠²

The document discusses the timing diagram of the 8085 microprocessor. It explains that a timing diagram is a graphical representation of the execution time of each instruction. It then describes the different machine cycles of the 8085 including the opcode fetch cycle, memory read cycle, memory write cycle, I/O read cycle, I/O write cycle, and interrupt acknowledge cycle. It provides details on the T-states within each machine cycle and examples of timing diagrams for different instructions like STA, IN, OUT, MVI, INR and ADD. Finally, it lists several references used to collect information on the 8085 timing diagram.System bus timing 8086

System bus timing 8086mpsrekha83

╠²

The document summarizes the timing of the system bus for the 8086 microprocessor. It describes that a machine cycle consists of at least four clock periods called T1, T2, T3, and T4. For a read bus cycle, the address is sent out in T1, read/write signals appear in T2 along with data for a write, T3 can be a wait state if ready is low, and data is sampled in T4. A write bus cycle outputs the address in T1, data in T2, and a write signal to memory.Programmable peripheral interface 8255

Programmable peripheral interface 8255Marajulislam3

╠²

8255 is a programmable I/O device that acts as an interface between peripheral devices and the microprocessor for parallel data transfer.Similar to Intel 8259 - Programmable Interrupt Controller (20)

8259

8259Mohansonale1

╠²

The document discusses the 8259 Programmable Interrupt Controller (PIC), which simplifies interrupt handling in 8088/8086 microcomputer systems. The PIC can handle up to 8 interrupts and can be cascaded to handle up to 64 interrupts. It is programmable via initialization command words and operation command words to configure interrupt priorities, vector numbers, and other settings. The PIC includes registers to track interrupt requests, masking, and service status to properly handle interrupt processing.8259 A P R O G R A M M A B L E I N T E R R U P T C O N T R O L L E R2

8259 A P R O G R A M M A B L E I N T E R R U P T C O N T R O L L E R2Aisu

╠²

The 8259A Programmable Interrupt Controller (PIC) is used to handle multiple interrupt requests from I/O devices connected to CPUs. It can manage up to 8 interrupt requests with different priority levels. It consists of registers and logic circuits that prioritize interrupts and direct the CPU to the correct interrupt handling routine. It allows flexible and expandable interrupt management for systems with numerous I/O devices generating interrupts.8259a.pdf

8259a.pdfssusere55750

╠²

Based on the information provided:

- 8086 mode: Set IC4 bit to 1

- Single PIC: Set SNGL bit to 1

- Rising edge triggered: Set LTIM bit to 0

- Don't care bits: ADI, A7-A5 can be set to 0

Therefore, the value for ICW1 is:

1 0 0 0 0 0 0 08259 programmable PPI interfacing with 8085 .ppt

8259 programmable PPI interfacing with 8085 .pptDrVikasMahor

╠²

This document provides information about the 8259A Programmable Interrupt Controller chip. It describes the chip's features such as supporting 8 levels of priority and being expandable up to 64 levels. It also explains how the chip works as an interrupt manager in a system, accepting requests from peripherals and determining which has highest priority to issue to the CPU. Block diagrams and explanations of the chip's registers and pins are provided.8259 updated

8259 updated jemimajerome

╠²

The 8259A Programmable Interrupt Controller (PIC) handles interrupts from I/O devices for processors that have limited hardware interrupt pins. It supports up to 8 interrupt requests with configurable priority levels that can be expanded to 64 levels by cascading additional 8259A chips. The PIC consists of registers and logic to accept interrupt requests, determine priority, notify the processor, and provide the interrupt vector address. It is initialized via initialization command words and controlled via operation command words to configure operating modes like fully nested, automatic rotation, and specific rotation priority schemes.8259 programmable interrupt controller

8259 programmable interrupt controllerSrikrishna Thota

╠²

The 8259 Programmable Interrupt Controller (PIC) handles multiple interrupt requests from I/O devices connected to the CPU. It has 8 interrupt lines and can prioritize and process interrupts. It includes registers to store interrupt requests and service status, and can cascade with other PICs to handle more interrupts. When an interrupt occurs, the PIC sends a call instruction to the CPU, then the interrupt service routine address, allowing the CPU to service high-priority interrupts first in a multitasking system.Icws

Icwsmithleshks11

╠²

The 8259A is a programmable interrupt controller that can handle multiple interrupt requests simultaneously with defined priorities. It works with both 8-bit and 16-bit processors to provide more interrupt pins than are available from a single processor. The 8259A must be initialized through command words to configure its operation before it can function properly. The initialization sequence involves compulsory command words ICW1 and ICW2, as well as optional words ICW3 and ICW4 to configure master/slave operation or interrupt vector addresses.Microprocessor.pptx

Microprocessor.pptxSachinKupade

╠²

The document describes the pinouts and signals of the 8085 microprocessor IC. It discusses the 7 groups of pins - address bus, data bus, control/status signals, power supply, clock signals, interrupts/external signals, and serial I/O signals. It also summarizes the 5 addressing modes of the 8085 - immediate, register, direct, indirect, and implied. Finally, it provides details about the different types of interrupts in the 8085 including TRAP, RST 7.5, RST 6.5, RST 5.5, and INTR interrupts and interrupt service routines.8259 Programmable Interrupt Controller by vijay

8259 Programmable Interrupt Controller by vijayVijay Kumar

╠²

The 8259A Programmable Interrupt Controller (PIC) is used to simplify the interrupt interface of 8088/8086 microprocessor systems. It can accept up to 8 interrupt requests and expand to 64 requests by cascading additional PICs. The PIC is programmable through initialization command words to configure operating modes and interrupt vector assignments. It also has operation command words to control interrupt masking, priorities, and acknowledgement.8259.pptx

8259.pptxsrenr

╠²

The document provides information about the 8259 programmable interrupt controller (PIC). It describes the PIC's features such as supporting 8 interrupts, masking interrupts individually, and cascading capability to support up to 64 interrupts. It also includes the pin diagram and provides details about the PIC's internal blocks - data bus buffer, read/write and control logic, interrupt request register, interrupt mask register, in-service register, and priority resolver. The priority resolver determines if the INT signal should be sent to the processor based on the states of the other registers.B sc e5.2 mp unit 3 interfacing

B sc e5.2 mp unit 3 interfacingMahiboobAliMulla

╠²

The document discusses different methods of data transfer between a microprocessor and input/output devices. It describes programmed I/O, interrupt-driven I/O, and direct memory access (DMA) as common parallel data transfer schemes. For slower I/O devices, asynchronous or interrupt-driven methods are used to avoid wasted processor time waiting for the I/O device. Interrupt-driven I/O allows an I/O device to signal the processor when data is ready via an interrupt request, improving efficiency over programmed I/O.21262738 8259a-programmable-interrupt-controller-2

21262738 8259a-programmable-interrupt-controller-2lords_ko

╠²

The 8259A Programmable Interrupt Controller (PIC) allows for more interrupts than the 8085 processor's 5 hardware interrupts. It can handle multiple interrupts simultaneously with different priorities. It manages 8 interrupt lines and their priorities through control registers. It interfaces with the CPU through control words that initialize it and perform operations like masking interrupts. Cascading multiple 8259As allows for up to 64 interrupt levels to be managed.Microprocessor questions converted

Microprocessor questions convertedArghodeepPaul

╠²

The document discusses various topics related to microprocessors and computer architecture. It begins by providing details about the pins and functions of the 8085 microprocessor. It then discusses interfacing memory chips with the 8085 and provides an example. Next, it describes the block diagram and functions of the different units of the 8086 microprocessor. It also explains the different addressing modes used in 8086 with examples. The document then discusses the control word format for programming the I/O ports of the 8255 chip. In less than 3 sentences.UNIT 1 Microprocessors.pptx

UNIT 1 Microprocessors.pptxGowrishankar C

╠²

The document provides information about the 8085 microprocessor, including its architecture, features, instruction formats, and addressing modes. The 8085 is an 8-bit microprocessor with an accumulator, registers, arithmetic logic unit (ALU), flags, and I/O controls. It has three types of instructions that are 1, 2, or 3 bytes long. The addressing modes allow instructions to specify operands and include immediate, direct, register, register indirect, and implicit modes.Micro Processor And Micro Controller for engineering in Pondicherry University

Micro Processor And Micro Controller for engineering in Pondicherry UniversityShyamShyam76

╠²

This document provides an overview of memory and I/O interfacing concepts for microprocessors and microcontrollers. It discusses types of memory including RAM, ROM, and EEPROM and methods of memory mapping and addressing such as partial decoding and complete decoding. It also covers I/O interfacing topics like I/O mapping, interfacing switches and LEDs, the 8255 Programmable Peripheral Interface chip, and serial communication using the 8251 USART.Microprocessor and Microcontroller lec5

Microprocessor and Microcontroller lec5Ameen San

╠²

The document discusses the Intel 8085 microprocessor architecture. It describes the 8085's pin configuration and its address, data, control and status signal pins. It provides details on the CPU block diagram, including the ALU, flags register, and how the different units are connected via buses. It also explains the different machine cycles of the 8085 like opcode fetch, memory read/write, and I/O read/write.T-states in microprocessor 8085

T-states in microprocessor 8085yedles

╠²

The document provides information about microprocessors and the 8085 microprocessor. It defines key terms like microprocessor, ALU, registers, control unit, bus, machine cycle, T-state, instruction cycle, fetch cycle, execute cycle, flags, memory mapping, opcode fetch, interrupts, polling, and interrupt types. It describes the basic units and operations of a microprocessor, bus types, the instruction execution process, and interrupt handling. It also discusses I/O techniques, 8085 pins and signals, addressing modes, and differences between memory mapped and I/O mapped I/O.System Connection Of 8254 and Its Port Selection

System Connection Of 8254 and Its Port SelectionMohammedIrfanulAlamT

╠²

The document discusses the Intel 8254 programmable interval timer chip. It consists of three independent 16-bit counters that can count in binary or BCD. Each counter has a CLK input, gate input, and OUT output. The 8254 interfaces with the CPU via data, read, write, chip select, and address lines. It is commonly found in PCs and is decoded at ports 40H-43H, with timer 0 generating an 18.2 Hz interrupt, timer 1 refreshing DRAM, and timer 2 generating audio tones. The 8254 has 3 ports that can be configured by software for inputs/outputs and divided into smaller ports.Recently uploaded (20)

Hackathon-Problem-Statements-Technology-Track-with-Link.pptx

Hackathon-Problem-Statements-Technology-Track-with-Link.pptxdatahiverecruitment

╠²

Hackathon-Problem-Statements-Technology-Track-with-Link.pptxUHV UNIT-3 HARMONY IN THE FAMILY AND SOCIETY.pptx

UHV UNIT-3 HARMONY IN THE FAMILY AND SOCIETY.pptxariomthermal2031

╠²

HARMONY IN THE FAMILY AND SOCIETY DBMS Notes selection projection aggregate

DBMS Notes selection projection aggregateSreedhar Chowdam

╠²

Selection

Projection

Aggregate functions

Arithmetic & logical operationsGDGoC Artificial Intelligence Workshop.pptx

GDGoC Artificial Intelligence Workshop.pptxAditi330605

╠²

Presentation for Artificial Intelligence Workshop conducted by GDG on Campus Amity University Gurugram Virtual Power plants-Cleantech-Revolution

Virtual Power plants-Cleantech-RevolutionAshoka Saket

╠²

VPPs are virtual aggregations of distributed energy resources, such as energy storage, solar panels, and wind turbines, that can be controlled and optimized in real-time to provide grid services.Agentic architectures and workflows @ AIware Bootcamp 2024

Agentic architectures and workflows @ AIware Bootcamp 2024Keheliya Gallaba

╠²

In this talk, I dove deep into the world of agents, starting with some history of the term. We explored the core properties of agents, like autonomy, social ability, reactiveness, and proactiveness, and how these translate into the agentic systems we're seeing today. I broke down the anatomy of a foundation model-based agent, discussing environments, memory types (procedural, semantic, and episodic), and the role of external tools . We also looked at how these agents reason and plan, and even briefly touched on the concept of "theory of mind". Finally, I walked through some examples from research papers, like generative agents and software developer agents. I wrapped up with a look at the open research challenges, including control, human-agent interfaces, and evaluation.

Video recording of the talk: https://www.youtube.com/watch?v=fuag-KiPijQSIMULATION OF FIR FILTER BASED ON CORDIC ALGORITHM

SIMULATION OF FIR FILTER BASED ON CORDIC ALGORITHMVLSICS Design

╠²

Coordinate Rotation Digital Computer (CORDIC) discovered by Jack E Volder. It is a shift-add operation and iterative algorithm. CORDIC algorithm has wide area for several applications like digital signal processing, biomedical processing, image processing, radar signal processing, 8087 math coprocessor, the HP-35 calculator, Discrete Fourier, Discrete Hartley and Chirp-Z transforms, filtering, robotics, real time navigational system and also in communication systems. In this paper, we discussed about the CORDIC algorithm and CORDIC algorithm based finite impulse response low pass & high pass filter. We have generated the M-code for the CORDIC Algorithm and CORDIC Algorithm based FIR filter with the help of MATLAB 2010a.We also discussed about the frequency response characteristics of FIR filter.

NFPA 70B & 70E Changes and Additions Webinar Presented By Fluke

NFPA 70B & 70E Changes and Additions Webinar Presented By FlukeTranscat

╠²

Join us for this webinar about NFPA 70B & 70E changes and additions. NFPA 70B and NFPA 70E are both essential standards from the National Fire Protection Association (NFPA) that focus on electrical safety in the workplace. Both standards are critical for protecting workers, reducing the risk of electrical accidents, and ensuring compliance with safety regulations in industrial and commercial environments.

Fluke Sales Applications Manager Curt Geeting is presenting on this engaging topic:

Curt has worked for Fluke for 24 years. He currently is the Senior Sales Engineer in the NYC & Philadelphia Metro Markets. In total, Curt has worked 40 years in the industry consisting of 14 years in Test Equipment Distribution, 4+ years in Mfg. Representation, NAED Accreditation, Level 1 Thermographer, Level 1 Vibration Specialist, and Power Quality SME.Optimize AI Latency & Response Time with LLumo

Optimize AI Latency & Response Time with LLumosgupta86

╠²

Long response times kill user experience. We provide real-time monitoring and optimizations to ensure fast, seamless interactions.Analysis of Daylighting in Interior Spaces using the Daylight Factor - A Manu...

Analysis of Daylighting in Interior Spaces using the Daylight Factor - A Manu...Ignacio J. J. Palma Carazo

╠²

Daylighting manual method based on Daylight Factor for indoor spaces, previous to any computational simulation method.Privilege Escalation Techniques and methodology.pdf

Privilege Escalation Techniques and methodology.pdfharshvikramshahi2

╠²

Consolidated 40 different ways to escalate privilege Telehealth technology ŌĆō A new horizon in health care

Telehealth technology ŌĆō A new horizon in health careDr INBAMALAR T M

╠²

Telehealth technology ŌĆō A new horizon in health care, Telemedicine, E-healthLA2-64 -bit assemby language program to count number of positive and negative...

LA2-64 -bit assemby language program to count number of positive and negative...VidyaAshokNemade

╠²

This is one of lab experiment for Microprocessor NBA Criteria TIER I and TIER II Comparison

NBA Criteria TIER I and TIER II ComparisonDr INBAMALAR T M

╠²

Document Preparation for NBA

Self Assessment Report (SAR) Tier I Formats

"Introduction to VLSI Design: Concepts and Applications"

"Introduction to VLSI Design: Concepts and Applications"GtxDriver

╠²

This document offers a detailed exploration of VLSI (Very Large-Scale Integration) design principles, techniques, and applications. Topics include transistor-level design, digital circuit integration, and optimization strategies for modern electronics. Ideal for students, researchers, and professionals seeking a comprehensive guide to VLSI technology.UHV UNIT-5 IMPLICATIONS OF THE ABOVE HOLISTIC UNDERSTANDING OF HARMONY ON ...

UHV UNIT-5 IMPLICATIONS OF THE ABOVE HOLISTIC UNDERSTANDING OF HARMONY ON ...ariomthermal2031

╠²

IMPLICATIONS OF THE ABOVE HOLISTIC UNDERSTANDING OF HARMONY ON PROFESSIONAL ETHICS Analysis of Daylighting in Interior Spaces using the Daylight Factor - A Manu...

Analysis of Daylighting in Interior Spaces using the Daylight Factor - A Manu...Ignacio J. J. Palma Carazo

╠²

Intel 8259 - Programmable Interrupt Controller

- 2. Programmable Interrupt Controller (PIC) ’üĄ 8259 is a programmable interrupt controller. ’üĄ used to expand the interrupts of 8085. ’üĄ One 8259 can accept 8 interrupt requests and allow one by one to processor INTR pin. ’üĄ can be used in cascaded mode to expand the interrupt up to 64.

- 3. Features of 8259 ’üĄ programmed to work with 8085 & 8086. ’üĄ it manages 8 interrupts according to the instructions written into its control registers. ’üĄ the priorities of interrupts are programmable. ’üĄ 8259 can be programmed to accept either level triggered or edge triggered ’üĄ The interrupts can be masked or unmasked individually. ’üĄ The 8259s can be cascaded to accept a maximum of 64 interrupts.

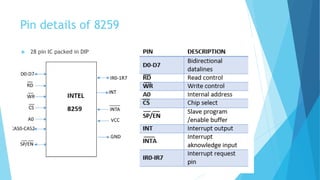

- 4. Pin details of 8259 ’üĄ 28 pin IC packed in DIP

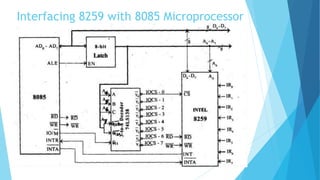

- 5. Interfacing 8259 with 8085 Microprocessor

- 6. ’üĄ It requires two internal address and they are A =0 or A = 1. ’üĄ It can be either memory mapped or I/O mapped in the system. The interfacing of 8259 to 8085 is shown in figure is I/O mapped in the system. ’üĄ The low order data bus lines D0-D7 are connected to D0-D7 of 8259. ’üĄ The address line A0 of the 8085 processor is connected to A0 of 8259 to provide the internal address.

- 7. ’üĄ The 8259 require one chip select signal. Using 3-to-8 decoder generates the chip select signal for 8259. ’üĄ The address lines A4, A5 and A6 are used as input to decoder. ’üĄ The control signal IO/M (low) is used as logic high enables for decoder and the address line A7 is used as logic low enable for decoder. ’üĄ The I/O addresses of 8259 are shown in table.

- 8. Working of 8259 with 8085 Microprocessor ’üĄ First the 8259 should be programmed by sending Initialization Command Word (ICW) and Operational Command Word (OCW). ’üĄ These command words will inform 8259 about the following: ’üĄ Type of interrupt signal (Level triggered / Edge triggered). ’üĄ Type of processor (8085/8086). ’üĄ Call address and its interval (4 or 8). ’üĄ Masking of interrupts. ’üĄ Priority of interrupts. ’üĄ Type of end of interrupts. ’üĄ Once 8259 is programmed it is ready for accepting interrupt signal. When it receives an interrupt through any one of the interrupt lines IR0-IR7 it checks for its priority and also checks whether it is masked or not.

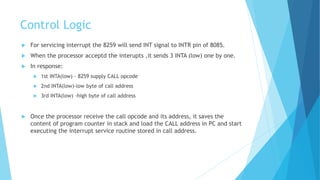

- 9. ’üĄ If the previous interrupt is completed and if the current request has highest priority and unmasked, then it is serviced. ’üĄ For servicing this interrupt the 8259 will send INT signal to INTR pin of 8085. ’üĄ In response it expects an acknowledge INTA (low) from the processor. ’üĄ When the processor accepts the interrupt, it sends three INTA (low) one by one. ’üĄ In response to first, second and third INTA (low) signals, the 8259 will supply CALL opcode, low byte of call address and high byte of call address respectively. Once the processor receives the call opcode and its address, it saves the content of program counter (PC) in stack and load the CALL address in PC and start executing the interrupt service routine stored in this call address.

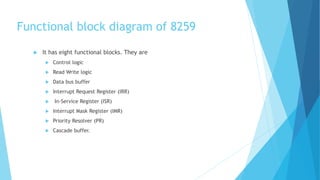

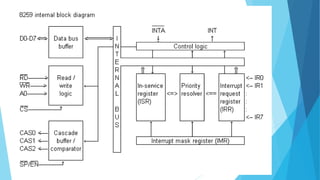

- 10. Functional block diagram of 8259 ’üĄ It has eight functional blocks. They are ’üĄ Control logic ’üĄ Read Write logic ’üĄ Data bus buffer ’üĄ Interrupt Request Register (IRR) ’üĄ In-Service Register (ISR) ’üĄ Interrupt Mask Register (IMR) ’üĄ Priority Resolver (PR) ’üĄ Cascade buffer.

- 12. Control Logic ’üĄ For servicing interrupt the 8259 will send INT signal to INTR pin of 8085. ’üĄ When the processor acceptd the interupts ,it sends 3 INTA (low) one by one. ’üĄ In response: ’üĄ 1st INTA(low) - 8259 supply CALL opcode ’üĄ 2nd INTA(low)-low byte of call address ’üĄ 3rd INTA(low) -high byte of call address ’üĄ Once the processor receive the call opcode and its address, it saves the content of program counter in stack and load the CALL address in PC and start executing the interrupt service routine stored in call address.

- 13. Read/Write/Logic ’üĄ The data bus and its buffer are used for the following activities. ’üĄ The processor sends control word to data bus buffer through D0-D7. ’üĄ The processor read status word from data bus buffer through D0-D7. ’üĄ From the data bus buffer the 8259 call opcode and address through D0-D7 to the processor. Data Bus Buffer ’üĄ The processor uses the RD (low), WR (low) and A0 to read or write 8259. ’üĄ The 8259 is selected by CS (low).

- 14. Interrupt Mask Register ’üĄ The IRR has eight input lines (IR0-IR7) for interrupts. When these lines go high, the request is stored in IRR. It registers a request only if the interrupt is unmasked. ’üĄ Normally IR0 has highest priority and IR7 has the lowest priority. The priorities of the interrupt request input are also programmable. Interrupt Request Register ’üĄ The interrupt mask register (IMR) stores the masking bits of the interrupt lines to be masked. The relevant information is send by the processor through OCW.

- 15. Priority Resolver ’üĄ The in-service register keeps track of which interrupt is currently being serviced. In-Service Register ’üĄ The priority resolver examines the interrupt request, mask and in- service registers and determines whether INT signal should be sent to the processor or not. Cascade Buffer/Comparator ’üĄ The cascade buffer/comparator is used to expand the interrupts of 8259.