12 LCD ADC - C·∫£m bi·∫øn

- 1. Ch­¬ng 12 Phèi ghÐp víi thÕ giíi thùc: LCD, ADC vµ c¸c c¶m biÕn Ch­¬ng nµy kh¸m ph¸ mét sè øng dông cña 8051 víi thÕ giíi thùc. Chóng ta gi¶i thÝch lµm c¸ch nµo phèi ghÐp 8051 víi c¸c thiÕt bÞ nh­ lµ LCD, ADC vµ c¸c c¶m biÕn. 12.1 Phèi ghÐp mét LCD víi 8051. ë phÇn nµy ta sÏ m« t¶ c¸c chÕ ®é ho¹t ®éng cña c¸c LCD vµ sau ®ã m« t¶ c¸ch lËp tr×nh vµ phèi ghÐp mét LCD tíi 8051. 12.1.1 Ho¹t ®éng cña LCD. Trong nh÷ng n¨m gÇn ®©y LCD ®ang ngµy cµng ®­îc sö dông réng r·i thay thÕ dÇn cho c¸c ®Ìn LED (c¸c ®Ìn LED 7 ®o¹n hay nhiÒu ®o¹n). §ã lµ v× c¸c nguyªn nh©n sau: 1. C¸c LCD cã gi¸ thµnh h¹. 2. Kh¶ n¨ng hiÓn thÞ c¸c sè, c¸c ký tù vµ ®å ho¹ tèt h¬n nhiÒu so víi c¸c ®Ìn LED (v× c¸c ®Ìn LED chØ hiÓn thÞ ®­îc c¸c sè vµ mét sè ký tù). 3. Nhê kÕt hîp mét bé ®iÒu khiÓn lµm t­¬i vµo LCD lµm gi¶i phãng cho CPU c«ng viÖc lµm t­¬i LCD. Trong khi ®Ìn LED ph¶i ®­îc lµm t­¬i b»ng CPU (hoÆc b»ng c¸ch nµo ®ã) ®Ó duy tr× viÖc hiÓn thÞ d÷ liÖu. 4. DÔ dµng lËp tr×nh cho c¸c ký tù vµ ®å ho¹. 12.1.2 M« t¶ c¸c ch©n cña LCD. LCD ®­îc nãi trong môc nµy cã 14 ch©n, chøc n¨ng cña c¸c ch©n ®­îc cho trong b¶ng 12.1. VÞ trÝ cña c¸c ch©n ®­îc m« t¶ trªn h×nh 12.1 cho nhiÒu LCD kh¸c nhau. 1. Ch©n VCC, VSS vµ VEE: C¸c ch©n VCC, VSS vµ VEE: CÊp d­¬ng nguån - 5v vµ ®Êt t­¬ng øng th× VEE ®­îc dïng ®Ó ®iÒu khiÓn ®é t­¬ng ph¶n cña LCD. 2. Ch©n chän thanh ghi RS (Register Select). Cã hai thanh ghi rÊt quan träng bªn trong LCD, ch©n RS ®­îc dïng ®Ó chän c¸c thanh ghi nµy nh­ sau: NÕu RS = 0 th× thanh ghi mµ lÖnh ®­îc chän ®Ó cho phÐp ng­êi dïng göi mét lÖnh ch¼ng h¹n nh­ xo¸ mµn h×nh, ®­a con trá vÒ ®Çu dßng v.v… NÕu RS = 1 th× thanh ghi d÷ liÖu ®­îc chän cho phÐp ng­êi dïng göi d÷ liÖu cÇn hiÓn thÞ trªn LCD. 3. Ch©n ®äc/ ghi (R/W). §Çu vµo ®äc/ ghi cho phÐp ng­êi dïng ghi th«ng tin lªn LCD khi R/W = 0 hoÆc ®äc th«ng tin tõ nã khi R/W = 1. 4. Ch©n cho phÐp E (Enable). Ch©n cho phÐp E ®­îc sö dông bëi LCD ®Ó chèt th«ng tin hiÖn h÷u trªn ch©n d÷ liÖu cña nã. Khi d÷ liÖu ®­îc cÊp ®Õn ch©n d÷ liÖu th× mét xung møc cao xuèng thÊp ph¶i ®­îc ¸p ®Õn ch©n nµy ®Ó LCD chèt d÷ liÖu trªn c¸c ch©n d÷ liªu. Xung nµy ph¶i réng tèi thiÓu lµ 450ns. 5. Ch©n D0 - D7. §©y lµ 8 ch©n d÷ liÖu 8 bÝt, ®­îc dïng ®Ó göi th«ng tin lªn LCD hoÆc ®äc néi dung cña c¸c thanh ghi trong LCD. §Ó hiÓn thÞ c¸c ch÷ c¸i vµ c¸c con sè, chóng ta göi c¸c m· ASCII cña c¸c ch÷ c¸i tõ A ®Õn Z, a ®Õn f vµ c¸c con sè tõ 0 - 9 ®Õn c¸c ch©n nµy khi bËt RS = 1.

- 2. Còng cã c¸c m· lÖnh mµ cã thÓ ®­îc göi ®Õn LCD ®Ó xo¸ mµn h×nh hoÆc ®­a con trá vÒ ®Çu dßng hoÆc nhÊp nh¸y con trá. B¶ng 12.2 liÖt kª c¸c m· lªnh. Chóng ta còng sö dông RS = 0 ®Ó kiÓm tra bÝt cê bËn ®Ó xem LCD cã s½n sµng nh©n th«ng tin. Cê bËn lµ D7 vµ cã thÓ ®­îc®äc khi R/W = 1 vµ RS = 0 nh­ sau: NÕu R/W = 1, RS = 0 khi D7 = 1 (cê bËn 1) th× LCD bËn bëi c¸c c«ng viÖc bªn trong vµ sÏ kh«ng nhËn bÊt kú th«ng tin míi nµo. Khi D7 = 0 th× LCD s½n sµng nhËn th«ng tin míi. L­u ý chóng ta nªn kiÓm tra cê bËn tr­íc khi ghi bÊt kú d÷ liÖu nµo lªn LCD. B¶ng 12.1: M« t¶ c¸c ch©n cña LCD. Ch©n Ký hiÖu I/O M« t¶ 1 VSS - §Êt 2 VCC - D­¬ng nguån 5v 3 VEE - CÊp nguån ®iÒu khiÓn ph¶n 4 RS I RS = 0 chän thanh ghi lÖnh. RS = 1 chän thanh d÷ liÖu 5 R/W I R/W = 1 ®äc d÷ liÖu. R/W = 0 ghi 6 E I/O Cho phÐp 7 DB0 I/O C¸c bÝt d÷ liÖu 8 DB1 I/O C¸c bÝt d÷ liÖu 9 DB2 I/O C¸c bÝt d÷ liÖu 10 DB3 I/O C¸c bÝt d÷ liÖu 11 DB4 I/O C¸c bÝt d÷ liÖu 12 DB5 I/O C¸c bÝt d÷ liÖu 13 DB6 I/O C¸c bÝt d÷ liÖu 14 DB7 I/O C¸c bÝt d÷ liÖu B¶ng 12.2: C¸c m· lÖnh LCD. M· (Hex) LÖnh ®Õn thanh ghi cña LCD 1 Xo¸ mµn h×nh hiÓn thÞ 2 Trë vÒ ®Çu dßng 4 Gi¶ con trá (dÞch con trá sang tr¸i) 6 T¨ng con trá (dÞch con trá sang ph¶i) 5 DÞch hiÓn thÞ sang ph¶i 7 DÞch hiÓn thÞ sang tr¸i 8 T¾t con trá, t¾t hiÓn thÞ A T¾t hiÓn thÞ, bËt con trá C BËt hiÓn thÞ, t¾t con trá E BËt hiÓn thÞ, nhÊp nh¸y con trá F T¾t con trá, nhÊp nh¸y con trá 10 DÞch vÞ trÝ con trá sang tr¸i 14 DÞch vÞ trÝ con trá sang ph¶i 18 DÞch toµn bé hiÓn thÞ sang tr¸i

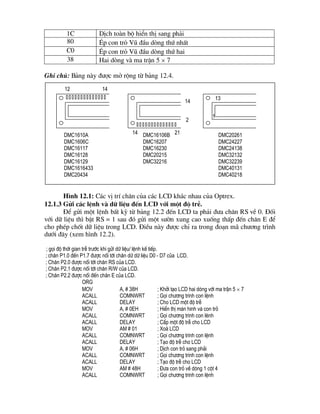

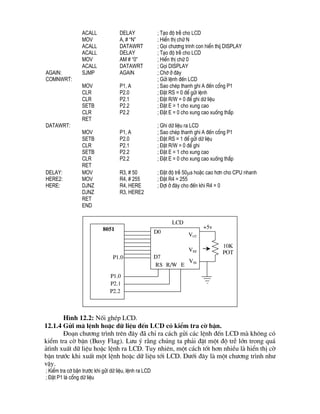

- 3. 1C DÞch toµn bé hiÓn thÞ sang ph¶i 80 Ðp con trá Vò ®Çu dßng thø nhÊt C0 Ðp con trá Vò ®Çu dßng thø hai 38 Hai dßng vµ ma trËn 5 ´ 7 Ghi chó: B¶ng nµy ®­îc më réng tõ b¶ng 12.4. H×nh 12.1: C¸c vÞ trÝ ch©n cña c¸c LCD kh¸c nhau cña Optrex. 12.1.3 Göi c¸c lÖnh vµ d÷ liÖu ®Õn LCD víi mét ®é trÔ. §Ó göi mét lÖnh bÊt kú tõ b¶ng 12.2 ®Õn LCD ta ph¶i ®­a ch©n RS vÒ 0. §èi víi d÷ liÖu th× bËt RS = 1 sau ®ã göi mét s­ên xung cao xuèng thÊp ®Õn ch©n E ®Ó cho phÐp chèt d÷ liÖu trong LCD. §iÒu nµy ®­îc chØ ra trong ®o¹n m· ch­¬ng tr×nh d­íi ®©y (xem h×nh 12.2). ; gäi ®é thêi gian trÔ tr­íc khi göi d÷ liÖu/ lÖnh kÕ tiÕp. ; ch©n P1.0 ®Õn P1.7 ®­îc nèi tíi ch©n d÷ d÷ liÖu D0 - D7 cña LCD. ; Ch©n P2.0 ®­îc nèi tíi ch©n RS cña LCD. ; Ch©n P2.1 ®­îc nèi tíi ch©n R/W cña LCD. ; Ch©n P2.2 ®­îc nèi ®Õn ch©n E cña LCD. ORG MOV A, # 38H ; Khëi t¹o LCD hai dßng víi ma trËn 5 ´ 7 ACALL COMNWRT ; Gäi ch­¬ng tr×nh con lÖnh ACALL DELAY ; Cho LCD mét ®é trÔ MOV A, # 0EH ; HiÓn thÞ mµn h×nh vµ con trá ACALL COMNWRT ; Gäi ch­¬ng tr×nh con lªnh ACALL DELAY ; CÊp mét ®é trÔ cho LCD MOV AM # 01 ; Xo¸ LCD ACALL COMNWRT ; Gäi ch­¬ng tr×nh con lÖnh ACALL DELAY ; T¹o ®é trÔ cho LCD MOV A, # 06H ; DÞch con trá sang ph¶i ACALL COMNWRT ; Gäi ch­¬ng tr×nh con lÖnh ACALL DELAY ; T¹o ®é trÔ cho LCD MOV AM # 48H ; §­a con trá vÒ dßng 1 cét 4 ACALL COMNWRT ; Gäi ch­¬ng tr×nh con lÖnh 12 14 14 13 2 1 14 21 DMC20261 DMC24227 DMC24138 DMC32132 DMC32239 DMC40131 DMC40218 DMC1610A DMC1606C DMC16117 DMC16128 DMC16129 DMC1616433 DMC20434 DMC16106B DMC16207 DMC16230 DMC20215 DMC32216

- 4. ACALL DELAY ; T¹o ®é trÔ cho LCD MOV A, # “N” ; HiÓn thÞ ch÷ N ACALL DATAWRT ; Gäi ch­¬ng tr×nh con hiÓn thij DISPLAY ACALL DELAY ; T¹o ®é trÔ cho LCD MOV AM # “0” ; HiÓn thÞ ch÷ 0 ACALL DATAWRT ; Gäi DISPLAY AGAIN: SJMP AGAIN ; Chê ë ®©y COMNWRT: ; Göi lÖnh ®Õn LCD MOV P1, A ; Sao chÐp thanh ghi A ®Õn cæng P1 CLR P2.0 ; §Æt RS = 0 ®Ó göi lÖnh CLR P2.1 ; §Æt R/W = 0 ®Ó ghi d÷ liÖu SETB P2.2 ; §Æt E = 1 cho xung cao CLR P2.2 ; §Æt E = 0 cho xung cao xuèng thÊp RET DATAWRT: ; Ghi d÷ liÖu ra LCD MOV P1, A ; Sao chÐp thanh ghi A ®Õn cæng P1 SETB P2.0 ; §Æt RS = 1 ®Ó göi d÷ liÖu CLR P2.1 ; §Æt R/W = 0 ®Ó ghi SETB P2.2 ; §Æt E = 1 cho xung cao CLR P2.2 ; §Æt E = 0 cho xung cao xuèng thÊp RET DELAY: MOV R3, # 50 ; §Æt ®é trÔ 50ms hoÆc cao h¬n cho CPU nhanh HERE2: MOV R4, # 255 ; §Æt R4 = 255 HERE: DJNZ R4, HERE ; §îi ë ®©y cho ®Õn khi R4 = 0 DJNZ R3, HERE2 RET END H×nh 12.2: Nèi ghÐp LCD. 12.1.4 Göi m· lÖnh hoÆc d÷ liÖu ®Õn LCD cã kiÓm tra cê bËn. §o¹n ch­¬ng tr×nh trªn ®©y ®· chØ ra c¸ch göi c¸c lÖnh ®Õn LCD mµ kh«ng cã kiÓm tra cê bËn (Busy Flag). L­u ý r»ng chóng ta ph¶i ®Æt mét ®é trÔ lín trong qu¸ ¶t×nh xuÊt d÷ liÖu hoÆc lÖnh ra LCD. Tuy nhiªn, mét c¸ch tèt h¬n nhiÒu lµ hiÓn thÞ cê bËn tr­íc khi xuÊt mét lÖnh hoÆc d÷ liÖu tíi LCD. D­íi ®©y lµ mét ch­¬ng tr×nh nh­ vËy. ; KiÓm tra cê bËn tr­íc khi göi d÷ liÖu, lÖnh ra LCD ; §Æt P1 lµ cæng d÷ liÖu P2.1 D0 P1.0 P1.0 P2.2 D7 R/W ERS VSS VEE VCC +5v 10K POT LCD 8051

- 5. ; §Æt P2.0 nèi tíi cæng RS ; §Æt P2.1 nèi tíi ch©n R/W ; §Æt P2.2 nèi tíi ch©n E ORG MOV A, # 38H ; Khëi t¹o LCD hai dßng víi ma trËn 5 ´ 7 ACALL COMMAND ; XuÊt lÖnh MOV A, # 0EH ; DÞch con trá sang ph¶i ACALL COMMAND ; XuÊt lÖnh MOV A, # 01H ; Xo¸ lÖnh LCD ACALL COMMAND ; XuÊt lÖnh MOV A, # 86H ; DÞch con trá sang ph¶i ACALL COMMAND ; §­a con trá vÒ dßng 1 lÖnh 6 MOV A, # “N” ; HiÓn thÞ ch÷ N ACALL DATA DISPLAY MOV A, # “0” ; HiÓn thÞ ch÷ 0 ACALL DATA DISPLAY HERE: SJMP HERE ; Chê ë ®©y COMMAND: ACALL READY ; LCD ®· s½n sµng ch­a? MOV P1, A ; XuÊt m· lÖnh CLR P2.0 ; §Æt RS = 0 cho xuÊt lÖnh CLR P2.1 ; §Æt R/W = 0 ®Ó ghi d÷ liÖu tíi LCD SETB P2.2 ; §Æt E = 1 ®èi víi xung cao xuèng thÊp CLR P2.2 ; §Æt E = 0 chèt d÷ liÖu RET DATA-DISPLAY:: ACALL READY ; LCD ®· s½n sµng ch­a? MOV P1, A ; XuÊt d÷ liÖu SETB P2.0 ; §Æt RS = 1 cho xuÊt d÷ liÖu CLR P2.1 ; §Æt R/W = 0 ®Ó ghi d÷ liÖu ra LCD SETB P2.2 ; §Æt E = 1 ®èi víi xung cao xuèng thÊp CLR P2.2 ; §Æt E = 0 chèt d÷ liÖu RET DELAY: SETB P1.7 ; LÊy P1.7 lµm cæng vµo CLR P2.0 ; §Æt RS = 0 ®Ó truy cËp thanh ghi lÖnh SETB P2.1 ; §Æt R/W = 1 ®äc thanh ghi lÖnh ; §äc thanh ghi lÖnh vµ kiÓm tra cê lÖnh BACK: CLR P2.2 ; E = 1 ®èi víi xung cao xuèng thÊp SETB P2.2 ; E = 0 cho xung cao xuèng thÊp? JB P1.7, BACK ; §îi ë ®©y cho ®Õn khi cê bËn = 0 RET END L­u ý r»ng trong ch­¬ng tr×nh cê bËn D7 cña thanh ghi lÖnh. §Ó ®äc thanh ghi lÖnh ta ph¶i ®Æt RS = 0, R/W = 1 vµ xung cao - xuèng - thÊp cho bÝt E ®Ó cÊp thanh ghi lÖnh cho chóng ta. Sau khi ®äc thanh ghi lÖnh, nÕu bÝt D7 (cê bËn) ë møc cao th× LCD bËn vµ kh«ng cã th«ng tin (lÖnh) nµo ®­îc xuÊt ®Õn nã chØ khi nµo D7 = 0 míi cã thÓ göi d÷ liÖu hoÆc lÖnh ®Õn LCD. L­u ý trong ph­¬ng ph¸t nµy kh«ng sö dông ®é trÔ thêi gian nµo v× ta ®ang kiÓm tra cê bËn tr­íc khi xuÊt lÖnh hoÆc d÷ liÖu lªn LCD. 12.1.5 B¶ng d÷ liÖu cña LCD. Trong LCD ta cã thÓ ®Æt d÷ liÖu vµo bÊt cø chç nµo. d­íi ®©y lµ c¸c vÞ trÝ ®Þa chØ vµ c¸ch chóng ®­îc truy cËp.

- 6. RS E/W DB7 DB6 DB5 DB4 DB3 DB2 DB1 DB0 0 0 1 A A A A A A A Khi AAAAAAA = 0000000 ®Õn 0100111 cho dßng lÖnh 1 vµ AAAAAAA = 1100111 cho dßng lÖnh2. Xem b¶ng 12.3. B¶ng 12.3: §¸nh ®Þa chØ cho LCD. DB7 DB6 DB5 DB4 DB3 DB2 DB1 DB0 Dßng 1 (min) 1 0 0 0 0 0 0 0 Dßng 1 (max) 1 0 1 0 0 1 1 1 Dßng 2 (min) 1 1 0 0 0 0 0 0 Dßng 2 (max) 1 1 1 0 0 1 1 1 D¶i ®Þa chØ cao cã thÓ lµ 0100111 cho LCD. 40 ký tù trong khi ®èi víi CLD 20 ký tù chØ ®Õn 010011 (19 thËp ph©n = 10011 nhÞ ph©n). §Ó ý r»ng d¶i trªn 0100111 (nhÞ ph©n) = 39 thËp ph©n øng víi vÞ trÝ 0 ®Õn 39 cho LCD kÝch th­íc 40 ´ 2. Tõ nh÷ng ®iÒu nãi ë trªn ®©y ta cã thÓ nhËn ®­îc c¸c ®Þa chØ cña vÞ trÝ con trá cã c¸c kÝch th­íc LCD kh¸c nhau. Xem h×nh 12.3 chó ý r»ng tÊt c¶ mäi ®Þa chØ ®Òu ë d¹ng sè Hex. H×nh 12.4 cho mét biÓu ®å cña viÖc ph©n thêi gian cña LCD. B¶ng 12.4 lµ danh s¸ch liÖt kª chi tiÕt c¸c lÖnh vµ chØ lÖnh cña LCD. B¶ng 12.2 ®­îc më réng tõ b¶ng nµy. 16 ´ 2 LCD 80 C0 81 C0 82 C2 83 C3 84 C4 85 C5 86 C6 Through Through 8F CF 20 ´ 1 LCD 80 81 82 83 Through 93 20 ´ 2 LCD 80 C0 81 C0 82 C2 83 C3 Through 93 Through D3 20 ´ 4 LCD 80 C0 94 D4 81 C0 95 D5 82 C2 96 D6 83 C3 97 D7 Through 93 Through D3 Through A7 Through E7 20 ´ 2 LCD 80 C0 81 C0 82 C2 83 C3 Through A7 Through E7 Note: All data is in hex. H×nh 12.3: C¸c ®Þa chØ con trá ®èi víi mét sè LCD.

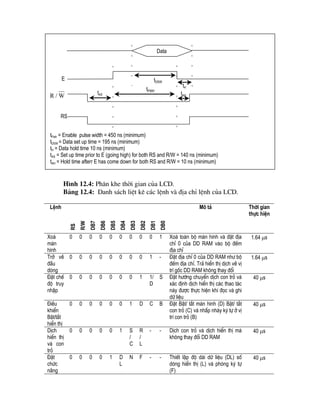

- 7. H×nh 12.4: Ph©n khe thêi gian cña LCD. B¶ng 12.4: Danh s¸ch liÖt kª c¸c lÖnh vµ ®Þa chØ lÖnh cña LCD. LÖnh RS R/W DB7 DB6 DB5 DB4 DB3 DB2 DB1 DB0 M« t¶ Thêi gian thùc hiÖn Xo¸ mµn h×nh 0 0 0 0 0 0 0 0 0 1 Xo¸ toµn bé mµn h×nh vµ ®Æt ®Þa chØ 0 cña DD RAM vµo bé ®Õm ®Þa chØ 1.64 ms Trë vÒ ®Çu dßng 0 0 0 0 0 0 0 0 1 - §Æt ®Þa chØ 0 cña DD RAM nh­ bé ®Õm ®Þa chØ. Tr¶ hiÓn thÞ dÞch vÒ vÞ trÝ gèc DD RAM kh«ng thay ®æi 1.64 ms §Æt chÕ ®é truy nhËp 0 0 0 0 0 0 0 1 1/ D S §Æt h­íng chuyÓn dÞch con trá vµ x¸c ®Þnh dÞch hiÓn thÞ c¸c thao t¸c nµy ®­îc thùc hiÖn khi ®äc vµ ghi d÷ liÖu 40 ms §iÒu khiÓn BËt/t¾t hiÓn thÞ 0 0 0 0 0 0 1 D C B §Æt BËt/ t¾t mµn h×nh (D) BËt/ t¾t con trá (C) vµ nhÊp nh¸y ký tù ë vÞ trÝ con trá (B) 40 ms DÞch hiÓn thÞ vµ con trá 0 0 0 0 0 1 S / C R / L - - DÞch con trá vµ dÞch hiÓn thÞ mµ kh«ng thay ®æi DD RAM 40 ms §Æt chøc n¨ng 0 0 0 0 1 D L N F - - ThiÕt lËp ®é dµi d÷ liÖu (DL) sè dßng hiÓn thÞ (L) vµ phßng ký tù (F) 40 ms tPwh = Enable pulse width = 450 ns (minimum) tDSW = Data set up time = 195 ns (minimum) tH = Data hold time 10 ns (minimum) tAS = Set up time prior to E (going high) for both RS and R/W = 140 ns (minimum) tAH = Hold time afterr E has come down for both RS and R/W = 10 ns (minimum) Data tDSW tPWH tH tAHW/R E RS tAS

- 8. §Æt ®Þa chØ CGRA M 0 0 0 1 AGC ThiÕt lËp ®Þa chØ C6 RAM d÷ liÖu CG RAM ®­îc göi ®i vµ nhËn sau thiÕt lËp nµy 40 ms ThiÕt lËp ®Þa chØ DD RAM 0 0 1 ADD ThiÕt lËp ®Þa chØ DD RAM d÷ liÖu DD RAM ®­îc göi vµ nhËn sau thiÕt lËp nµy 40 ms Cê bËn ®äc vµ ®Þa chØ 0 1 BF ADD Cê bËn ®äc (BF) b¸o ho¹t ®éng bªn trong ®ang ®­îc thùc hiÖn vµ ®äc néi dung bé ®Õm ®Þa chØ 40 ms Ghi d÷ liÖu CG hoÆc DD RAM 1 0 Ghi d÷ liÖu Ghi d÷ liÖu vµo DD RAM hoÆc CG RAM 40 ms §äc d÷ liÖu CG hoÆc DD RAM 1 1 §äc d÷ liÖu §äc d÷ liÖu tõ DD RAM hoÆc CG RAM 40 ms Ghi chó: 1. Thêi gian thùc lµ thêi gian cùc ®¹i khi tÇn sè fCP hoÆc fosc lµ 250KHz 2. Thêi gian thùc thay ®æi khi tÇn sè thay ®æi. Khi tÇn sè fEP hay fosc Lµ 270kHz th× thêi gian thùc hiÖn ®­îc tÝnh 250/270 ´ 40 = 35ms v.v… 3. C¸c ký hiÖu viÕt t¾t trong b¶ng lµ: 4. DD RAM RAM d÷ liÖu hiÓn thÞ (Display Data RAM) CG RAM RAM m¸y ph¸t ký tù (character Generator) ACC §Þa chØa cña RAM m¸y ph¸t ký tù ADD §Þa chØ cña RAM d÷ liÖu hiÓn thÞ phï hîp víi ®Þa chØ con trá. AC Bé ®Õm ®Þa chØ (Address Counter) ®­îc dïng cho c¸c ®Þa chØ DD RAM vµ CG RAM. 1/D = 1 T¨ng 1/D = 0 Gi¶m S = 1 KÌm dÞch hiÓn thÞ S/C = 1 DÞch hiÓn thÞ S/C = 0 DÞch con trá R/L = 1 DÞch sang ph¶i R/L = 0 DÞch tr¸i DL = 1 8 bÝt DL = 0 4 bÝt N = 1 2 dßng N = 1 1 dßng F = 1 Ma trËn ®iÓm 5 ´ 10 F = 0 Ma trËn ®iÓm 5 ´ 7 BF = 1 BËn BF = 0 Cã thÓ nhËn lªnh 12.2 Phèi ghÐp 8051 víi ADC vµ c¸c c¶m biÕn. PhÇn nµy sÏ kh¸m ph¸ ghÐp c¸c chÝp ADC (bé chuyÓn ®æi t­¬ng tù sè) vµ c¸c c¶m biÕn nhiÖt víi 8051. 12.1.1 C¸c thiÕt bÞ ADC. C¸c bé chuyÓn ®æi ADC thuéc trong nh÷ng thiÕt bÞ ®­îc sö dông réng r·i nhÊt ®Ó thu d÷ liÖu. C¸c m¸y tÝnh sè sö dông c¸c gi¸ trÞ nhÞ ph©n, nh­ng trong thÕ giíi vËt lý th× mäi ®¹i l­îng ë d¹ng t­¬ng tù (liªn tôc). NhiÖt ®é, ¸p suÊt (khÝ hoÆc

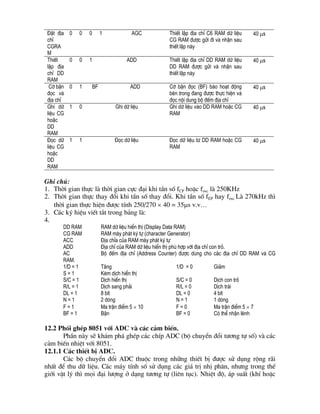

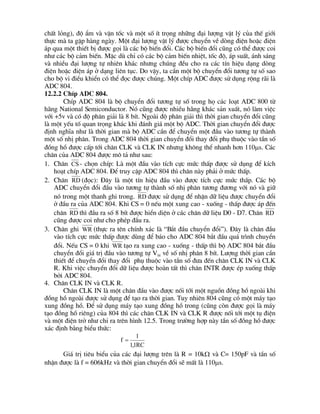

- 9. chÊt láng), ®é Èm vµ vËn tèc vµ mét sè Ýt träng nh÷ng ®¹i l­îng vËt lý cña thÕ giíi thùc mµ ta gÆp hµng ngµy. Mét ®¹i l­îng vËt lý ®­îc chuyÓn vÒ dßng ®iÖn hoÆc ®iÖn ¸p qua mét thiÕt bÞ ®­îc gäi lµ c¸c bé biÕn ®æi. C¸c bé biÕn ®æi còng cã thÓ ®­îc coi nh­ c¸c bé c¶m biÕn. MÆc dï chØ cã c¸c bé c¶m biÕn nhiÖt, tèc ®é, ¸p suÊt, ¸nh s¸ng vµ nhiÒu ®¹i l­îng tù nhiªn kh¸c nh­ng chóng ®Òu cho ra c¸c tÝn hiÖu d¹ng dßng ®iÖn hoÆc ®iÖn ¸p ë d¹ng liªn tôc. Do vËy, ta cÇn mét bé chuyÓn ®æi t­¬ng tù sè sao cho bé vi ®iÒu khiÓn cã thÓ ®äc ®­îc chóng. Mét chÝp ADC ®­îc sö dông réng r·i lµ ADC 804. 12.2.2 ChÝp ADC 804. ChÝp ADC 804 lµ bé chuyÓn ®æi t­¬ng tù sè trong hä c¸c lo¹t ADC 800 tõ h·ng National Semiconductor. Nã còng ®­îc nhiÒu h·ng kh¸c s¶n xuÊt, nã lµm viÖc víi +5v vµ cã ®é ph©n gi¶i lµ 8 bÝt. Ngoµi ®é ph©n gi¶i th× thêi gian chuyÓn ®æi còng lµ mét yÕu tè quan träng kh¸c khi ®¸nh gi¸ mét bé ADC. Thêi gian chuyÓn ®æi ®­îc ®Þnh nghÜa nh­ lµ thêi gian mµ bé ADC cÇn ®Ó chuyÓn mét ®Çu vµo t­¬ng tù thµnh mét sè nhÞ ph©n. Trong ADC 804 thêi gian chuyÓn ®æi thay ®æi phô thuéc vµo tÇn sè ®ång hå ®­îc cÊp tíi ch©n CLK vµ CLK IN nh­ng kh«ng thÓ nhanh h¬n 110ms. C¸c ch©n cña ADC 804 ®­îc m« t¶ nh­ sau: 1. Ch©n CS- chän chÝp: Lµ mét ®Çu vµo tÝch cùc møc thÊp ®­îc sö dông ®Ó kÝch ho¹t chÝp ADC 804. §Ó truy cËp ADC 804 th× ch©n nµy ph¶i ë møc thÊp. 2. Ch©n RD (®äc): §©y lµ mét tÝn hiÖu ®Çu vµo ®­îc tÝch cùc møc thÊp. C¸c bé ADC chuyÓn ®æi ®Çu vµo t­¬ng tù thµnh sè nhÞ ph©n t­¬ng ®­¬ng víi nã vµ gi÷ nã trong mét thanh ghi trong. RD ®­îc sö dông ®Ó nhËn d÷ liÖu ®­îc chuyÓn ®æi ë ®Çu ra cña ADC 804. Khi CS = 0 nÕu mét xung cao - xuèng - thÊp ®­îc ¸p ®Õn ch©n RD th× ®Çu ra sè 8 bÝt ®­îc hiÓn diÖn ë c¸c ch©n d÷ liÖu D0 - D7. Ch©n RD còng ®­îc coi nh­ cho phÐp ®Çu ra. 3. Ch©n ghi WR (thùc ra tªn chÝnh x¸c lµ “B¾t ®Çu chuyÓn ®æi”). §©y lµ ch©n ®Çu vµo tÝch cùc møc thÊp ®­îc dïng ®Ó b¸o cho ADC 804 b¾t ®Çu qu¸ tr×nh chuyÓn ®æi. NÕu CS = 0 khi WR t¹o ra xung cao - xuèng - thÊp th× bé ADC 804 b¾t ®Çu chuyÓn ®æi gi¸ trÞ ®Çu vµo t­¬ng tù Vin vÒ sè nhÞ ph©n 8 bÝt. L­îng thêi gian cÇn thiÕt ®Ó chuyÓn ®æi thay ®æi phô thuéc vµo tÇn sè ®­a ®Õn ch©n CLK IN vµ CLK R. Khi viÖc chuyÓn ®æi d÷ liÖu ®­îc hoµn tÊt th× ch©n INTR ®­îc Ðp xuèng thÊp bëi ADC 804. 4. Ch©n CLK IN vµ CLK R. Ch©n CLK IN lµ mét ch©n ®Çu vµo ®­îc nèi tíi mét nguån ®ång hå ngoµi khi ®ång hå ngoµi ®­îc sö dông ®Ó t¹o ra thêi gian. Tuy nhiªn 804 còng cã mét m¸y t¹o xung ®ång hå. §Ó sö dông m¸y t¹o xung ®ång hå trong (còng cßn ®­îc gäi lµ m¸y t¹o ®ång hå riªng) cña 804 th× c¸c ch©n CLK IN vµ CLK R ®­îc nèi tíi mét tô ®iÖn vµ mét ®iÖn trë nh­ chØ ra trªn h×nh 12.5. Trong tr­êng hîp nµy tÇn sè ®ång hå ®­îc x¸c ®Þnh b»ng biÓu thøc: RC1,1 1 f = gi¸ trÞ tiªu biÓu cña c¸c ®¹i l­îng trªn lµ R = 10kW vµ C= 150pF vµ tÇn sè nhËn ®­îc lµ f = 606kHz vµ thêi gian chuyÓn ®æi sÏ mÊt lµ 110ms.

- 10. H×nh 12.5: KiÓm tra ADC 804 ë chÕ ®é ch¹y tù do. 5. Ch©n ng¾t INTR (ng¾t hay gäi chÝnh x¸c h¬n lµ “kÕt thóc chuyÓn ®æi’). §©y lµ ch©n ®Çu ra tÝch cùc møc thÊp. B×nh th­êng nã ë tr¹ng th¸i cao vµ khi viÖc chuyÓn ®æi hoµn tÊt th× nã xuèng thÊp ®Ó b¸o cho CPU biÕt lµ d÷ liÖu ®­îc chuyÓn ®æi s½n sµng ®Ó lÊy ®i. Sau khi INTR xuèng thÊp, ta ®Æt CS = 0 vµ göi mét xung cao 0 xuèng - thÊp tíi ch©n RD lÊy d÷ liÖu ra cña 804. 6. Ch©n Vin (+) vµ Vin (-). §©y lµ c¸c ®Çu vµo t­¬ng tù vi sai mµ Vin = Vin (+) - Vin (-). Th«ng th­êng Vin (-) ®­îc nèi xuèng ®Êt vµ Vin (+) ®­îc dïng nh­ ®Çu vµo t­¬ng tù ®­îc chuyÓn ®æi vÒ d¹ng sè. 7. Ch©n VCC. §©y lµ ch©n nguån nuèi +5v, nã còng ®­îc dïng nh­ ®iÖn ¸p tham chiÕu khi ®Çu vµo Vref/2 (ch©n 9) ®Ó hë. 8. Ch©n Vref/2. Ch©n 9 lµ mét ®iÖn ¸p ®Çu vµo ®­îc dïng cho ®iÖn ¸p tham chiÕu. NÕu ch©n nµy hë (kh«ng ®­îc nèi) th× ®iÖn ¸p ®Çu vµo t­¬ng tù cho ADC 804 n»m trong d¶i 0 ®Õn +5v (gièng nh­ ch©n VCC). Tuy nhiªn, cã nhiÒu øng dông mµ ®Çu vµo t­¬ng tù ¸p ®Õn Vin cÇn ph¶i kh¸c ngoµi d¶i 0 ®Õn 5v. Ch©n Vref/2 ®­îcdïng ®Ó thùc thi c¸c ®iÖn ¸p ®Çu vµo kh¸c ngoµi d¶i 0 - 5v. VÝ dô, nÕu d¶i ®Çu vµo t­¬ng tù cÇn ph¶i lµ 0 ®Õn 4v th× Vref/2 ®­îc nèi víi +2v. B¶ng 12.5 biÓu diÔn d¶i ®iÖn ¸p Vin ®èi víi c¸c ®Çu vµo Vref/2 kh¸c nhau. B¶ng 12.5: §iÖn ¸p Vref/2 liªn hÖ víi d¶i Vin. ADC0804 +5V 1 1 1 4 1 2 10 9 19 10k 150pF 11 12 13 14 15 16 17 18 3 5 to LEDs Nomally Open START D0 D1 D2 D3 D4 D5 D6 D7 WR INTRD GND RD CS CLK in CLK R A GND Vref/2 Vin(-) Vin(+) 20 Vcc 10k POT

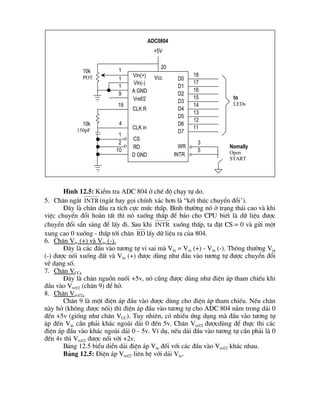

- 11. Vref/ 2(V) Vin(V) Step Size (mV) Hë * 0 ®Õn 5 5/256 = 19.53 2.0 0 ®Õn 4 4/255 = 15.62 1.5 0 ®Õn 3 3/256 = 11.71 1.28 0 ®Õn 2.56 2.56/256 = 10 1.0 0 ®Õn 2 2/256 = 7.81 0.5 0 ®Õn 1 1/256 = 3.90 Ghi chó: - VCC = 5V - * Khi Vref/2 hë th× ®o ®­îc ë ®ã kho¶ng 2,5V - KÝch th­íc b­íc (®é ph©n d¶i) lµ sù thay ®æi nhá nhÊt mµ ADC cã thÓ ph©n biÖt ®­îc. 9. C¸c ch©n d÷ liÖu D0 - D7. C¸c ch©n d÷ liÖu D0 - D7 (D7 lµ bÝt cao nhÊt MSB vµ D0 lµ bÝt thÊp nhÊt LSB) lµ c¸c ch©n ®Çu ra d÷ liÖu sè. §©y lµ nh÷ng ch©n ®­îc ®Öm ba tr¹ng th¸i vµ d÷ liÖu ®­îc chuyÓn ®æi chØ ®­îc truy cËp khi ch©n CS = 0 vµ ch©n RD bÞ ®­a xuèng thÊp. §Ó tÝnh ®iÖn ¸p ®Çu ra ta cã thÓ sö dông c«ng thøc sau: buocthuockich V D in out = Víi Dout lµ ®Çu ra d÷ liÖu sè (d¹ng thËp ph©n). Vin lµ ®iÖn ¸p ®Çu vµo t­¬ng tù vµ ®é ph©n d¶i lµ sù thay ®æi nhá nhÊt ®­îc tÝnh nh­ lµ (2 ´ Vref/2) chia cho 256 ®èi víi ADC 8 bÝt. 10.Ch©n ®Êt t­¬ng tù vµ ch©n ®Êt sè. §©y lµ nh÷ng ch©n ®Çu vµo cÊp ®Êt chung cho c¶ tÝn hiÖu sè vµ t­¬ng tù. §Êt t­¬ng tù ®­îc nèi tíi ®Êt cña ch©n Vin t­¬ng tù, cßn ®Êt sè ®­îc nèi tíi ®Êt cña ch©n Vcc. Lý do mµ ta ph¶i cã hai ®Êt lµ ®Ó c¸ch ly tÝn hiÖu t­¬ng tù Vin tõ c¸c ®iÖn ¸p ký sinh t¹o ra viÖc chuyÓn m¹ch sè ®­îc chÝnh x¸c. Trong phÇn tr×nh bµy cña chóng ta th× c¸c ch©n nµy ®­îc nèi chung víi mét ®Êt. Tuy nhiªn, trong thùc tÕ thu ®o d÷ liÖu c¸c ch©n ®Êt nµy ®­îc nèi t¸ch biÖt. Tõ nh÷ng ®iÒu trªn ta kÕt luËn r»ng c¸c b­íc cÇn ph¶i thùc hiÖn khi chuyÓn ®æi d÷ liÖu bëi ADC 804 lµ: a) BËt CS = 0 vµ göi mét xung thÊp lªn cao tíi ch©n WR ®Ó b¾t ®Çu chuyÓn ®æi. b) Duy tr× hiÓn thÞ ch©n INTR . NÕu INTR xuèng thÊp th× viÖc chuyÓn ®æi ®­îc hoµn tÊt vµ ta cã thÓ sang b­íc kÕ tiÕp. NÕu INTR cao tiÕp tôc th¨m dß cho ®Õn khi nã xuèng thÊp. c) Sau khi ch©n INTR xuèng thÊp, ta bËt CS = 0 vµ göi mét xung cao - xuèng - thÊp ®Õn ch©n RD ®Ó lÊy d÷ liÖu ra khái chÝp ADC 804. Ph©n chia thêi gian cho qu¸ tr×nh nµy ®­îc tr×nh bµy trªn h×nh 12.6.

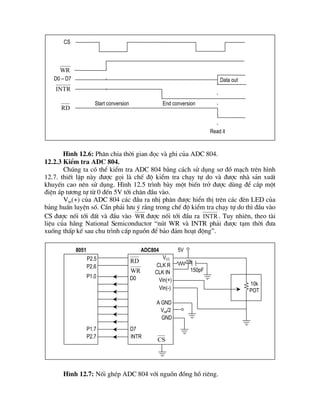

- 12. H×nh 12.6: Ph©n chia thêi gian ®äc vµ ghi cña ADC 804. 12.2.3 KiÓm tra ADC 804. Chóng ta cã thÓ kiÓm tra ADC 804 b»ng c¸ch sö dông s¬ ®å m¹ch trªn h×nh 12.7. thiÕt lËp nµy ®­îc gäi lµ chÕ ®é kiÓm tra ch¹y tù do vµ ®­îc nhµ s¶n xuÊt khuyÕn cao nªn sö dông. H×nh 12.5 tr×nh bµy mét biÕn trë ®­îc dïng ®Ó c¾p mét ®iÖn ¸p t­¬ng tù tõ 0 ®Õn 5V tíi ch©n ®Çu vµo. Vin(+) cña ADC 804 c¸c ®Çu ra nhÞ ph©n ®­îc hiÓn thÞ trªn c¸c ®Ìn LED cña b¶ng huÊn luyÖn sè. CÇn ph¶i l­u ý r»ng trong chÕ ®é kiÓm tra ch¹y tù do th× ®Çu vµo CS ®­îc nèi tíi ®Êt vµ ®Çu vµo WR ®­îc nèi tíi ®Çu ra INTR . Tuy nhiªn, theo tµi liÖu cña h·ng National Semiconductor “nót WR vµ INTR ph¶i ®­îc t¹m thêi ®­a xuèng thÊp kÕ sau chu tr×nh cÊp nguån ®Ó b¶o ®¶m ho¹t ®éng”. H×nh 12.7: Nèi ghÐp ADC 804 víi nguån ®ång hå riªng. CS D0 – D7 Data out Read it End conversionStart conversion WR INTR RD 8051 ADC804 P2.5 P2.6 P1.0 P1.7 P2.7 D0 D7 INTR GND A GND Vref/2 CLK IN CLK R VCC Vin(+) Vin(-) 150pF 5V 10k 10k POT RD WR CS

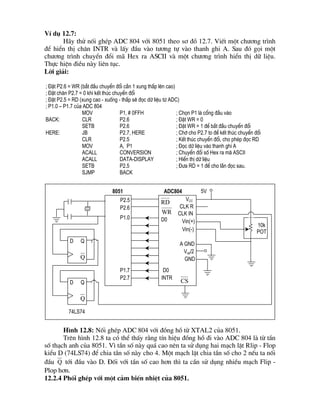

- 13. VÝ dô 12.7: H·y thö nèi ghÐp ADC 804 víi 8051 theo s¬ ®å 12.7. ViÕt mét ch­¬ng tr×nh ®Ó hiÓn thÞ ch©n INTR vµ lÊy ®Çu vµo t­¬ng tù vµo thanh ghi A. Sau ®ã gäi mét ch­¬ng tr×nh chuyÓn ®æi m· Hex ra ASCII vµ mét ch­¬ng tr×nh hiÓn thÞ d÷ liÖu. Thùc hiÖn ®iÒu nµy liªn tôc. Lêi gi¶i: ; §Æt P2.6 = WR (b¾t ®Çu chuyÓn ®æi cÇn 1 xung thÊp lªn cao) ; §Æt ch©n P2.7 = 0 khi kÕt thóc chuyÓn ®æi ; §Æt P2.5 = RD (xung cao - xuèng - thÊp sÏ ®äc d÷ liÖu tõ ADC) ; P1.0 – P1.7 cña ADC 804 MOV P1, # 0FFH ; Chän P1 lµ cæng ®Çu vµo BACK: CLR P2.6 ; §Æt WR = 0 SETB P2.6 ; §Æt WR = 1 ®Ó b¾t ®Çu chuyÓn ®æi HERE: JB P2.7, HERE ; Chê cho P2.7 to ®Ó kÕt thóc chuyÓn ®æi CLR P2.5 ; KÕt thóc chuyÓn ®æi, cho phÐp ®äc RD MOV A, P1 ; §äc d÷ liÖu vµo thanh ghi A ACALL CONVERSION ; ChuyÓn ®æi sè Hex ra m· ASCII ACALL DATA-DISPLAY ; HiÓn thÞ d÷ liÖu SETB P2.5 ; §­a RD = 1 ®Ó cho lÇn ®äc sau. SJMP BACK H×nh 12.8: Nèi ghÐp ADC 804 víi ®ång hå tõ XTAL2 cña 8051. Trªn h×nh 12.8 ta cã thÓ thÊy r»ng tÝn hiÖu ®ång hå ®i vµo ADC 804 lµ tõ tÇn sè th¹ch anh cña 8051. V× tÇn sè nµy qu¸ cao nªn ta sö dông hai m¹ch lËt Rlip - Flop kiÓu D (74LS74) ®Ó chia tÇn sè nµy cho 4. Mét m¹ch lËt chia tÇn sè cho 2 nÕu ta nèi ®Çu Q tíi ®Çu vµo D. §èi víi tÇn sè cao h¬n th× ta cÇn sö dông nhiÒu m¹ch Flip - Plop h¬n. 12.2.4 Phèi ghÐp víi mét c¶m biÕn nhiÖt cña 8051. 8051 ADC804 P2.5 P2.6 P1.0 P1.7 P2.7 D0 D0 INTR GND A GND Vref/2 CLK IN CLK R VCC Vin(+) Vin(-) 5V 10k POT RD WR CSD Q Q D Q Q 74LS74

- 14. C¸c bé biÕn ®æi (Transducer) chuyÓn ®æi c¸c ®¹i l­îng vËt lý vÝ dô nh­ nhiÖt ®é, c­êng ®é ¸nh s¸ng, l­u tèc vµ tèc ®é thµnh c¸c tÝn hiÖu ®iÖn phô thuéc vµo bé biÕn ®æi mµ ®Çu ra cã thÓ lµ tÝn hiÖu d¹ng ®iÖn ¸p, dßng, trë kh¸ng hay dung kh¸ng. VÝ dô, nhiÖt ®é ®­îc biÕn ®æi thµnh vÒ c¸c tÝn hiÖu ®iÖn sö dông mét bé biÕn ®æi gäi lµ Rhermistor (bé c¶m biÕn nhiÖt), mét bé c¶m biÕn nhiÖt ®¸p øng sù thay ®æi nhiÖt ®é b»ng c¸ch thay ®æi trë kh¸ng nh­ng ®¸p øng cña nã kh«ng tuyÕn tÝnh (xem b¶ng 12.6). B¶ng 12.6: Trë kh¸ng cña bé c¶m biÕn nhiÖt theo nhiÖt ®é. NhiÖt ®é (0 C) Trë kh¸ng cña c¶m biÕn (kW) 0 29.490 25 10.000 50 3.893 75 1.700 100 0.817 B¶ng 12.7: H­íng dÉn chän lo¹t c¸c c¶m biÕn hä LM34. M· ký hiÖu D¶i nhiÖt ®é §é chÝnh x¸c §Çu ra LM34A -55 F to + 300 C + 2.0 F 10mV/F LM34 -55 F to + 300 C + 3.0 F 10mV/F LM34CA -40 F to + 230 C + 2.0 F 10mV/F LM34C -40 F to + 230 C + 3.0 F 10mV/F LM34D -32 F to + 212 C + 4.0 F 10mV/F B¶ng 12.8: H­íng dÉn chän lo¹t c¸c c¶m biÕn nhiÖt hä LM35. M· s¶n phÈm D¶i nhiÖt ®é §é chÝnh x¸c §Çu ra LM35A -55 C to + 150 C + 1.0 C 10 mV/F LM35 -55 C to + 150 C + 1.5 C 10 mV/F LM35CA -40 C to + 110 C + 1.0 C 10 mV/F LM35C -40 C to + 110 C + 1.5 C 10 mV/F LM35D 0 C to + 100 C + 2.0 C 10 mV/F TÝnh chÊt g¾n liÖn víi viÖc viÕt phÇn mÒm cho c¸c thiÕt bÞ phi tuyÕn nh­ vËy ®· ®­a nhiÒu nhµ s¶n xuÊt tung ra thÞ tr­êng c¸c lo¹t bé c¶m biÕn nhiÖt tuyÕn tÝnh. C¸c bé c¶m biÕn nhiÖt ®¬n gi¶n vµ ®­îc sö dông réng r·i bao gåm c¸c lo¹t hä LM34 vµ LM35 cña h·ng National Semiconductor Corp. 12.2.5 C¸c bé c¶m biÕn nhiÖt hä LM34 vµ LM35. Lo¹t c¸c bé c¶m biÕn LM34 lµ c¸c bé c¶m biÕn nhiÖt m¹ch tÝch hîp chÝnh x¸c cao mµ ®iÖn ¸p ®Çu ra cña nã tû lÖ tuyÕn tÝnh v¬Ý nhiÖt ®é Fahrenheit (xem h×nh 12.7). lo¹t LM34 kh«ng yªu cÇu c©n chØnh bªn ngoµi v× vèn nã ®· ®­îc c©n chØnh råi. Nã ®­a ra ®iÖn ¸p 10mV cho sù thay ®æi nhiÖt ®é 10 F. b¶ng 12.7 h­íng dÉn ta chän c¸c c¶m biÕn lo¹t LM34.

- 15. Lo¹t c¸c bé c¶m biÕn LM35 còng lµ c¸c bé c¶m biÕn nhiÖt m¸ch tÝch hîp chÝnh x¸c cao mµ ®iÖn ¸p ®Çu ra cña nã tû lÖ tuyÕn tÝnh víi nhiÖt ®é theo thang ®é Celsius. Chóng còng kh«ng yªu cÇu c©n chØnh ngoµi v× vèn chóng ®· ®­îc c©n chØnh. Chóng ®­a ra ®iÖn ¸p 10Mv cho mçi sù thay ®æi 10 C. B¶ng 12.8 h­íng dÉn ta chän c¸c c¶m biÕn hä LM35. 12.2.6 Phèi hîp tÝn hiÖu vµ phèi ghÐp LM35 víi 8051. Phèi hîp tÝn hiÖu lµ mét thuËt ng÷ ®­îc sö dông réng r·i trong lÜnh vùc thu ®o d÷ liÖu. HÇu hÕt c¸c bé biÕn ®æi ®Òu ®­a ra c¸c tÝn hiÖu ®iÖn d¹ng ®iÖn ¸p, dßng ®iÖn, dung kh¸ng hoÆc trë kh¸ng. Tuy nhiªn, chóng ta cÇn chuyÓn ®æi c¸c tÝn hiÖu nµy vÒ ®iÖn ¸p nh»m göi ®Çu vµo ®Õn bé chuyÓn ®æi ADC. Sù chuyÓn ®æi (biÕn ®æi) nµy ®­îc gäi chung lµ phèi hîp tÝn hiÖu. Phèi hîp tÝn hiÖu cã thÓ lµ viÖc chuyÓn ®æi dßng ®iÖn thµnh ®iÖn ¸p hoÆc sù khuyÕch ®¹i tÝn hiÖu. VÝ dô, bé c¶m biÕn nhiÖt thay ®æi trë kh¸ng víi nhiÖt ®é. Sù thay ®æi trë kh¸ng ph¶i ®­îc chuyÓn thµnh ®iÖn ¸p ®Ó cã thÓ ®­îc sö dông cho c¸c ADC. XÐt tr­êng hîp nèi mét LM35 tíi mét ADC 804 v× ADC 804 cã ®é ph©n d¶i 8 bÝt víi tèi ®a 256 b­íc (28 ) vµ LM35 (hoÆc ML34) t¹o ®iÖn ¸p 10mV cho mçi sù thay ®æi nhiÖt ®é 10 C nªn ta cã thÓ t¹o ®iÒu kiÖn Vin cña ADC 804 t¹o ra mét Vout = 2560mV (2,56V) cho ®Çu ra ®Çu thang ®o. do vËy, nh»m t¹o ra Vout ®Çy thang 2,56V cho ADC 804 ta cÇn ®Æt ®iÖn ¸p Vref/2 = 1,28V. §iÒu nµy lµm cho Vout cña ADC 804 ®¸p øng trùc tiÕp víi nhiÖt ®é ®­îc hiÓn thÞ trªn LM35 (xem b¶ng 12.9). C¸c gi¸ trÞ cña Vref/2 ®­îc cho ë b¶ng 12.5. B¶ng 12.9: NhiÖt ®é. NhiÖt ®é (0 C) Vin (mV) Vout (D7 – D0) 0 0 0000 0000 1 10 0000 0001 2 20 0000 0010 3 30 0000 0011 10 100 0000 1010 30 300 0001 1110 C¸c ®¹i l­îng vËt lý (nhiÖt ®é, ¸p suÊt, l­u tèc v.v…) Bé biÕn ®æi Phèi hîp tÝn hiÖu ADC Bé vi ®iÒu khiÓn

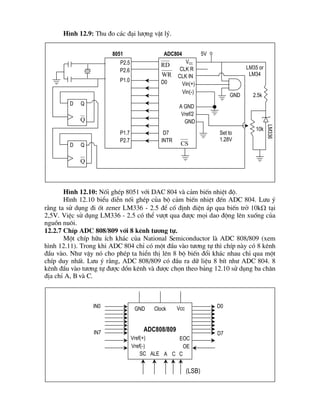

- 16. H×nh 12.9: Thu ®o c¸c ®¹i l­îng vËt lý. H×nh 12.10 H×nh 12.10: Nèi ghÐp 8051 víi DAC 804 vµ c¶m biÕn nhiÖt ®é. H×nh 12.10 biÓu diÔn nèi ghÐp cña bé c¶m biÕn nhiÖt ®Õn ADC 804. L­u ý r»ng ta sö dông ®i èt zener LM336 - 2.5 ®Ó cè ®Þnh ®iÖn ¸p qua biÕn trë 10kW t¹i 2,5V. ViÖc sö dông LM336 - 2.5 cã thÓ v­ît qua ®­îc mäi dao ®éng lªn xuèng cña nguån nu«i. 12.2.7 ChÝp ADC 808/809 víi 8 kªnh t­¬ng tù. Mét chÝp h÷u Ých kh¸c cña National Semiconductor lµ ADC 808/809 (xem h×nh 12.11). Trong khi ADC 804 chØ cã mét ®Çu vµo t­¬ng tù th× chÝp nµy cã 8 kªnh ®Çu vµo. Nh­ vËy nã cho phÐp ta hiÓn thÞ lªn 8 bé biÕn ®æi kh¸c nhau chØ qua mét chÝp duy nhÊt. L­u ý r»ng, ADC 808/809 cã ®Çu ra d÷ liÖu 8 bÝt nh­ ADC 804. 8 kªnh ®Çu vµo t­¬ng tù ®­îc dån kªnh vµ ®­îc chän theo b¶ng 12.10 sö dông ba ch©n ®Þa chØ A, B vµ C. (LSB) GND Clock Vcc ADC808/809 Vref(+) Vref(-) CCASC ALE OE EOC D7 D0IN0 IN7 8051 ADC804 P2.5 P2.6 P1.0 P1.7 P2.7 D0 D7 INTR GND A GND Vref/2 CLK IN CLK R VCC Vin(+) Vin(-) 5V RD WR CSD Q Q D Q Q Set to 1.28V GND LM35 or LM34 LM336 2.5k 10k

- 17. H×nh 12.11: Bé biÕn ®æi ADC 808/809. B¶ng 12.10: Chän kªnh t­¬ng tù cña ADC 808. Chän kªnh t­¬ng tù C B A IN0 0 0 0 IN1 0 0 1 IN2 0 1 0 IN3 0 1 1 IN4 1 0 0 IN5 1 0 1 IN6 1 1 0 IN7 1 1 1 Trong ADC 808/809 th× Vrer(+) vµ Vref(-) thiÕt lËp ®iÖn ¸p tham chiÕu. NÕu Vref (-1) = Gnd vµ Vref (+) = 5V th× ®é ph©n d¶i lµ 5V/256 = 19,53mV. Do vËy, ®Ó cã ®é ph©n d¶i 10mV ta cÇn ®Æt Vref (+) = 2,56V vµ Vref (-) = Gnd. Tõ h×nh 12.11 ta thÊy cã ch©n ALE. Ta sö dông c¸c ®Þa chØ A, B vµ C ®Ó chän kªnh ®Çu vµo IN0 – IN7 vµ kÝch ho¹t ch©n ALE ®Ó chèt ®Þa chØ. Ch©n SetComplete ®Ó b¾t ®Çu chuyÓn ®æi (Start Conversion). Ch©n EOC ®­îc dïng ®Ó kÕt thóc chuyÓn ®æi (End - Of - Conversion) vµ ch©n OE lµ cho phÐp ®äc ®Çu ra (Out put Enable). 12.2.7 C¸c b­íc lËp tr×nh cho ADC 808/809. C¸c b­íc chuyÓn d÷ liÖu tõ ®Çu vµo cña ADC 808/809 vµo bé vi ®iÒu khiÓn nh­ sau: 1. Chän mét kªnh t­¬ng tù b»ng c¸ch t¹o ®Þa chØ A, B vµ C theo b¶ng 12.10. 2. KÝch ho¹t ch©n ALE (cho phÐp chèt ®Þa chØ Address Latch Enable). Nã cÇn xung thÊp lªn cao ®Ó chèt ®Þa chØ. 3. KÝch ho¹t ch©n SCb»ng xung cao xuèng thÊp ®Ó b¾t ®Çu chuyÓn ®æi. 4. HiÓn thÞ OEC ®Ó b¸o kÕt thóc chuyÓn ®æi. §Çu ra cao - xuèng - thÊp b¸o r»ng d÷ liÖu ®· ®­îc chuyÓn ®æi vµ cÇn ph¶i ®­îc lÊy ®i. 5. KÝch ho¹t OE cho phÐp ®äc d÷ liÖu ra cña ADC. Mét xung cao xuèng thÊp tíi ch©n OE sÏ ®em d÷ liÖu sè ra khái chÝp ADC. L­u ý r»ng trong ADC 808/809 kh«ng cã ®ång hå riªng vµ do vËy ph¶i cÊp xung ®ång bé ngoµi ®Õn ch©n CLK. MÆc dï tèc ®é chuyÓn ®æi phô thuéc vµo tÇn sè ®ång hå ®­îc nèi ®Õn CLK nh­ng nã kh«ng nhanh h¬n 100ms.