ĐŒĐŸĐ°Đż 2011 05

- 1. ĐĐŸĐŒĐżĐžĐ»ŃŃĐžŃ Đž ĐŒĐŸĐŽĐ”Đ»ĐžŃĐŸĐČĐ°ĐœĐžĐ” VHDL-ĐșĐŸĐŽĐ° ĐŻĐ·ŃĐșĐž ĐŸĐżĐžŃĐ°ĐœĐžŃ Đ°ĐżĐżĐ°ŃĐ°ŃŃŃŃ Đ„Đ°Ń Đ°ĐœĐŸĐČĐ° Đ.Đ, ĐșĐ°Ń.ĐĐĐĐą, Đ„ĐĐŁĐ Đ, e-mail: 1 hahanova@mail.ru 09.02.2011

- 2. ï¶ ĐŠĐ”Đ»Ń Đ»Đ”ĐșŃОО: ĐĐ·ŃŃĐžŃŃ ĐżŃĐžĐœŃĐžĐżŃ ĐŒĐŸĐŽĐ”Đ»ĐžŃĐŸĐČĐ°ĐœĐžŃ Đž ŃĐ”ŃŃĐžŃĐŸĐČĐ°ĐœĐžŃ VHDL- ĐżŃĐŸĐ”ĐșŃĐŸĐČ ï¶ ĐĄĐŸĐŽĐ”ŃĐ¶Đ°ĐœĐžĐ”: 1. ĐĐŸĐŒĐżĐžĐ»ŃŃĐžŃ, ŃĐ°Đ·ŃĐ°Đ±ĐŸŃĐșĐ°, Đž ĐŒĐŸĐŽĐ”Đ»ĐžŃĐŸĐČĐ°ĐœĐžĐ” VHDL - ĐșĐŸĐŽĐ° 2. ĐąŃĐ°ĐœŃĐżĐŸŃŃĐœĐ°Ń Đž ĐžĐœĐ”ŃŃĐžĐŸĐœĐœĐ°Ń Đ·Đ°ĐŽĐ”ŃжĐșĐž 3. ĐŃĐ°ĐčĐČĐ”Ń ŃĐžĐłĐœĐ°Đ»Đ° 4. ĐŃĐ°ĐČĐžĐ»ĐŸ ŃĐŸŃĐŒĐžŃĐŸĐČĐ°ĐœĐžŃ ĐŸŃĐ”ŃДЎО бŃĐŽŃŃĐžŃ Đ·ĐœĐ°ŃĐ”ĐœĐžĐč ŃĐžĐłĐœĐ°Đ»Đ° 5. ĐпДŃĐ°ŃĐŸŃ wait бДз паŃĐ°ĐŒĐ”ŃŃĐ° 2 Đ„Đ°Ń Đ°ĐœĐŸĐČĐ° Đ.Đ, ĐșĐ°Ń.ĐĐĐĐą, Đ„ĐĐŁĐ Đ, e-mail: hahanova@mail.ru 09.02.2011

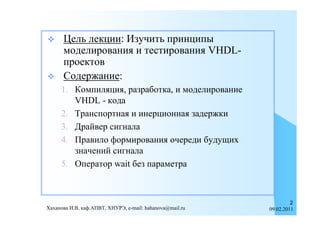

- 3. ĐĐŸĐŒĐżĐžĐ»ŃŃĐžŃ, ŃĐ°Đ·ŃĐ°Đ±ĐŸŃĐșĐ°, Đž ĐŒĐŸĐŽĐ”Đ»ĐžŃĐŸĐČĐ°ĐœĐžĐ” VHDL - ĐșĐŸĐŽĐ° 3 Đ„Đ°Ń Đ°ĐœĐŸĐČĐ° Đ.Đ, ĐșĐ°Ń.ĐĐĐĐą, Đ„ĐĐŁĐ Đ, e-mail: hahanova@mail.ru 09.02.2011

- 4. ĐąŃĐ°ĐœŃĐżĐŸŃŃĐœĐ°Ń Đž ĐžĐœĐ”ŃŃĐžĐŸĐœĐœĐ°Ń Đ·Đ°ĐŽĐ”ŃжĐșĐž (1) VHDL ĐżŃĐ”ĐŽĐ»Đ°ĐłĐ°Đ”Ń ĐŽĐČĐ° ŃОпа Đ·Đ°ĐŽĐ”ŃжДĐș: ŃŃĐ°ĐœŃĐżĐŸŃŃĐœŃŃ Đž ĐžĐœĐ”ŃŃĐžĐŸĐœĐœŃŃ. ï ĐąŃĐ°ĐœŃĐżĐŸŃŃĐœĐ°Ń ŃĐŸĐŸŃĐČĐ”ŃŃŃĐČŃĐ”Ń ĐŒĐŸĐŽĐ”Đ»Đž Đ·Đ°ĐŽĐ”ŃжДĐș ĐœĐ° ĐżŃĐŸĐČĐŸĐŽĐœĐžĐșĐ°Ń ŃŃ Đ”ĐŒŃ. ĐŃŃ ĐŸĐŽĐœĐŸĐč ŃĐžĐłĐœĐ°Đ» ĐżĐŸĐČŃĐŸŃŃĐ”Ń ĐČ ŃŃĐŸĐŒ ŃĐ»ŃŃĐ°Đ” ŃĐŸŃĐŒŃ ĐČŃ ĐŸĐŽĐœĐŸĐłĐŸ ŃĐžĐłĐœĐ°Đ»Đ° Ń Đ·Đ°ĐŽĐ”ŃжĐșĐŸĐč ĐœĐ° ŃĐșĐ°Đ·Đ°ĐœĐœĐŸĐ” ĐČŃĐ”ĐŒŃ. ĐĄĐžĐœŃĐ°ĐșŃĐžŃ: signal_name <= transport expression after delay-time ï ĐĐœĐ”ŃŃĐžĐŸĐœĐœĐ°Ń ĐŒĐŸĐŽĐ”Đ»ĐžŃŃĐ”Ń Đ·Đ°ĐŽĐ”ŃжĐșŃ ĐœĐ° ĐČĐ”ĐœŃОлŃŃ ĐžĐ»Đž ĐŽŃŃĐłĐžŃ ŃŃŃŃĐŸĐčŃŃĐČĐ°Ń , ĐœĐ” ĐżŃĐŸĐżŃŃĐșĐ°ŃŃĐžŃ ĐșĐŸŃĐŸŃĐșОД ĐžĐŒĐżŃĐ»ŃŃŃ ĐČŃ ĐŸĐŽĐœĐŸĐłĐŸ ŃĐžĐłĐœĐ°Đ»Đ° ĐœĐ° ĐČŃŃ ĐŸĐŽ. ĐŃĐŸ Đ·Đ°ĐŽĐ”ŃжĐșĐ° ĐžŃĐżĐŸĐ»ŃĐ·ŃĐ”ŃŃŃ ĐżĐŸ ŃĐŒĐŸĐ»ŃĐ°ĐœĐžŃ. ĐĄĐžĐœŃĐ°ĐșŃĐžŃ: signal_name <= reject pulse-width [ inertial ] expression after delay-time 4 Đ„Đ°Ń Đ°ĐœĐŸĐČĐ° Đ.Đ, ĐșĐ°Ń.ĐĐĐĐą, Đ„ĐĐŁĐ Đ, e-mail: hahanova@mail.ru 09.02.2011

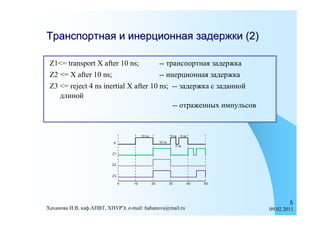

- 5. ĐąŃĐ°ĐœŃĐżĐŸŃŃĐœĐ°Ń Đž ĐžĐœĐ”ŃŃĐžĐŸĐœĐœĐ°Ń Đ·Đ°ĐŽĐ”ŃжĐșĐž (2) Z1<= transport X after 10 ns; -- ŃŃĐ°ĐœŃĐżĐŸŃŃĐœĐ°Ń Đ·Đ°ĐŽĐ”ŃжĐșĐ° Z2 <= X after 10 ns; -- ĐžĐœĐ”ŃŃĐžĐŸĐœĐœĐ°Ń Đ·Đ°ĐŽĐ”ŃжĐșĐ° Z3 <= reject 4 ns inertial X after 10 ns; -- Đ·Đ°ĐŽĐ”ŃжĐșĐ° Ń Đ·Đ°ĐŽĐ°ĐœĐœĐŸĐč ĐŽĐ»ĐžĐœĐŸĐč -- ĐŸŃŃĐ°Đ¶Đ”ĐœĐœŃŃ ĐžĐŒĐżŃĐ»ŃŃĐŸĐČ 10 ns 3 ns 5 ns X 10 ns 2 ns Z1 Z2 Z3 0 10 20 30 40 50 5 Đ„Đ°Ń Đ°ĐœĐŸĐČĐ° Đ.Đ, ĐșĐ°Ń.ĐĐĐĐą, Đ„ĐĐŁĐ Đ, e-mail: hahanova@mail.ru 09.02.2011

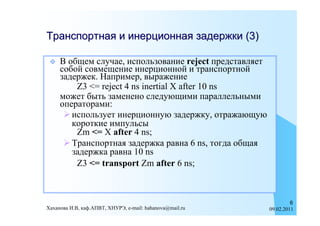

- 6. ĐąŃĐ°ĐœŃĐżĐŸŃŃĐœĐ°Ń Đž ĐžĐœĐ”ŃŃĐžĐŸĐœĐœĐ°Ń Đ·Đ°ĐŽĐ”ŃжĐșĐž (3) ï¶ Đ ĐŸĐ±ŃĐ”ĐŒ ŃĐ»ŃŃĐ°Đ”, ĐžŃĐżĐŸĐ»ŃĐ·ĐŸĐČĐ°ĐœĐžĐ” reject ĐżŃДЎŃŃĐ°ĐČĐ»ŃĐ”Ń ŃĐŸĐ±ĐŸĐč ŃĐŸĐČĐŒĐ”ŃĐ”ĐœĐžĐ” ĐžĐœĐ”ŃŃĐžĐŸĐœĐœĐŸĐč Đž ŃŃĐ°ĐœŃĐżĐŸŃŃĐœĐŸĐč Đ·Đ°ĐŽĐ”ŃжДĐș. ĐĐ°ĐżŃĐžĐŒĐ”Ń, ĐČŃŃĐ°Đ¶Đ”ĐœĐžĐ” Z3 <= reject 4 ns inertial X after 10 ns ĐŒĐŸĐ¶Đ”Ń Đ±ŃŃŃ Đ·Đ°ĐŒĐ”ĐœĐ”ĐœĐŸ ŃлДЎŃŃŃĐžĐŒĐž паŃаллДлŃĐœŃĐŒĐž ĐŸĐżĐ”ŃĐ°ŃĐŸŃĐ°ĐŒĐž: ï ĐžŃĐżĐŸĐ»ŃĐ·ŃĐ”Ń ĐžĐœĐ”ŃŃĐžĐŸĐœĐœŃŃ Đ·Đ°ĐŽĐ”ŃжĐșŃ, ĐŸŃŃажаŃŃŃŃ ĐșĐŸŃĐŸŃĐșОД ĐžĐŒĐżŃĐ»ŃŃŃ Zm <= X after 4 ns; ï ĐąŃĐ°ĐœŃĐżĐŸŃŃĐœĐ°Ń Đ·Đ°ĐŽĐ”ŃжĐșĐ° ŃĐ°ĐČĐœĐ° 6 ns, ŃĐŸĐłĐŽĐ° ĐŸĐ±ŃĐ°Ń Đ·Đ°ĐŽĐ”ŃжĐșĐ° ŃĐ°ĐČĐœĐ° 10 ns Z3 <= transport Zm after 6 ns; 6 Đ„Đ°Ń Đ°ĐœĐŸĐČĐ° Đ.Đ, ĐșĐ°Ń.ĐĐĐĐą, Đ„ĐĐŁĐ Đ, e-mail: hahanova@mail.ru 09.02.2011

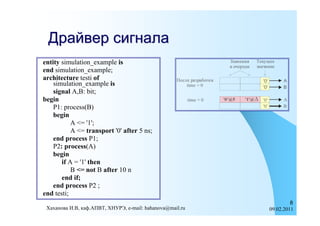

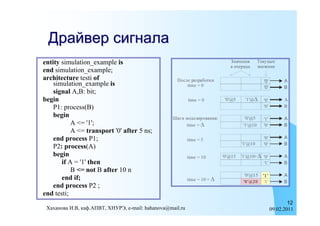

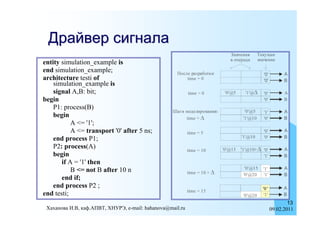

- 7. ĐŃĐ°ĐčĐČĐ”Ń ŃĐžĐłĐœĐ°Đ»Đ° entity simulation_example is ĐĐœĐ°ŃĐ”ĐœĐžŃ ĐąĐ”ĐșŃŃДД ĐČ ĐŸŃĐ”ŃДЎО Đ·ĐœĐ°ŃĐ”ĐœĐžĐ” end simulation_example; architecture testi of ĐĐŸŃлД ŃĐ°Đ·ŃĐ°Đ±ĐŸŃĐșĐž A simulation_example is '0' time = 0 '0' B signal A,B: bit; begin P1: process(B) begin A <= '1'; A <= transport '0' after 5 ns; end process P1; P2: process(A) begin if A = '1' then B <= not B after 10 n end if; end process P2 ; end testi; 7 Đ„Đ°Ń Đ°ĐœĐŸĐČĐ° Đ.Đ, ĐșĐ°Ń.ĐĐĐĐą, Đ„ĐĐŁĐ Đ, e-mail: hahanova@mail.ru 09.02.2011

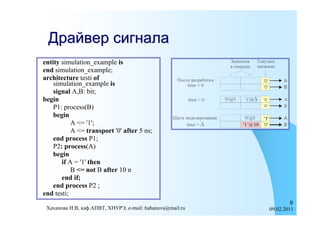

- 8. ĐŃĐ°ĐčĐČĐ”Ń ŃĐžĐłĐœĐ°Đ»Đ° entity simulation_example is end simulation_example; architecture testi of simulation_example is signal A,B: bit; begin P1: process(B) begin A <= '1'; A <= transport '0' after 5 ns; end process P1; P2: process(A) begin if A = '1' then B <= not B after 10 n end if; end process P2 ; end testi; 8 Đ„Đ°Ń Đ°ĐœĐŸĐČĐ° Đ.Đ, ĐșĐ°Ń.ĐĐĐĐą, Đ„ĐĐŁĐ Đ, e-mail: hahanova@mail.ru 09.02.2011

- 9. ĐŃĐ°ĐčĐČĐ”Ń ŃĐžĐłĐœĐ°Đ»Đ° entity simulation_example is end simulation_example; architecture testi of simulation_example is signal A,B: bit; begin P1: process(B) begin A <= '1'; A <= transport '0' after 5 ns; end process P1; P2: process(A) begin if A = '1' then B <= not B after 10 n end if; end process P2 ; end testi; 9 Đ„Đ°Ń Đ°ĐœĐŸĐČĐ° Đ.Đ, ĐșĐ°Ń.ĐĐĐĐą, Đ„ĐĐŁĐ Đ, e-mail: hahanova@mail.ru 09.02.2011

- 10. ĐŃĐ°ĐčĐČĐ”Ń ŃĐžĐłĐœĐ°Đ»Đ° entity simulation_example is end simulation_example; architecture testi of simulation_example is signal A,B: bit; begin P1: process(B) begin A <= '1'; A <= transport '0' after 5 ns; end process P1; P2: process(A) begin if A = '1' then B <= not B after 10 n end if; end process P2 ; end testi; 10 Đ„Đ°Ń Đ°ĐœĐŸĐČĐ° Đ.Đ, ĐșĐ°Ń.ĐĐĐĐą, Đ„ĐĐŁĐ Đ, e-mail: hahanova@mail.ru 09.02.2011

- 11. ĐŃĐ°ĐčĐČĐ”Ń ŃĐžĐłĐœĐ°Đ»Đ° entity simulation_example is end simulation_example; architecture testi of simulation_example is signal A,B: bit; begin P1: process(B) begin A <= '1'; A <= transport '0' after 5 ns; end process P1; P2: process(A) begin if A = '1' then B <= not B after 10 n end if; end process P2 ; end testi; 11 Đ„Đ°Ń Đ°ĐœĐŸĐČĐ° Đ.Đ, ĐșĐ°Ń.ĐĐĐĐą, Đ„ĐĐŁĐ Đ, e-mail: hahanova@mail.ru 09.02.2011

- 12. ĐŃĐ°ĐčĐČĐ”Ń ŃĐžĐłĐœĐ°Đ»Đ° entity simulation_example is end simulation_example; architecture testi of simulation_example is signal A,B: bit; begin P1: process(B) begin A <= '1'; A <= transport '0' after 5 ns; end process P1; P2: process(A) begin if A = '1' then B <= not B after 10 n end if; end process P2 ; end testi; 12 Đ„Đ°Ń Đ°ĐœĐŸĐČĐ° Đ.Đ, ĐșĐ°Ń.ĐĐĐĐą, Đ„ĐĐŁĐ Đ, e-mail: hahanova@mail.ru 09.02.2011

- 13. ĐŃĐ°ĐčĐČĐ”Ń ŃĐžĐłĐœĐ°Đ»Đ° entity simulation_example is end simulation_example; architecture testi of simulation_example is signal A,B: bit; begin P1: process(B) begin A <= '1'; A <= transport '0' after 5 ns; end process P1; P2: process(A) begin if A = '1' then B <= not B after 10 n end if; end process P2 ; end testi; 13 Đ„Đ°Ń Đ°ĐœĐŸĐČĐ° Đ.Đ, ĐșĐ°Ń.ĐĐĐĐą, Đ„ĐĐŁĐ Đ, e-mail: hahanova@mail.ru 09.02.2011

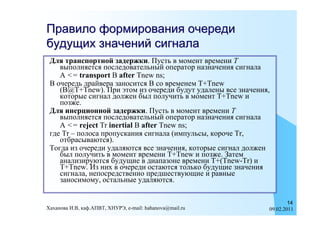

- 14. ĐŃĐ°ĐČĐžĐ»ĐŸ ŃĐŸŃĐŒĐžŃĐŸĐČĐ°ĐœĐžŃ ĐŸŃĐ”ŃДЎО бŃĐŽŃŃĐžŃ Đ·ĐœĐ°ŃĐ”ĐœĐžĐč ŃĐžĐłĐœĐ°Đ»Đ° ĐĐ»Ń ŃŃĐ°ĐœŃĐżĐŸŃŃĐœĐŸĐč Đ·Đ°ĐŽĐ”ŃжĐșĐž. ĐŃŃŃŃ ĐČ ĐŒĐŸĐŒĐ”ĐœŃ ĐČŃĐ”ĐŒĐ”ĐœĐž T ĐČŃĐżĐŸĐ»ĐœŃĐ”ŃŃŃ ĐżĐŸŃĐ»Đ”ĐŽĐŸĐČĐ°ŃДлŃĐœŃĐč ĐŸĐżĐ”ŃĐ°ŃĐŸŃ ĐœĐ°Đ·ĐœĐ°ŃĐ”ĐœĐžŃ ŃĐžĐłĐœĐ°Đ»Đ° A <= transport B after Tnew ns; Đ ĐŸŃĐ”ŃĐ”ĐŽŃ ĐŽŃĐ°ĐčĐČĐ”ŃĐ° Đ·Đ°ĐœĐŸŃĐžŃŃŃ B ŃĐŸ ĐČŃĐ”ĐŒĐ”ĐœĐ”ĐŒ T+Tnew (B@T+Tnew). ĐŃĐž ŃŃĐŸĐŒ Оз ĐŸŃĐ”ŃДЎО бŃĐŽŃŃ ŃĐŽĐ°Đ»Đ”ĐœŃ ĐČŃĐ” Đ·ĐœĐ°ŃĐ”ĐœĐžŃ, ĐșĐŸŃĐŸŃŃĐ” ŃĐžĐłĐœĐ°Đ» ĐŽĐŸĐ»Đ¶Đ”Đœ бŃĐ» ĐżĐŸĐ»ŃŃĐžŃŃ ĐČ ĐŒĐŸĐŒĐ”ĐœŃ T+Tnew Đž ĐżĐŸĐ·Đ¶Đ”. ĐĐ»Ń ĐžĐœĐ”ŃŃĐžĐŸĐœĐœĐŸĐč Đ·Đ°ĐŽĐ”ŃжĐșĐž. ĐŃŃŃŃ ĐČ ĐŒĐŸĐŒĐ”ĐœŃ ĐČŃĐ”ĐŒĐ”ĐœĐž T ĐČŃĐżĐŸĐ»ĐœŃĐ”ŃŃŃ ĐżĐŸŃĐ»Đ”ĐŽĐŸĐČĐ°ŃДлŃĐœŃĐč ĐŸĐżĐ”ŃĐ°ŃĐŸŃ ĐœĐ°Đ·ĐœĐ°ŃĐ”ĐœĐžŃ ŃĐžĐłĐœĐ°Đ»Đ° A <= reject Tr inertial B after Tnew ns; гЎД Tr â ĐżĐŸĐ»ĐŸŃĐ° ĐżŃĐŸĐżŃŃĐșĐ°ĐœĐžŃ ŃĐžĐłĐœĐ°Đ»Đ° (ĐžĐŒĐżŃĐ»ŃŃŃ, ĐșĐŸŃĐŸŃĐ” Tr, ĐŸŃбŃĐ°ŃŃĐČĐ°ŃŃŃŃ). ĐąĐŸĐłĐŽĐ° Оз ĐŸŃĐ”ŃДЎО ŃĐŽĐ°Đ»ŃŃŃŃŃ ĐČŃĐ” Đ·ĐœĐ°ŃĐ”ĐœĐžŃ, ĐșĐŸŃĐŸŃŃĐ” ŃĐžĐłĐœĐ°Đ» ĐŽĐŸĐ»Đ¶Đ”Đœ бŃĐ» ĐżĐŸĐ»ŃŃĐžŃŃ ĐČ ĐŒĐŸĐŒĐ”ĐœŃ ĐČŃĐ”ĐŒĐ”ĐœĐž T+Tnew Đž ĐżĐŸĐ·Đ¶Đ”. ĐĐ°ŃĐ”ĐŒ Đ°ĐœĐ°Đ»ĐžĐ·ĐžŃŃŃŃŃŃ Đ±ŃĐŽŃŃОД ĐČ ĐŽĐžĐ°ĐżĐ°Đ·ĐŸĐœĐ” ĐČŃĐ”ĐŒĐ”ĐœĐž T+(Tnew-Tr) Đž T+Tnew. ĐĐ· ĐœĐžŃ ĐČ ĐŸŃĐ”ŃДЎО ĐŸŃŃĐ°ŃŃŃŃ ŃĐŸĐ»ŃĐșĐŸ бŃĐŽŃŃОД Đ·ĐœĐ°ŃĐ”ĐœĐžŃ ŃĐžĐłĐœĐ°Đ»Đ°, ĐœĐ”ĐżĐŸŃŃДЎŃŃĐČĐ”ĐœĐœĐŸ ĐżŃДЎŃĐ”ŃŃĐČŃŃŃОД Đž ŃĐ°ĐČĐœŃĐ” Đ·Đ°ĐœĐŸŃĐžĐŒĐŸĐŒŃ, ĐŸŃŃĐ°Đ»ŃĐœŃĐ” ŃĐŽĐ°Đ»ŃŃŃŃŃ. 14 Đ„Đ°Ń Đ°ĐœĐŸĐČĐ° Đ.Đ, ĐșĐ°Ń.ĐĐĐĐą, Đ„ĐĐŁĐ Đ, e-mail: hahanova@mail.ru 09.02.2011

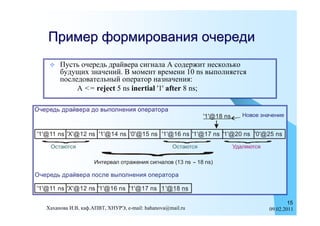

- 15. ĐŃĐžĐŒĐ”Ń ŃĐŸŃĐŒĐžŃĐŸĐČĐ°ĐœĐžŃ ĐŸŃĐ”ŃДЎО ï¶ ĐŃŃŃŃ ĐŸŃĐ”ŃĐ”ĐŽŃ ĐŽŃĐ°ĐčĐČĐ”ŃĐ° ŃĐžĐłĐœĐ°Đ»Đ° Đ ŃĐŸĐŽĐ”ŃĐ¶ĐžŃ ĐœĐ”ŃĐșĐŸĐ»ŃĐșĐŸ бŃĐŽŃŃĐžŃ Đ·ĐœĐ°ŃĐ”ĐœĐžĐč. Đ ĐŒĐŸĐŒĐ”ĐœŃ ĐČŃĐ”ĐŒĐ”ĐœĐž 10 ns ĐČŃĐżĐŸĐ»ĐœŃĐ”ŃŃŃ ĐżĐŸŃĐ»Đ”ĐŽĐŸĐČĐ°ŃДлŃĐœŃĐč ĐŸĐżĐ”ŃĐ°ŃĐŸŃ ĐœĐ°Đ·ĐœĐ°ŃĐ”ĐœĐžŃ: A <= reject 5 ns inertial '1' after 8 ns; ĐŃĐ”ŃĐ”ĐŽŃ ĐŽŃĐ°ĐčĐČĐ”ŃĐ° ĐŽĐŸ ĐČŃĐżĐŸĐ»ĐœĐ”ĐœĐžŃ ĐŸĐżĐ”ŃĐ°ŃĐŸŃĐ° '1'@18 ns ĐĐŸĐČĐŸĐ” Đ·ĐœĐ°ŃĐ”ĐœĐžĐ” '1'@11 ns 'X'@12 ns '1'@14 ns '0'@15 ns '1'@16 ns '1'@17 ns '1'@20 ns '0'@25 ns ĐŃŃĐ°ŃŃŃŃ ĐŃŃĐ°ŃŃŃŃ ĐŁĐŽĐ°Đ»ŃŃŃŃŃ ĐĐœŃĐ”ŃĐČĐ°Đ» ĐŸŃŃĐ°Đ¶Đ”ĐœĐžŃ ŃĐžĐłĐœĐ°Đ»ĐŸĐČ (13 ns -- 18 ns) ĐŃĐ”ŃĐ”ĐŽŃ ĐŽŃĐ°ĐčĐČĐ”ŃĐ° ĐżĐŸŃлД ĐČŃĐżĐŸĐ»ĐœĐ”ĐœĐžŃ ĐŸĐżĐ”ŃĐ°ŃĐŸŃĐ° '1'@11 ns 'X'@12 ns '1'@16 ns '1'@17 ns ' 1 '@18 ns 15 Đ„Đ°Ń Đ°ĐœĐŸĐČĐ° Đ.Đ, ĐșĐ°Ń.ĐĐĐĐą, Đ„ĐĐŁĐ Đ, e-mail: hahanova@mail.ru 09.02.2011

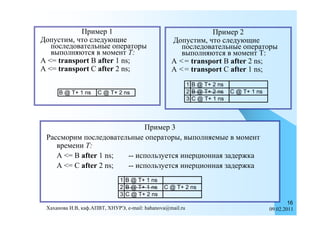

- 16. ĐŃĐžĐŒĐ”Ń 1 ĐŃĐžĐŒĐ”Ń 2 ĐĐŸĐżŃŃŃĐžĐŒ, ŃŃĐŸ ŃлДЎŃŃŃОД ĐĐŸĐżŃŃŃĐžĐŒ, ŃŃĐŸ ŃлДЎŃŃŃОД ĐżĐŸŃĐ»Đ”ĐŽĐŸĐČĐ°ŃДлŃĐœŃĐ” ĐŸĐżĐ”ŃĐ°ŃĐŸŃŃ ĐżĐŸŃĐ»Đ”ĐŽĐŸĐČĐ°ŃДлŃĐœŃĐ” ĐŸĐżĐ”ŃĐ°ŃĐŸŃŃ ĐČŃĐżĐŸĐ»ĐœŃŃŃŃŃ ĐČ ĐŒĐŸĐŒĐ”ĐœŃ T: ĐČŃĐżĐŸĐ»ĐœŃŃŃŃŃ ĐČ ĐŒĐŸĐŒĐ”ĐœŃ T: A <= transport B after 1 ns; A <= transport B after 2 ns; A <= transport C after 2 ns; A <= transport C after 1 ns; 1 B @ T+ 2 ns B @ T+ 1 ns C @ T+ 2 ns 2 B @ T+ 2 ns C @ T+ 1 ns 3 C @ T+ 1 ns ĐŃĐžĐŒĐ”Ń 3 Đ Đ°ŃŃĐŒĐŸŃĐžĐŒ ĐżĐŸŃĐ»Đ”ĐŽĐŸĐČĐ°ŃДлŃĐœŃĐ” ĐŸĐżĐ”ŃĐ°ŃĐŸŃŃ, ĐČŃĐżĐŸĐ»ĐœŃĐ”ĐŒŃĐ” ĐČ ĐŒĐŸĐŒĐ”ĐœŃ ĐČŃĐ”ĐŒĐ”ĐœĐž T: A <= B after 1 ns; -- ĐžŃĐżĐŸĐ»ŃĐ·ŃĐ”ŃŃŃ ĐžĐœĐ”ŃŃĐžĐŸĐœĐœĐ°Ń Đ·Đ°ĐŽĐ”ŃжĐșĐ° A <= C after 2 ns; -- ĐžŃĐżĐŸĐ»ŃĐ·ŃĐ”ŃŃŃ ĐžĐœĐ”ŃŃĐžĐŸĐœĐœĐ°Ń Đ·Đ°ĐŽĐ”ŃжĐșĐ° 1 B @ T+ 1 ns 2 B @ T+ 1 ns C @ T+ 2 ns 3 C @ T+ 2 ns 16 Đ„Đ°Ń Đ°ĐœĐŸĐČĐ° Đ.Đ, ĐșĐ°Ń.ĐĐĐĐą, Đ„ĐĐŁĐ Đ, e-mail: hahanova@mail.ru 09.02.2011

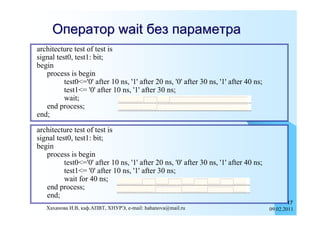

- 17. ĐпДŃĐ°ŃĐŸŃ wait бДз паŃĐ°ĐŒĐ”ŃŃĐ° architecture test of test is signal test0, test1: bit; begin process is begin test0<='0' after 10 ns, '1' after 20 ns, '0' after 30 ns, '1' after 40 ns; test1<= '0' after 10 ns, '1' after 30 ns; wait; end process; end; architecture test of test is signal test0, test1: bit; begin process is begin test0<='0' after 10 ns, '1' after 20 ns, '0' after 30 ns, '1' after 40 ns; test1<= '0' after 10 ns, '1' after 30 ns; wait for 40 ns; end process; end; 17 Đ„Đ°Ń Đ°ĐœĐŸĐČĐ° Đ.Đ, ĐșĐ°Ń.ĐĐĐĐą, Đ„ĐĐŁĐ Đ, e-mail: hahanova@mail.ru 09.02.2011

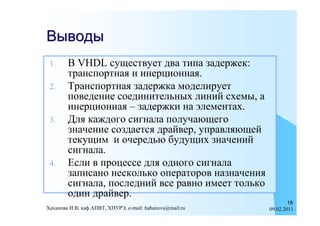

- 18. ĐŃĐČĐŸĐŽŃ 1. Đ VHDL ŃŃŃĐ”ŃŃĐČŃĐ”Ń ĐŽĐČĐ° ŃОпа Đ·Đ°ĐŽĐ”ŃжДĐș: ŃŃĐ°ĐœŃĐżĐŸŃŃĐœĐ°Ń Đž ĐžĐœĐ”ŃŃĐžĐŸĐœĐœĐ°Ń. 2. ĐąŃĐ°ĐœŃĐżĐŸŃŃĐœĐ°Ń Đ·Đ°ĐŽĐ”ŃжĐșĐ° ĐŒĐŸĐŽĐ”Đ»ĐžŃŃĐ”Ń ĐżĐŸĐČĐ”ĐŽĐ”ĐœĐžĐ” ŃĐŸĐ”ĐŽĐžĐœĐžŃДлŃĐœŃŃ Đ»ĐžĐœĐžĐč ŃŃ Đ”ĐŒŃ, Đ° ĐžĐœĐ”ŃŃĐžĐŸĐœĐœĐ°Ń â Đ·Đ°ĐŽĐ”ŃжĐșĐž ĐœĐ° ŃĐ»Đ”ĐŒĐ”ĐœŃĐ°Ń . 3. ĐĐ»Ń ĐșĐ°Đ¶ĐŽĐŸĐłĐŸ ŃĐžĐłĐœĐ°Đ»Đ° ĐżĐŸĐ»ŃŃĐ°ŃŃĐ”ĐłĐŸ Đ·ĐœĐ°ŃĐ”ĐœĐžĐ” ŃĐŸĐ·ĐŽĐ°Đ”ŃŃŃ ĐŽŃĐ°ĐčĐČĐ”Ń, ŃĐżŃĐ°ĐČĐ»ŃŃŃĐ”Đč ŃĐ”ĐșŃŃĐžĐŒ Đž ĐŸŃĐ”ŃДЎŃŃ Đ±ŃĐŽŃŃĐžŃ Đ·ĐœĐ°ŃĐ”ĐœĐžĐč ŃĐžĐłĐœĐ°Đ»Đ°. 4. ĐŃлО ĐČ ĐżŃĐŸŃĐ”ŃŃĐ” ĐŽĐ»Ń ĐŸĐŽĐœĐŸĐłĐŸ ŃĐžĐłĐœĐ°Đ»Đ° запОŃĐ°ĐœĐŸ ĐœĐ”ŃĐșĐŸĐ»ŃĐșĐŸ ĐŸĐżĐ”ŃĐ°ŃĐŸŃĐŸĐČ ĐœĐ°Đ·ĐœĐ°ŃĐ”ĐœĐžŃ ŃĐžĐłĐœĐ°Đ»Đ°, ĐżĐŸŃĐ»Đ”ĐŽĐœĐžĐč ĐČŃĐ” ŃĐ°ĐČĐœĐŸ ĐžĐŒĐ”Đ”Ń ŃĐŸĐ»ŃĐșĐŸ ĐŸĐŽĐžĐœ ĐŽŃĐ°ĐčĐČĐ”Ń. 18 Đ„Đ°Ń Đ°ĐœĐŸĐČĐ° Đ.Đ, ĐșĐ°Ń.ĐĐĐĐą, Đ„ĐĐŁĐ Đ, e-mail: hahanova@mail.ru 09.02.2011

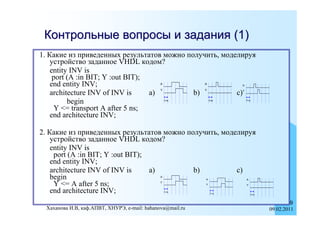

- 19. ĐĐŸĐœŃŃĐŸĐ»ŃĐœŃĐ” ĐČĐŸĐżŃĐŸŃŃ Đž Đ·Đ°ĐŽĐ°ĐœĐžŃ (1) 1. ĐĐ°ĐșОД Оз ĐżŃĐžĐČĐ”ĐŽĐ”ĐœĐœŃŃ ŃДзŃĐ»ŃŃĐ°ŃĐŸĐČ ĐŒĐŸĐ¶ĐœĐŸ ĐżĐŸĐ»ŃŃĐžŃŃ, ĐŒĐŸĐŽĐ”Đ»ĐžŃŃŃ ŃŃŃŃĐŸĐčŃŃĐČĐŸ Đ·Đ°ĐŽĐ°ĐœĐœĐŸĐ” VHDL ĐșĐŸĐŽĐŸĐŒ? entity INV is port (A :in BIT; Y :out BIT); end entity INV; A A A architecture INV of INV is a) b) c) Y Y Y begin 5 ns 5 ns 5 ns Y <= transport A after 5 ns; end architecture INV; 2. ĐĐ°ĐșОД Оз ĐżŃĐžĐČĐ”ĐŽĐ”ĐœĐœŃŃ ŃДзŃĐ»ŃŃĐ°ŃĐŸĐČ ĐŒĐŸĐ¶ĐœĐŸ ĐżĐŸĐ»ŃŃĐžŃŃ, ĐŒĐŸĐŽĐ”Đ»ĐžŃŃŃ ŃŃŃŃĐŸĐčŃŃĐČĐŸ Đ·Đ°ĐŽĐ°ĐœĐœĐŸĐ” VHDL ĐșĐŸĐŽĐŸĐŒ? entity INV is port (A :in BIT; Y :out BIT); end entity INV; architecture INV of INV is a) b) c) begin A A A Y <= A after 5 ns; Y Y Y end architecture INV; 5 ns 5 ns 5 ns 19 Đ„Đ°Ń Đ°ĐœĐŸĐČĐ° Đ.Đ, ĐșĐ°Ń.ĐĐĐĐą, Đ„ĐĐŁĐ Đ, e-mail: hahanova@mail.ru 09.02.2011

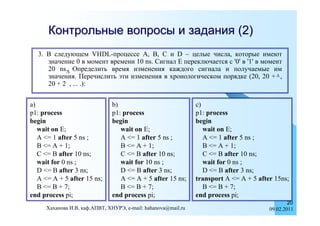

- 20. ĐĐŸĐœŃŃĐŸĐ»ŃĐœŃĐ” ĐČĐŸĐżŃĐŸŃŃ Đž Đ·Đ°ĐŽĐ°ĐœĐžŃ (2) 3. Đ ŃлДЎŃŃŃĐ”ĐŒ VHDL-ĐżŃĐŸŃĐ”ŃŃĐ” A, B, C Đž D â ŃДлŃĐ” ŃĐžŃла, ĐșĐŸŃĐŸŃŃĐ” ĐžĐŒĐ”ŃŃ Đ·ĐœĐ°ŃĐ”ĐœĐžĐ” 0 ĐČ ĐŒĐŸĐŒĐ”ĐœŃ ĐČŃĐ”ĐŒĐ”ĐœĐž 10 ns. ĐĄĐžĐłĐœĐ°Đ» E пДŃĐ”ĐșĐ»ŃŃĐ°Đ”ŃŃŃ Ń '0' ĐČ '1' ĐČ ĐŒĐŸĐŒĐ”ĐœŃ 20 ns.ï ĐĐżŃДЎДлОŃŃ ĐČŃĐ”ĐŒŃ ĐžĐ·ĐŒĐ”ĐœĐ”ĐœĐžŃ ĐșĐ°Đ¶ĐŽĐŸĐłĐŸ ŃĐžĐłĐœĐ°Đ»Đ° Đž ĐżĐŸĐ»ŃŃĐ°Đ”ĐŒŃĐ” ĐžĐŒ Đ·ĐœĐ°ŃĐ”ĐœĐžŃ. ĐĐ”ŃĐ”ŃĐžŃлОŃŃ ŃŃĐž ĐžĐ·ĐŒĐ”ĐœĐ”ĐœĐžŃ ĐČ Ń ŃĐŸĐœĐŸĐ»ĐŸĐłĐžŃĐ”ŃĐșĐŸĐŒ ĐżĐŸŃŃĐŽĐșĐ” (20, 20 + ï , 20 + 2 , ... .): a) b) c) p1: process p1: process p1: process begin begin begin wait on E; wait on E; wait on E; A <= 1 after 5 ns ; A <= 1 after 5 ns ; A <= 1 after 5 ns ; B <= A + 1; B <= A + 1; B <= A + 1; C <= B after 10 ns; C <= B after 10 ns; C <= B after 10 ns; wait for 0 ns ; wait for 10 ns ; wait for 0 ns ; D <= B after 3 ns; D <= B after 3 ns; D <= B after 3 ns; A <= A + 5 after 15 ns; A <= A + 5 after 15 ns; transport A <= A + 5 after 15ns; B <= B + 7; B <= B + 7; B <= B + 7; end process pi; end process pi; end process pi; 20 Đ„Đ°Ń Đ°ĐœĐŸĐČĐ° Đ.Đ, ĐșĐ°Ń.ĐĐĐĐą, Đ„ĐĐŁĐ Đ, e-mail: hahanova@mail.ru 09.02.2011

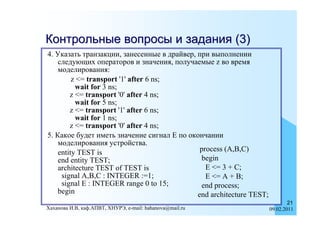

- 21. ĐĐŸĐœŃŃĐŸĐ»ŃĐœŃĐ” ĐČĐŸĐżŃĐŸŃŃ Đž Đ·Đ°ĐŽĐ°ĐœĐžŃ (3) 4. ĐŁĐșĐ°Đ·Đ°ŃŃ ŃŃĐ°ĐœĐ·Đ°ĐșŃОО, Đ·Đ°ĐœĐ”ŃĐ”ĐœĐœŃĐ” ĐČ ĐŽŃĐ°ĐčĐČĐ”Ń, ĐżŃĐž ĐČŃĐżĐŸĐ»ĐœĐ”ĐœĐžĐž ŃлДЎŃŃŃĐžŃ ĐŸĐżĐ”ŃĐ°ŃĐŸŃĐŸĐČ Đž Đ·ĐœĐ°ŃĐ”ĐœĐžŃ, ĐżĐŸĐ»ŃŃĐ°Đ”ĐŒŃĐ” z ĐČĐŸ ĐČŃĐ”ĐŒŃ ĐŒĐŸĐŽĐ”Đ»ĐžŃĐŸĐČĐ°ĐœĐžŃ: z <= transport '1' after 6 ns; wait for 3 ns; z <= transport '0' after 4 ns; wait for 5 ns; z <= transport '1' after 6 ns; wait for 1 ns; z <= transport '0' after 4 ns; 5. ĐĐ°ĐșĐŸĐ” бŃĐŽĐ”Ń ĐžĐŒĐ”ŃŃ Đ·ĐœĐ°ŃĐ”ĐœĐžĐ” ŃĐžĐłĐœĐ°Đ» Đ ĐżĐŸ ĐŸĐșĐŸĐœŃĐ°ĐœĐžĐž ĐŒĐŸĐŽĐ”Đ»ĐžŃĐŸĐČĐ°ĐœĐžŃ ŃŃŃŃĐŸĐčŃŃĐČĐ°. entity TEST is process (A,B,C) end entity TEST; begin architecture TEST of TEST is E <= 3 + C; signal A,B,C : INTEGER :=1; E <= A + B; signal E : INTEGER range 0 to 15; end process; begin end architecture TEST; 21 Đ„Đ°Ń Đ°ĐœĐŸĐČĐ° Đ.Đ, ĐșĐ°Ń.ĐĐĐĐą, Đ„ĐĐŁĐ Đ, e-mail: hahanova@mail.ru 09.02.2011

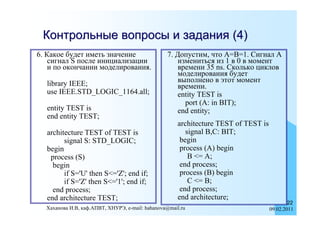

- 22. ĐĐŸĐœŃŃĐŸĐ»ŃĐœŃĐ” ĐČĐŸĐżŃĐŸŃŃ Đž Đ·Đ°ĐŽĐ°ĐœĐžŃ (4) 6. ĐĐ°ĐșĐŸĐ” бŃĐŽĐ”Ń ĐžĐŒĐ”ŃŃ Đ·ĐœĐ°ŃĐ”ĐœĐžĐ” 7. ĐĐŸĐżŃŃŃĐžĐŒ, ŃŃĐŸ A=B=1. CĐžĐłĐœĐ°Đ» A ŃĐžĐłĐœĐ°Đ» S ĐżĐŸŃлД ĐžĐœĐžŃОалОзаŃОО ĐžĐ·ĐŒĐ”ĐœĐžŃŃŃŃ ĐžĐ· 1 ĐČ 0 ĐČ ĐŒĐŸĐŒĐ”ĐœŃ Đž ĐżĐŸ ĐŸĐșĐŸĐœŃĐ°ĐœĐžĐž ĐŒĐŸĐŽĐ”Đ»ĐžŃĐŸĐČĐ°ĐœĐžŃ. ĐČŃĐ”ĐŒĐ”ĐœĐž 35 ns. ĐĄĐșĐŸĐ»ŃĐșĐŸ ŃĐžĐșĐ»ĐŸĐČ ĐŒĐŸĐŽĐ”Đ»ĐžŃĐŸĐČĐ°ĐœĐžŃ Đ±ŃĐŽĐ”Ń library IEEE; ĐČŃĐżĐŸĐ»ĐœĐ”ĐœĐŸ ĐČ ŃŃĐŸŃ ĐŒĐŸĐŒĐ”ĐœŃ ĐČŃĐ”ĐŒĐ”ĐœĐž. use IEEE.STD_LOGIC_1164.all; entity TEST is port (A: in BIT); entity TEST is end entity; end entity TEST; architecture TEST of TEST is architecture TEST of TEST is signal B,C: BIT; signal S: STD_LOGIC; begin begin process (A) begin process (S) B <= A; begin end process; if S='U' then S<='Z'; end if; process (B) begin if S='Z' then S<='1'; end if; C <= B; end process; end process; end architecture TEST; end architecture; 22 Đ„Đ°Ń Đ°ĐœĐŸĐČĐ° Đ.Đ, ĐșĐ°Ń.ĐĐĐĐą, Đ„ĐĐŁĐ Đ, e-mail: hahanova@mail.ru 09.02.2011

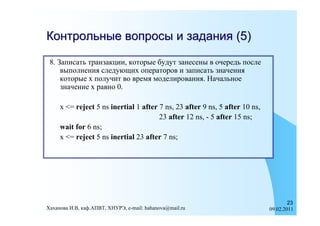

- 23. ĐĐŸĐœŃŃĐŸĐ»ŃĐœŃĐ” ĐČĐŸĐżŃĐŸŃŃ Đž Đ·Đ°ĐŽĐ°ĐœĐžŃ (5) 8. ĐапОŃĐ°ŃŃ ŃŃĐ°ĐœĐ·Đ°ĐșŃОО, ĐșĐŸŃĐŸŃŃĐ” бŃĐŽŃŃ Đ·Đ°ĐœĐ”ŃĐ”ĐœŃ ĐČ ĐŸŃĐ”ŃĐ”ĐŽŃ ĐżĐŸŃлД ĐČŃĐżĐŸĐ»ĐœĐ”ĐœĐžŃ ŃлДЎŃŃŃĐžŃ ĐŸĐżĐ”ŃĐ°ŃĐŸŃĐŸĐČ Đž запОŃĐ°ŃŃ Đ·ĐœĐ°ŃĐ”ĐœĐžŃ ĐșĐŸŃĐŸŃŃĐ” x ĐżĐŸĐ»ŃŃĐžŃ ĐČĐŸ ĐČŃĐ”ĐŒŃ ĐŒĐŸĐŽĐ”Đ»ĐžŃĐŸĐČĐ°ĐœĐžŃ. ĐĐ°ŃĐ°Đ»ŃĐœĐŸĐ” Đ·ĐœĐ°ŃĐ”ĐœĐžĐ” x ŃĐ°ĐČĐœĐŸ 0. x <= reject 5 ns inertial 1 after 7 ns, 23 after 9 ns, 5 after 10 ns, 23 after 12 ns, - 5 after 15 ns; wait for 6 ns; x <= reject 5 ns inertial 23 after 7 ns; 23 Đ„Đ°Ń Đ°ĐœĐŸĐČĐ° Đ.Đ, ĐșĐ°Ń.ĐĐĐĐą, Đ„ĐĐŁĐ Đ, e-mail: hahanova@mail.ru 09.02.2011

- 24. ĐŃĐČĐ”ŃŃ 4. 24 Đ„Đ°Ń Đ°ĐœĐŸĐČĐ° Đ.Đ, ĐșĐ°Ń.ĐĐĐĐą, Đ„ĐĐŁĐ Đ, e-mail: hahanova@mail.ru 09.02.2011

![ĐąŃĐ°ĐœŃĐżĐŸŃŃĐœĐ°Ń Đž ĐžĐœĐ”ŃŃĐžĐŸĐœĐœĐ°Ń Đ·Đ°ĐŽĐ”ŃжĐșĐž (1)

VHDL ĐżŃĐ”ĐŽĐ»Đ°ĐłĐ°Đ”Ń ĐŽĐČĐ° ŃОпа Đ·Đ°ĐŽĐ”ŃжДĐș: ŃŃĐ°ĐœŃĐżĐŸŃŃĐœŃŃ Đž

ĐžĐœĐ”ŃŃĐžĐŸĐœĐœŃŃ.

ï ĐąŃĐ°ĐœŃĐżĐŸŃŃĐœĐ°Ń ŃĐŸĐŸŃĐČĐ”ŃŃŃĐČŃĐ”Ń ĐŒĐŸĐŽĐ”Đ»Đž Đ·Đ°ĐŽĐ”ŃжДĐș ĐœĐ°

ĐżŃĐŸĐČĐŸĐŽĐœĐžĐșĐ°Ń

ŃŃ

Đ”ĐŒŃ. ĐŃŃ

ĐŸĐŽĐœĐŸĐč ŃĐžĐłĐœĐ°Đ» ĐżĐŸĐČŃĐŸŃŃĐ”Ń ĐČ ŃŃĐŸĐŒ

ŃĐ»ŃŃĐ°Đ” ŃĐŸŃĐŒŃ ĐČŃ

ĐŸĐŽĐœĐŸĐłĐŸ ŃĐžĐłĐœĐ°Đ»Đ° Ń Đ·Đ°ĐŽĐ”ŃжĐșĐŸĐč ĐœĐ° ŃĐșĐ°Đ·Đ°ĐœĐœĐŸĐ”

ĐČŃĐ”ĐŒŃ.

ĐĄĐžĐœŃĐ°ĐșŃĐžŃ:

signal_name <= transport expression after delay-time

ï ĐĐœĐ”ŃŃĐžĐŸĐœĐœĐ°Ń ĐŒĐŸĐŽĐ”Đ»ĐžŃŃĐ”Ń Đ·Đ°ĐŽĐ”ŃжĐșŃ ĐœĐ° ĐČĐ”ĐœŃОлŃŃ

ОлО ĐŽŃŃгОŃ

ŃŃŃŃĐŸĐčŃŃĐČĐ°Ń

, ĐœĐ” ĐżŃĐŸĐżŃŃĐșĐ°ŃŃĐžŃ

ĐșĐŸŃĐŸŃĐșОД ĐžĐŒĐżŃĐ»ŃŃŃ

ĐČŃ

ĐŸĐŽĐœĐŸĐłĐŸ ŃĐžĐłĐœĐ°Đ»Đ° ĐœĐ° ĐČŃŃ

ĐŸĐŽ. ĐŃĐŸ Đ·Đ°ĐŽĐ”ŃжĐșĐ° ĐžŃĐżĐŸĐ»ŃĐ·ŃĐ”ŃŃŃ ĐżĐŸ

ŃĐŒĐŸĐ»ŃĐ°ĐœĐžŃ.

ĐĄĐžĐœŃĐ°ĐșŃĐžŃ:

signal_name <= reject pulse-width [ inertial ] expression after

delay-time

4

Đ„Đ°Ń

Đ°ĐœĐŸĐČĐ° Đ.Đ, ĐșĐ°Ń.ĐĐĐĐą, Đ„ĐĐŁĐ Đ, e-mail: hahanova@mail.ru 09.02.2011](https://image.slidesharecdn.com/201105-110209155702-phpapp01/85/2011-05-4-320.jpg)