íë§ĩ 20a 28335

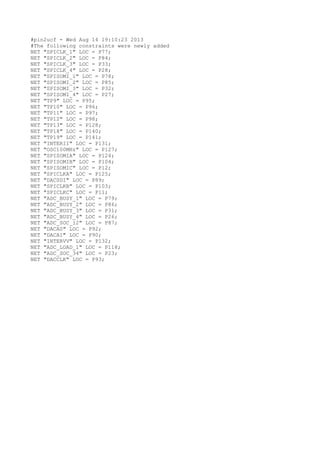

- 1. #pin2ucf - Wed Aug 14 19:10:23 2013 #The following constraints were newly added NET "SPICLK_1" LOC = P77; NET "SPICLK_2" LOC = P84; NET "SPICLK_3" LOC = P33; NET "SPICLK_4" LOC = P28; NET "SPISOMI_1" LOC = P78; NET "SPISOMI_2" LOC = P85; NET "SPISOMI_3" LOC = P32; NET "SPISOMI_4" LOC = P27; NET "TP9" LOC = P95; NET "TP10" LOC = P96; NET "TP11" LOC = P97; NET "TP12" LOC = P98; NET "TP13" LOC = P128; NET "TP18" LOC = P140; NET "TP19" LOC = P141; NET "INTERII" LOC = P131; NET "OSC100MHz" LOC = P127; NET "SPISOMIA" LOC = P124; NET "SPISOMIB" LOC = P104; NET "SPISOMIC" LOC = P12; NET "SPICLKA" LOC = P125; NET "DACSDI" LOC = P89; NET "SPICLKB" LOC = P103; NET "SPICLKC" LOC = P11; NET "ADC_BUSY_1" LOC = P79; NET "ADC_BUSY_2" LOC = P86; NET "ADC_BUSY_3" LOC = P31; NET "ADC_BUSY_4" LOC = P26; NET "ADC_SOC_12" LOC = P87; NET "DACA0" LOC = P92; NET "DACA1" LOC = P90; NET "INTERVV" LOC = P132; NET "ADC_LOAD_1" LOC = P118; NET "ADC_SOC_34" LOC = P23; NET "DACCLK" LOC = P93;