Bthesis - A High-speed and Portable FPGA Accelerator

- 1. USB3.0ĮėŠAż╬Ė▀╦┘żŪź▌®`ź┐źųźļż╩ FPGAźóź»ź╗źķźņ®`ź┐ 2015/02/16 ŲĮ│╔26─ĻČ╚ūõśI蹊┐░k▒Ē╗ß @S422 B2: ėŗ╦ŃÖCźĘź╣źŲźÓ?╝»Ęe╗ž┬Ę(10:55-11:09) ░k▒Ē7Ęų + ┘|ę╔ÅĻ┤7Ęų ¢|Š®╣żśI┤¾č¦ ╣żč¦▓┐ Ūķł¾╣żč¦┐Ų ╝¬×ü蹊┐╩ę 11_03601 Š╩Š« ū┴šµ

- 3. FPGAż╚ż╬ĮėŠAźżź¾ź┐®`źšź¦®`ź╣▒╚▌^ ?USB3.0żŽUART, USB2.0żĶżĻżŽłRĄ╣Ą─ż╦╦┘żż ?PCI Expressżõ10Gbps EthernetżĶżĻżŽ▀Wżż ?żĘż½żĘĮėŠAż¼ĘŪ│Żż╦╚▌ęūżŪŻ¼śöĪ®ż╩ŁhŠ│żŪ╩╣ż©żļ 2 ĮėŠAĘĮĘ© USB3.0 USB2.0 UART PCI Express Ethernet ūŅĖ▀╦┘Č╚(└ĒšōéÄ) 5Gbps 480Mbps ╩²Mbps 8GB/s@2.0 x8 1GB/s@2.0 x1 1Gbps@GbE 10Gbps@XGbE ─┌╩i/═ŌĖČ ═ŌĖČ ═ŌĖČ ═ŌĖČ ─┌╩i ═ŌĖČ ūŅą┬PCżŪż╬Ųš╝░┬╩ Ī Ī Ī┴ Ī„ Ī┴(XGbE) ź█ź├ź╚ź╣ź’ź├źū Ī Ī Ī┴ Ī Ī źąź╣źčź’®` 900mA,5V 500mA,5V Ī┴ 25/75W@x16 Ī┴

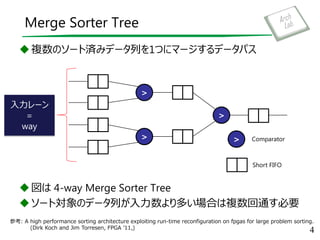

- 5. Merge Sorter Tree ?č}╩²ż╬źĮ®`ź╚£gż▀źŪ®`ź┐┴ąż“1ż─ż╦ź▐®`źĖż╣żļźŪ®`ź┐źčź╣ ?ćĒżŽ 4-way Merge Sorter Tree ?źĮ®`ź╚īØŽ¾ż╬źŪ®`ź┐┴ąż¼╚ļ┴”╩²żĶżĻČÓżżł÷║ŽżŽč}╩²╗ž═©ż╣▒žę¬ 4 ▓╬┐╝: A high performance sorting architecture exploiting run-time reconfiguration on fpgas for large problem sorting. (Dirk Koch and Jim Torresen, FPGA Ī»11,) > > > > Comparator Short FIFO ╚ļ┴”źņ®`ź¾ = way

- 7. īgū░?įuü² ?īgū░ ?8-way Merge Sorter Tree ż“īgū░ ?źŽ®`ź╔ź”ź¦źóėø╩÷čįšZ: Verilog HDL ?šō└Ē║Ž│╔: Xilinx ISE 14.7 ?H/W╩╣ė├┴┐: Block RAMżŽ20%, SliceżŽ19% (8-wayīgū░Ģr) ?FPGA: Xilinx Artix-7 XC7A100T @ 100MHz ?DRAM: DDR3 256MB @ 400MHz ?įuü² ?32bitż╬intą═š¹╩²32MéĆż╬źĮ®`źŲźŻź¾ź░ż╬īgąąĢrķgż“ėŗ£y Ī¾USB3.0ż“ĮķżĘżŲFPGAźóź»ź╗źķźņ®`ź┐ż╦źŪ®`ź┐ż“╦═ą┼Ż¼ĮY╣¹ż“╩▄ą┼ Ī¾ź█ź╣ź╚PCżŪż╬ź▐®`źĖźĮ®`ź╚ż╚▒╚▌^ ?ź▌®`ź┐źėźĻźŲźŻįuü²ż╬ż┐żßŻ¼4ż─ż╬įuü²ŁhŠ│ż“ė├ęŌ Ī¾USB3.0ŁhŠ│Ż¼USB2.0ŁhŠ│ Ī¾źŪź╣ź»ź╚ź├źūPCż╚źķź├źūź╚ź├źūPC 6

- 8. 4ĘNŅÉż╬įuü²ŁhŠ│ ©C Computer A 7 Core i7-3770K @3.50GHz 16GB DDR3 Memory Supports USB3.0 High Performance!

- 9. 4ĘNŅÉż╬įuü²ŁhŠ│ ©C Computer B 8 Supports USB3.0 Core i3-4010U @1.70GHz 4GB DDR3 Memory Portable!

- 10. 4ĘNŅÉż╬įuü²ŁhŠ│ ©C Computer C 9 Only supports USB2.0 Core i7-870 @2.93GHz 4GB DDR3 Memory

- 11. 4ĘNŅÉż╬įuü²ŁhŠ│ ©C Computer D 10 Core Duo T2400 @1.83GHz 1GB DDR2 Memory Only supports USB2.0

- 12. įuü²©Dintą═32MéĆż╬źĮ®`źŲźŻź¾ź░ 11 0 2 4 6 8 10 12 CPU FPGA 8-way CPU FPGA 8-way CPU FPGA 8-way CPU FPGA 8-way Computer A Computer B Computer C Computer D ElapsedTime[s] Data Transfer Sorting only USB3.0 USB2.0

- 13. 0 2 4 6 8 10 12 CPU FPGA 8-way CPU FPGA 8-way CPU FPGA 8-way CPU FPGA 8-way Computer A Computer B Computer C Computer D ElapsedTime[s] Data Transfer Sorting only USB3.0 USB2.0 Ęų╬÷ 12 ąį─▄Ž“╔Ž▓╗┐╔─▄ ═©ą┼Ģrķg > CPUż╦ż¬ż▒żļźĮ®`źŲźŻź¾ź░Ģrķg

- 14. 0 2 4 6 8 10 12 CPU FPGA 8-way CPU FPGA 8-way CPU FPGA 8-way CPU FPGA 8-way Computer A Computer B Computer C Computer D ElapsedTime[s] Data Transfer Sorting only USB3.0 USB2.0 Ęų╬÷ 13 ═©ą┼Ģrķg ┤¾Ę∙£p USB3.0żŪ ąį─▄Ž“╔Ž

- 15. įuü² @USB3.0ŁhŠ│ 14 4.30 3.27 8.75 3.28 0 2 4 6 8 10 CPU FPGA 8-way CPU FPGA 8-way Computer A Computer B ElapsedTime[s] 2.66x Faster 1.31x Faster ?Merge Sorter Treeż“32-wayż╦ÆłÅłżĘComputer Aż╬CPU▒╚ 1.93▒Čż╬Ė▀╦┘╗»▀_│╔ śöĪ®ż╩ŁhŠ│żŪ ╩╣ż©żļ

- 16. ż▐ż╚żß?Į±ßßż╬šnŅ} ?ż▐ż╚żß ?USB3.0ĮėŠAż╬Ė▀╦┘żŪź▌®`ź┐źųźļż╩FPGAźóź»ź╗źķźņ®`ź┐ż“╠ß░Ė ?īØŽ¾źóźūźĻ: źĮ®`źŲźŻź¾ź░ ?USB2.0ŁhŠ│żŪżŽ╠ß░Ėż╣żļFPGAźóź»ź╗źķźņ®`ź┐ż“ė├żżżŲżŌąį─▄ż¼Ž“╔ŽżĘż╩żż ?USB3.0ŁhŠ│żŪżŽąį─▄ż¼Ž“╔Ž Ī¾źķź├źūź╚ź├źūPC▒╚2.66▒Č Ī¾źŪź╣ź»ź╚ź├źūPC▒╚1.31▒ČĪ·TreeÆłÅłĢr1.93▒Č ?Į±ßßż╬šnŅ} ?Merge Sorter Treeż“Ė³ż╦ÆłÅł ?╦¹ż╬źóźūźĻź▒®`źĘźńź¾ż╬Ė▀╦┘╗» Ī¾ź░źķźšäI└ĒŻ¼╗ŁŽ±äI└ĒŻ¼źŪ®`ź┐łR┐setcĪŁ 15

- 17. ░k▒Ē┬─Üs?ėĶČ© ?ļŖūėŪķł¾═©ą┼č¦╗ß蹊┐╗ß(RECONF) ░k▒Ē (2015/01/30) ?ĪĖUSB3.0ĮėŠAż╬╩ų▌XżŪĖ▀╦┘ż╩FPGAźóź»ź╗źķźņ®`ź┐Ī╣ ?Š╩Š« ū┴šµŻ¼ąĪ┴ų šÅŲĮŻ¼╝¬×ü ųtČ■ ?Ūķł¾äI└Ēč¦╗ß Ą┌77╗ž ╚½╣·┤¾╗ß ░k▒ĒėĶČ© (2015/03/18) ?ĪĖ╩ų▌Xż╩═ŌĖČż▒FPGAźóź»ź╗źķźņ®`ź┐ż╦żĶżļźĮ®`źŲźŻź¾ź░ż╬Ė▀╦┘╗»Ī╣ ?Š╩Š« ū┴šµŻ¼╝¬×ü ųtČ■ ?ARC 2015 POSTER SESSION (2015/04/15-17) ?Ī░A Challenge of Portable and High-speed FPGA AcceleratorĪ▒ ?Takuma USUI, Ryohei KOBAYASHI, Kenji KISE 16

![įuü²©Dintą═32MéĆż╬źĮ®`źŲźŻź¾ź░

11

0

2

4

6

8

10

12

CPU FPGA

8-way

CPU FPGA

8-way

CPU FPGA

8-way

CPU FPGA

8-way

Computer A Computer B Computer C Computer D

ElapsedTime[s]

Data Transfer

Sorting only

USB3.0

USB2.0](https://image.slidesharecdn.com/bthesisslideshare-150427060935-conversion-gate02/85/Bthesis-A-High-speed-and-Portable-FPGA-Accelerator-12-320.jpg)

![0

2

4

6

8

10

12

CPU FPGA

8-way

CPU FPGA

8-way

CPU FPGA

8-way

CPU FPGA

8-way

Computer A Computer B Computer C Computer D

ElapsedTime[s]

Data Transfer

Sorting only

USB3.0

USB2.0

Ęų╬÷

12

ąį─▄Ž“╔Ž▓╗┐╔─▄

═©ą┼Ģrķg > CPUż╦ż¬ż▒żļźĮ®`źŲźŻź¾ź░Ģrķg](https://image.slidesharecdn.com/bthesisslideshare-150427060935-conversion-gate02/85/Bthesis-A-High-speed-and-Portable-FPGA-Accelerator-13-320.jpg)

![0

2

4

6

8

10

12

CPU FPGA

8-way

CPU FPGA

8-way

CPU FPGA

8-way

CPU FPGA

8-way

Computer A Computer B Computer C Computer D

ElapsedTime[s]

Data Transfer

Sorting only

USB3.0

USB2.0

Ęų╬÷

13

═©ą┼Ģrķg

┤¾Ę∙£p

USB3.0żŪ

ąį─▄Ž“╔Ž](https://image.slidesharecdn.com/bthesisslideshare-150427060935-conversion-gate02/85/Bthesis-A-High-speed-and-Portable-FPGA-Accelerator-14-320.jpg)

![įuü² @USB3.0ŁhŠ│

14

4.30 3.27 8.75 3.28

0

2

4

6

8

10

CPU FPGA

8-way

CPU FPGA

8-way

Computer A Computer B

ElapsedTime[s] 2.66x

Faster

1.31x

Faster

?Merge Sorter Treeż“32-wayż╦ÆłÅłżĘComputer Aż╬CPU▒╚

1.93▒Čż╬Ė▀╦┘╗»▀_│╔

śöĪ®ż╩ŁhŠ│żŪ

╩╣ż©żļ](https://image.slidesharecdn.com/bthesisslideshare-150427060935-conversion-gate02/85/Bthesis-A-High-speed-and-Portable-FPGA-Accelerator-15-320.jpg)