Cache coherence

28 likes23,028 views

The document discusses cache coherence in multiprocessor systems. It describes the cache coherence problem that can arise when multiple processors have caches and can access shared memory. It then summarizes two primary hardware solutions: directory protocols which maintain information about which caches hold which memory lines; and snoopy cache protocols where cache controllers monitor bus traffic to maintain coherence without a directory. Finally it mentions a software-based solution relying on compiler analysis and operating system support.

1 of 8

Ad

Recommended

Memory Organization

Memory OrganizationKamal Acharya

Ěý

The document discusses the different types of memory in digital computers, including main memory, associative memory, cache memory, and virtual memory, detailing their organization, functions, and access methods. It explains the memory hierarchy, the role of auxiliary memory, and various mapping techniques for cache memory, such as associative, direct, and set-associative mapping. Additionally, the document covers memory addressing, data storage, and mechanisms like page replacement in virtual memory systems.Cache coherence problem and its solutions

Cache coherence problem and its solutionsMajid Saleem

Ěý

This document discusses cache coherence in shared memory multiprocessor systems. It defines cache coherence as ensuring changes to shared memory values are propagated throughout the system quickly. It describes two main approaches to maintaining cache coherence - software-based and hardware-based solutions. Hardware-based approaches can use either snooping or directory-based protocols. Snooping is used in low-end multiprocessors and involves broadcasting cache coherency messages on a shared bus. Directory-based protocols are used in higher-end systems and involve tracking the state of cached blocks in a directory.Opetating System Memory management

Opetating System Memory managementJohan Granados Montero

Ěý

Memory management handles allocation of memory to processes and tracks used and free memory. It uses techniques like paging, segmentation, and dynamic allocation from a heap. Paging maps logical addresses to physical pages, avoiding external fragmentation. Segmentation divides memory into logical segments of varying sizes. Dynamic allocation fulfills requests from the heap, managing free blocks and avoiding fragmentation and memory leaks.Interrupts

InterruptsUrwa Shanza

Ěý

The document discusses interrupts in a computer system. It defines an interrupt as a signal that breaks the normal sequence of program execution to handle an event that requires immediate attention, like input from a device. There are two main types of interrupts: hardware interrupts caused by external devices, and software interrupts caused by exceptional conditions in a program like division by zero. The document outlines how interrupts work, including how the processor saves the state of the interrupted program, services the interrupt, and then restores the original program context. It also discusses interrupt priorities and how interrupts can be disabled or deferred based on priority.8 memory management strategies

8 memory management strategiesDr. Loganathan R

Ěý

The document discusses different memory management strategies:

- Swapping allows processes to be swapped temporarily out of memory to disk, then back into memory for continued execution. This improves memory utilization but incurs long swap times.

- Contiguous memory allocation allocates processes into contiguous regions of physical memory using techniques like memory mapping and dynamic storage allocation with first-fit or best-fit. This can cause external and internal fragmentation over time.

- Paging permits the physical memory used by a process to be noncontiguous by dividing memory into pages and mapping virtual addresses to physical frames, allowing more efficient use of memory but requiring page tables for translation.Cache coherence

Cache coherencePriyam Pandey

Ěý

Cache coherence is an issue that arises in multiprocessing systems where multiple processors have cached copies of shared memory locations. If a processor modifies its local copy, it can create an inconsistent global view of memory.

There are two main approaches to maintaining cache coherence - snoopy bus protocols and directory schemes. Snoopy bus protocols use a shared bus for processors to monitor memory transactions and invalidate local copies when needed. Directory schemes track which processors are sharing each block of data using a directory structure.

One common snoopy protocol is MESI, which uses cache states of Modified, Exclusive, Shared, and Invalid to track the ownership of cache lines and ensure coherency is maintained when a line is modified.Memory management

Memory managementRajni Sirohi

Ěý

The document discusses memory management in operating systems. It covers key concepts like logical versus physical addresses, binding logical addresses to physical addresses, and different approaches to allocating memory like contiguous allocation. It also discusses dynamic storage allocation using a buddy system to merge adjacent free spaces, as well as compaction techniques to reduce external fragmentation by moving free memory blocks together. Memory management aims to efficiently share physical memory between processes using mechanisms like partitioning memory and enforcing protection boundaries.9 virtual memory management

9 virtual memory managementDr. Loganathan R

Ěý

Virtual memory management techniques allow processes to access memory in a virtual address space that is larger than the actual physical memory. There are three main techniques:

1. Demand paging only loads pages into memory when they are needed, reducing I/O and memory usage but increasing access time due to page faults.

2. Copy-on-write shares pages between processes until a page is modified, then it is copied to avoid overwriting another process's page.

3. Page replacement algorithms select victim pages to remove from memory and write to disk when new pages are needed. Least recently used is commonly used but not optimal.Operating systems system structures

Operating systems system structuresMukesh Chinta

Ěý

The document details the functions and services provided by operating systems, including handling user interactions through command-line and graphical user interfaces, managing resources, and facilitating communication between processes. It explains system calls as a method for applications to request services, and categorizes these calls into major groups such as process control, file manipulation, and device manipulation. Additionally, the document emphasizes the importance of security, resource allocation, and error handling within operating systems.Operating system structures

Operating system structuresMohd Arif

Ěý

This chapter discusses operating system structures and concepts. It describes the services operating systems provide to users and processes, such as user interfaces, program execution, I/O operations, file manipulation, communications, and error detection. It also discusses how operating systems ensure efficient resource sharing through resource allocation, accounting, protection and security. The chapter covers system calls, which are the programming interface to OS services, and how system calls are typically implemented and accessed through APIs rather than direct calls.Virtual memory management in Operating System

Virtual memory management in Operating SystemRashmi Bhat

Ěý

Virtual memory allows processes to execute without being completely loaded into physical memory. It abstracts memory into a large, uniform array that allows processes to easily share files and memory. With virtual memory, programs are no longer constrained by the amount of physical memory and more programs can run simultaneously with less I/O. Pages are loaded into memory on demand via demand paging to avoid loading unused pages. When a page fault occurs for an invalid page, it is paged into memory if valid. Common page replacement algorithms are FIFO, Optimal, and LRU which replace pages based on time since last use to make space for new pages on faults.Computer architecture virtual memory

Computer architecture virtual memoryMazin Alwaaly

Ěý

The document provides an overview of virtual memory, detailing its history, functionality, and key concepts such as paging and demand paging. It describes how virtual memory allows programs to run using a fraction of the physical memory capacity by swapping data in and out from a disk, enhancing multiprogramming capabilities and efficiency. Additionally, it addresses challenges in virtual memory implementation, such as thrashing, and discusses solutions like multilevel page tables and the use of translation lookaside buffers.Memory organization (Computer architecture)

Memory organization (Computer architecture)Sandesh Jonchhe

Ěý

Memory is organized in a hierarchy with different levels providing trade-offs between speed and cost.

- Cache memory sits between the CPU and main memory for fastest access.

- Main memory (RAM) is where active programs and data reside and is faster than auxiliary memory but more expensive.

- Auxiliary memory (disks, tapes) provides backup storage and is slower than main memory but larger and cheaper.

Virtual memory manages this hierarchy through address translation techniques like paging that map virtual addresses to physical locations, allowing programs to access more memory than physically available. When data is needed from auxiliary memory a page fault occurs and page replacement algorithms determine what data to remove from main memory.Parallel architecture

Parallel architectureMr SMAK

Ěý

This document discusses parallel computers and architectures. It defines parallel computers as collections of processing elements that cooperate and communicate to solve problems fast. It then examines questions about parallel computers, different types of parallelism, and opportunities for parallel computing in scientific and commercial applications. Finally, it discusses fundamental issues in parallel architectures, including naming, synchronization, latency and bandwidth, and different parallel frameworks and models like shared memory, message passing, and data parallelism.Parallel computing

Parallel computingVinay Gupta

Ěý

Parallel computing involves solving computational problems simultaneously using multiple processors. It can save time and money compared to serial computing and allow larger problems to be solved. Parallel programs break problems into discrete parts that can be solved concurrently on different CPUs. Shared memory parallel computers allow all processors to access a global address space, while distributed memory systems require communication between separate processor memories. Hybrid systems combine shared and distributed memory architectures.Cache memory

Cache memoryAnuj Modi

Ěý

Cache memory is a small, fast memory located between the CPU and main memory. It stores copies of frequently used instructions and data to accelerate access and improve performance. There are different mapping techniques for cache including direct mapping, associative mapping, and set associative mapping. When the cache is full, replacement algorithms like LRU and FIFO are used to determine which content to remove. The cache can write to main memory using either a write-through or write-back policy.Cache coherence

Cache coherenceShyam Krishna Khadka

Ěý

Cache coherence is a technique used in multiprocessing systems to maintain consistency between caches and shared memory. When a processor modifies a variable in its cache that is also stored in another processor's cache, inconsistency arises. There are three main techniques to maintain cache coherence: snoopy-based protocols invalidate or update other caches when a write is observed; directory-based protocols use a directory to control access to shared data and update or invalidate caches; and snarfing-based protocols allow caches to watch addresses and data to update copies when writes are seen. Cache coherence aims to ensure data consistency across caches for shared resources.Parallel processing

Parallel processingrajshreemuthiah

Ěý

The document provides an overview of parallel processing and multiprocessor systems. It discusses Flynn's taxonomy, which classifies computers as SISD, SIMD, MISD, or MIMD based on whether they process single or multiple instructions and data in parallel. The goals of parallel processing are to reduce wall-clock time and solve larger problems. Multiprocessor topologies include uniform memory access (UMA) and non-uniform memory access (NUMA) architectures.RAM and ROM Memory Overview

RAM and ROM Memory OverviewPankaj Khodifad

Ěý

This document provides an overview of different types of computer memory, including RAM, ROM, and hybrid memory. It describes the characteristics of SRAM and DRAM, the most common types of RAM memory. DRAM is cheaper and slower than SRAM, and must be periodically refreshed. The document outlines the evolution of DDR RAM standards and their internal structures. ROM includes mask ROM, PROM, EPROM, and is read-only memory that can be programmed during manufacture or special modes. Hybrid memory such as flash memory has qualities of both RAM and ROM.Cache Memory

Cache MemorySubid Biswas

Ěý

The document discusses cache memory and provides information on various aspects of cache memory including:

- Introduction to cache memory including its purpose and levels.

- Cache structure and organization including cache row entries, cache blocks, and mapping techniques.

- Performance of cache memory including factors like cycle count and hit ratio.

- Cache coherence in multiprocessor systems and coherence protocols.

- Synchronization mechanisms used in multiprocessor systems for cache coherence.

- Paging techniques used in cache memory including address translation using page tables and TLBs.

- Replacement algorithms used to determine which cache blocks to replace when the cache is full.Unit 5 Advanced Computer Architecture

Unit 5 Advanced Computer ArchitectureBalaji Vignesh

Ěý

This document provides an overview of hardware multithreading techniques including fine-grained, coarse-grained, and simultaneous multithreading. Fine-grained multithreading switches threads after every instruction to hide latency. Coarse-grained multithreading switches threads only after long stalls to avoid slowing individual threads. Simultaneous multithreading issues instructions from multiple threads each cycle to better utilize functional units.Linux Memory Management

Linux Memory ManagementSuvendu Kumar Dash

Ěý

The document provides an overview of the Linux operating system, detailing its components, such as the kernel, system libraries, and system utilities, as well as the user space and kernel space. It also discusses address translation, multithreading, and multiprocessing, including their benefits and various models. Ultimately, it highlights the parallel execution capabilities and efficiency improvements offered by multithreading in Linux.Multi processor scheduling

Multi processor schedulingShashank Kapoor

Ěý

The document discusses multi-processor scheduling, highlighting the complexity compared to single-processor scheduling and categorizing it into asymmetric and symmetric approaches. It addresses critical issues such as locking systems, shared data, cache coherence, and processor affinity, explaining their impact on performance and data consistency. Load balancing is also examined, outlining its importance in utilizing multiple processors effectively and describing methods like push and pull migration to distribute workloads.Symmetric multiprocessing

Symmetric multiprocessingMohammad Ali Khan

Ěý

This document discusses symmetric multiprocessing (SMP). It defines SMP as processing programs using multiple processors that share common operating system and memory. The key aspects of SMP are:

- Processors share memory and I/O bus or data path

- A single operating system controls all processors

- SMP architecture allows processors to access same memory simultaneously

- Advantages of SMP include improved performance, availability, ability to incrementally grow, and scaling

- Limitations include additional complexity in operating system and potential bottlenecking of master CPU.Cache coherence ppt

Cache coherence pptArendraSingh2

Ěý

This document discusses cache coherence in single and multiprocessor systems. It provides techniques to avoid inconsistencies between cache and main memory including write-through, write-back, and instruction caching. For multiprocessors, it discusses issues with sharing writable data, process migration, and I/O activity. Software solutions involve compiler and OS management while hardware uses coherence protocols like snoopy and directory protocols.Distributed Operating System_1

Distributed Operating System_1Dr Sandeep Kumar Poonia

Ěý

The document provides a comprehensive overview of distributed operating systems, covering topics such as design goals, inter-process communication, and synchronization methods. It outlines various operating system types, including mainframe, time-sharing, and real-time systems, alongside their features and management functions. Key concepts like process management, memory management, and networking are discussed in the context of their roles within operating systems, supported by specific examples and architectural considerations.Memory mapping

Memory mappingSnehalataAgasti

Ěý

Cache memory is located between the processor and main memory. It is smaller and faster than main memory. There are two types of cache memory policies - write-back and write-through. Mapping is a technique that maps CPU-generated memory addresses to cache lines. There are three types of mapping - direct, associative, and set associative. Direct mapping maps each main memory block to a single cache line using the formula: cache line number = main memory block number % number of cache lines. This can cause conflict misses.operating system structure

operating system structureWaseem Ud Din Farooqui

Ěý

The document discusses key components and concepts related to operating system structures. It describes common system components like process management, memory management, file management, I/O management, and more. It then provides more details on specific topics like the role of processes, main memory management, file systems, I/O systems, secondary storage, networking, protection systems, and command interpreters in operating systems. Finally, it discusses operating system services, system calls, and how parameters are passed between programs and the operating system.Lecture-7 Main Memroy.pptx

Lecture-7 Main Memroy.pptxAmanuelmergia

Ěý

Operating systems use main memory management techniques like paging and segmentation to allocate memory to processes efficiently. Paging divides both logical and physical memory into fixed-size pages. It uses a page table to map logical page numbers to physical frame numbers. This allows processes to be allocated non-contiguous physical frames. A translation lookaside buffer (TLB) caches recent page translations to improve performance by avoiding slow accesses to the page table in memory. Protection bits and valid/invalid bits ensure processes only access their allocated memory regions.More Related Content

What's hot (20)

Operating systems system structures

Operating systems system structuresMukesh Chinta

Ěý

The document details the functions and services provided by operating systems, including handling user interactions through command-line and graphical user interfaces, managing resources, and facilitating communication between processes. It explains system calls as a method for applications to request services, and categorizes these calls into major groups such as process control, file manipulation, and device manipulation. Additionally, the document emphasizes the importance of security, resource allocation, and error handling within operating systems.Operating system structures

Operating system structuresMohd Arif

Ěý

This chapter discusses operating system structures and concepts. It describes the services operating systems provide to users and processes, such as user interfaces, program execution, I/O operations, file manipulation, communications, and error detection. It also discusses how operating systems ensure efficient resource sharing through resource allocation, accounting, protection and security. The chapter covers system calls, which are the programming interface to OS services, and how system calls are typically implemented and accessed through APIs rather than direct calls.Virtual memory management in Operating System

Virtual memory management in Operating SystemRashmi Bhat

Ěý

Virtual memory allows processes to execute without being completely loaded into physical memory. It abstracts memory into a large, uniform array that allows processes to easily share files and memory. With virtual memory, programs are no longer constrained by the amount of physical memory and more programs can run simultaneously with less I/O. Pages are loaded into memory on demand via demand paging to avoid loading unused pages. When a page fault occurs for an invalid page, it is paged into memory if valid. Common page replacement algorithms are FIFO, Optimal, and LRU which replace pages based on time since last use to make space for new pages on faults.Computer architecture virtual memory

Computer architecture virtual memoryMazin Alwaaly

Ěý

The document provides an overview of virtual memory, detailing its history, functionality, and key concepts such as paging and demand paging. It describes how virtual memory allows programs to run using a fraction of the physical memory capacity by swapping data in and out from a disk, enhancing multiprogramming capabilities and efficiency. Additionally, it addresses challenges in virtual memory implementation, such as thrashing, and discusses solutions like multilevel page tables and the use of translation lookaside buffers.Memory organization (Computer architecture)

Memory organization (Computer architecture)Sandesh Jonchhe

Ěý

Memory is organized in a hierarchy with different levels providing trade-offs between speed and cost.

- Cache memory sits between the CPU and main memory for fastest access.

- Main memory (RAM) is where active programs and data reside and is faster than auxiliary memory but more expensive.

- Auxiliary memory (disks, tapes) provides backup storage and is slower than main memory but larger and cheaper.

Virtual memory manages this hierarchy through address translation techniques like paging that map virtual addresses to physical locations, allowing programs to access more memory than physically available. When data is needed from auxiliary memory a page fault occurs and page replacement algorithms determine what data to remove from main memory.Parallel architecture

Parallel architectureMr SMAK

Ěý

This document discusses parallel computers and architectures. It defines parallel computers as collections of processing elements that cooperate and communicate to solve problems fast. It then examines questions about parallel computers, different types of parallelism, and opportunities for parallel computing in scientific and commercial applications. Finally, it discusses fundamental issues in parallel architectures, including naming, synchronization, latency and bandwidth, and different parallel frameworks and models like shared memory, message passing, and data parallelism.Parallel computing

Parallel computingVinay Gupta

Ěý

Parallel computing involves solving computational problems simultaneously using multiple processors. It can save time and money compared to serial computing and allow larger problems to be solved. Parallel programs break problems into discrete parts that can be solved concurrently on different CPUs. Shared memory parallel computers allow all processors to access a global address space, while distributed memory systems require communication between separate processor memories. Hybrid systems combine shared and distributed memory architectures.Cache memory

Cache memoryAnuj Modi

Ěý

Cache memory is a small, fast memory located between the CPU and main memory. It stores copies of frequently used instructions and data to accelerate access and improve performance. There are different mapping techniques for cache including direct mapping, associative mapping, and set associative mapping. When the cache is full, replacement algorithms like LRU and FIFO are used to determine which content to remove. The cache can write to main memory using either a write-through or write-back policy.Cache coherence

Cache coherenceShyam Krishna Khadka

Ěý

Cache coherence is a technique used in multiprocessing systems to maintain consistency between caches and shared memory. When a processor modifies a variable in its cache that is also stored in another processor's cache, inconsistency arises. There are three main techniques to maintain cache coherence: snoopy-based protocols invalidate or update other caches when a write is observed; directory-based protocols use a directory to control access to shared data and update or invalidate caches; and snarfing-based protocols allow caches to watch addresses and data to update copies when writes are seen. Cache coherence aims to ensure data consistency across caches for shared resources.Parallel processing

Parallel processingrajshreemuthiah

Ěý

The document provides an overview of parallel processing and multiprocessor systems. It discusses Flynn's taxonomy, which classifies computers as SISD, SIMD, MISD, or MIMD based on whether they process single or multiple instructions and data in parallel. The goals of parallel processing are to reduce wall-clock time and solve larger problems. Multiprocessor topologies include uniform memory access (UMA) and non-uniform memory access (NUMA) architectures.RAM and ROM Memory Overview

RAM and ROM Memory OverviewPankaj Khodifad

Ěý

This document provides an overview of different types of computer memory, including RAM, ROM, and hybrid memory. It describes the characteristics of SRAM and DRAM, the most common types of RAM memory. DRAM is cheaper and slower than SRAM, and must be periodically refreshed. The document outlines the evolution of DDR RAM standards and their internal structures. ROM includes mask ROM, PROM, EPROM, and is read-only memory that can be programmed during manufacture or special modes. Hybrid memory such as flash memory has qualities of both RAM and ROM.Cache Memory

Cache MemorySubid Biswas

Ěý

The document discusses cache memory and provides information on various aspects of cache memory including:

- Introduction to cache memory including its purpose and levels.

- Cache structure and organization including cache row entries, cache blocks, and mapping techniques.

- Performance of cache memory including factors like cycle count and hit ratio.

- Cache coherence in multiprocessor systems and coherence protocols.

- Synchronization mechanisms used in multiprocessor systems for cache coherence.

- Paging techniques used in cache memory including address translation using page tables and TLBs.

- Replacement algorithms used to determine which cache blocks to replace when the cache is full.Unit 5 Advanced Computer Architecture

Unit 5 Advanced Computer ArchitectureBalaji Vignesh

Ěý

This document provides an overview of hardware multithreading techniques including fine-grained, coarse-grained, and simultaneous multithreading. Fine-grained multithreading switches threads after every instruction to hide latency. Coarse-grained multithreading switches threads only after long stalls to avoid slowing individual threads. Simultaneous multithreading issues instructions from multiple threads each cycle to better utilize functional units.Linux Memory Management

Linux Memory ManagementSuvendu Kumar Dash

Ěý

The document provides an overview of the Linux operating system, detailing its components, such as the kernel, system libraries, and system utilities, as well as the user space and kernel space. It also discusses address translation, multithreading, and multiprocessing, including their benefits and various models. Ultimately, it highlights the parallel execution capabilities and efficiency improvements offered by multithreading in Linux.Multi processor scheduling

Multi processor schedulingShashank Kapoor

Ěý

The document discusses multi-processor scheduling, highlighting the complexity compared to single-processor scheduling and categorizing it into asymmetric and symmetric approaches. It addresses critical issues such as locking systems, shared data, cache coherence, and processor affinity, explaining their impact on performance and data consistency. Load balancing is also examined, outlining its importance in utilizing multiple processors effectively and describing methods like push and pull migration to distribute workloads.Symmetric multiprocessing

Symmetric multiprocessingMohammad Ali Khan

Ěý

This document discusses symmetric multiprocessing (SMP). It defines SMP as processing programs using multiple processors that share common operating system and memory. The key aspects of SMP are:

- Processors share memory and I/O bus or data path

- A single operating system controls all processors

- SMP architecture allows processors to access same memory simultaneously

- Advantages of SMP include improved performance, availability, ability to incrementally grow, and scaling

- Limitations include additional complexity in operating system and potential bottlenecking of master CPU.Cache coherence ppt

Cache coherence pptArendraSingh2

Ěý

This document discusses cache coherence in single and multiprocessor systems. It provides techniques to avoid inconsistencies between cache and main memory including write-through, write-back, and instruction caching. For multiprocessors, it discusses issues with sharing writable data, process migration, and I/O activity. Software solutions involve compiler and OS management while hardware uses coherence protocols like snoopy and directory protocols.Distributed Operating System_1

Distributed Operating System_1Dr Sandeep Kumar Poonia

Ěý

The document provides a comprehensive overview of distributed operating systems, covering topics such as design goals, inter-process communication, and synchronization methods. It outlines various operating system types, including mainframe, time-sharing, and real-time systems, alongside their features and management functions. Key concepts like process management, memory management, and networking are discussed in the context of their roles within operating systems, supported by specific examples and architectural considerations.Memory mapping

Memory mappingSnehalataAgasti

Ěý

Cache memory is located between the processor and main memory. It is smaller and faster than main memory. There are two types of cache memory policies - write-back and write-through. Mapping is a technique that maps CPU-generated memory addresses to cache lines. There are three types of mapping - direct, associative, and set associative. Direct mapping maps each main memory block to a single cache line using the formula: cache line number = main memory block number % number of cache lines. This can cause conflict misses.operating system structure

operating system structureWaseem Ud Din Farooqui

Ěý

The document discusses key components and concepts related to operating system structures. It describes common system components like process management, memory management, file management, I/O management, and more. It then provides more details on specific topics like the role of processes, main memory management, file systems, I/O systems, secondary storage, networking, protection systems, and command interpreters in operating systems. Finally, it discusses operating system services, system calls, and how parameters are passed between programs and the operating system.Similar to Cache coherence (20)

Lecture-7 Main Memroy.pptx

Lecture-7 Main Memroy.pptxAmanuelmergia

Ěý

Operating systems use main memory management techniques like paging and segmentation to allocate memory to processes efficiently. Paging divides both logical and physical memory into fixed-size pages. It uses a page table to map logical page numbers to physical frame numbers. This allows processes to be allocated non-contiguous physical frames. A translation lookaside buffer (TLB) caches recent page translations to improve performance by avoiding slow accesses to the page table in memory. Protection bits and valid/invalid bits ensure processes only access their allocated memory regions.Memory Management in Operating Systems for all

Memory Management in Operating Systems for allVSKAMCSPSGCT

Ěý

The document discusses memory management techniques used in computer systems. It describes the memory hierarchy from fast registers to slower main memory and disk. Memory management aims to efficiently allocate memory for multiple processes while providing protection, relocation, sharing and logical organization. Techniques include contiguous allocation, fixed and dynamic partitioning, paging using page tables, segmentation using segment tables, and swapping processes in and out of memory. Hardware support through relocation registers, memory management units, translation lookaside buffers and associative memory help map logical to physical addresses efficiently.chapter-6-multiprocessors-and-thread-level (1).ppt

chapter-6-multiprocessors-and-thread-level (1).pptharishM874937

Ěý

Chapter 6 discusses multiprocessors and thread-level parallelism, highlighting different architectures like symmetric shared-memory and distributed shared-memory. It elaborates on performance aspects, cache coherence challenges, and communication models between processors, including advantages of both shared and message-passing communication. The chapter concludes with insights on multithreading and the role of application domains in exploiting parallelism.247267395-1-Symmetric-and-distributed-shared-memory-architectures-ppt (1).ppt

247267395-1-Symmetric-and-distributed-shared-memory-architectures-ppt (1).pptssuser5c9d4b1

Ěý

The document covers multiprocessors and thread-level parallelism, discussing various architectures such as symmetric shared-memory and distributed shared-memory systems. It highlights performance aspects, synchronization issues, cache coherence protocols, and models of memory consistency. Additionally, it defines several taxonomies of parallel architectures, including the categories of Flynn's taxonomy.22CS201 COA

22CS201 COAKathirvel Ayyaswamy

Ěý

This document discusses parallel processors and multicore architecture. It begins with an introduction to parallel processors, including concurrent access to memory and cache coherency. It then discusses multicore architecture, where a single physical processor contains the logic of two or more cores. This allows increasing processing power while keeping clock speeds and power consumption lower than would be needed for a single high-speed core. Cache coherence methods like write-through, write-back, and directory-based approaches are also summarized for maintaining consistency across cores' caches when accessing shared memory.Cache Coherence.pptx

Cache Coherence.pptxSamyakJain710491

Ěý

The document discusses cache coherence and different cache coherence protocols. Cache coherence is needed when multiple processor cores have their own caches to access shared memory. Incorrect execution could occur if the same data has different values in different caches. The document describes write-through, write-back, snoopy, and directory-based cache coherence protocols. Write-through updates memory on every write, while write-back only updates on cache eviction. Snoopy protocol uses a shared bus to monitor transactions. Directory-based protocol uses directories in memory to track the state of each block in large multiprocessor systems.Cache simulator

Cache simulatorSuraj Saini

Ěý

This document describes a cache simulator project. It discusses cache memory, types of cache including L1, L2 and L3 caches. It also describes cache mapping techniques like direct mapping, associative mapping, and set associative mapping. The document explains cache hits and misses. It covers write policies like write-back and write-through. Replacement algorithms like FIFO and LRU are also summarized. The cache simulator calculates metrics like hit rate, runtime, and memory access latency based on a memory access pattern file. It is implemented using data structures like queues for FIFO and doubly linked lists for LRU replacement.assignment_presentaion_jhvvnvhjhbhjhvjh.pptx

assignment_presentaion_jhvvnvhjhbhjhvjh.pptx23mu36

Ěý

The document discusses interleaved memory organization and multiprocessor operating systems, focusing on techniques to enhance memory access performance and configurations for parallel processing. It outlines various operating system architectures, including master-slave, separate supervisor, and floating supervisor models, along with their advantages and disadvantages. Additionally, it details software requirements for managing processors and optimizing resource utilization in different configurations.Ch8 main memory

Ch8 main memoryWelly Dian Astika

Ěý

This document provides an overview of memory management techniques in operating systems. It discusses contiguous memory allocation, segmentation, paging, and swapping. Contiguous allocation allocates processes to contiguous sections of memory which can lead to fragmentation issues. Segmentation divides memory into logical segments defined by segment tables. Paging divides memory into fixed-size pages and uses page tables to map virtual to physical addresses, avoiding external fragmentation. Swapping moves processes between main memory and disk to allow more processes to reside in memory than will physically fit. The document describes the hardware and data structures used to implement these techniques.Operating systems- Main Memory Management

Operating systems- Main Memory ManagementDr. Chandrakant Divate

Ěý

Chapter 8 discusses various memory management techniques, including swapping, contiguous allocation, segmentation, and paging, with a focus on their implementation and hardware support. It also covers concepts like address binding, logical versus physical address spaces, and the impact of fragmentation on memory allocation. Examples from Intel and ARM architectures illustrate these memory management methods and their application in operating systems.MK Sistem Operasi.pdf

MK Sistem Operasi.pdfwisard1

Ěý

The document outlines the key concepts covered in an operating systems course, including:

1. Operating system structures like processes, threads, CPU scheduling, synchronization, deadlocks, memory and file systems.

2. Linux and Windows system internals such as interrupts, device drivers, and protection.

3. Distributed systems topics like networks, client-server models, peer-to-peer architectures, and virtual machines.Memory Management.pdf

Memory Management.pdfSujanTimalsina5

Ěý

This chapter discusses various memory management techniques used in computer systems, including segmentation, paging, and swapping. Segmentation divides memory into variable-length logical segments, while paging divides it into fixed-size pages that can be mapped to non-contiguous physical frames. Paging requires a page table to map virtual to physical addresses and allows processes to exceed physical memory by swapping pages to disk. The chapter describes address translation hardware like TLBs, protection mechanisms, and issues like fragmentation.UNIT 3-EXPLAINING THE MEMORY MANAGEMENT LOGICAL AND AND PHYSICAL DATA FLOW DI...

UNIT 3-EXPLAINING THE MEMORY MANAGEMENT LOGICAL AND AND PHYSICAL DATA FLOW DI...LeahRachael

Ěý

The document discusses different memory management techniques used in operating systems. It describes logical and physical addresses, and how memory management is the responsibility of the operating system. It then explains address binding, which maps logical addresses to physical addresses. Next, it covers overlays, which allow multiple programs to share memory by swapping parts in and out. It notes the advantages and disadvantages of overlays. Finally, it briefly discusses contiguous allocation, which allocates memory to a process in a single continuous block.Mahti quick-start guide

Mahti quick-start guide CSC - IT Center for Science

Ěý

This webinar provided an overview of the Mahti supercomputer:

- Mahti has 1404 nodes each with two 64-core AMD Rome CPUs and 256GB RAM for a total of around 180,000 cores.

- Users can run pure MPI, hybrid MPI/OpenMP, or hybrid MPI/OpenMP with SMT jobs on Mahti.

- The webinar covered technical details like Mahti's hierarchical architecture and recommendations for optimizing job placement.

- Questions about Mahti can be addressed via CSC's website and customer portal.Parallel Processing Presentation2

Parallel Processing Presentation2daniyalqureshi712

Ěý

This document discusses parallel processing and computer architecture. It begins by using the analogy of making sandwiches to explain the difference between sequential and parallel processing. Parallel processing allows multiple tasks to be performed simultaneously using multiple processors. The document then discusses different types of parallel processor systems like SISD, SIMD, MISD, and MIMD. It also covers considerations for multiprocessor operating system design, symmetric multiprocessor systems, bus organization, cache coherence issues, and solutions to cache coherence problems like directory and snoopy protocols.Cache Memory.pptx

Cache Memory.pptxssusere16bd9

Ěý

Cache memory is a small, fast memory located close to the CPU that stores frequently accessed data from main memory to speed up processing. It is organized into multiple levels - L1 cache is inside the CPU, L2 cache is external, and main memory is L3. The cache improves performance by reducing access time - when data is in cache it is a "hit" and very fast to access, while a "miss" requires loading from main memory which is slower. Factors like cache size, mapping technique, replacement policy, and write strategy impact how efficiently it services memory requests.Ad

Cache coherence

- 1. Cache Coherence for Multiprocessors Presented by Adesh Mishra Reg. No.:1111427 Roll No.:RD1107A44

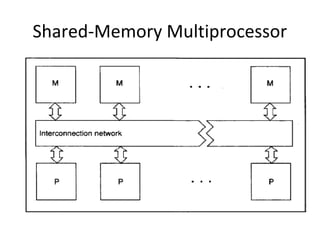

- 2. • Shared-Memory Multiprocessor all processor share a common memory, each processor have own cache. • Cache Coherence Problem • Solutions to Cache Coherence – Hardware • Policies • Two Primary Categories – Software

- 4. Cache Coherence Problem • Multiple copy of the same data can exist in the different caches simultaneously, • and if processors allowed to update their own copies freely, an inconsistent view of memory can result. • Write policies : write back, write through ->In the write back policy only cache is updated and the location marked so that it can be copied later into main memory. ->In the write through policy cache and main memory are updated with every write operation.

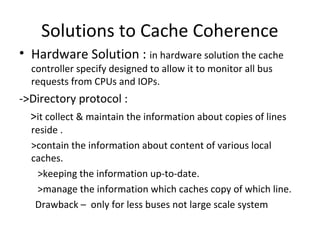

- 5. Solutions to Cache Coherence • Hardware Solution : in hardware solution the cache controller specify designed to allow it to monitor all bus requests from CPUs and IOPs. ->Directory protocol : >it collect & maintain the information about copies of lines reside . >contain the information about content of various local caches. >keeping the information up-to-date. >manage the information which caches copy of which line. Drawback – only for less buses not large scale system

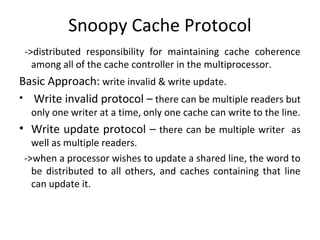

- 6. Snoopy Cache Protocol ->distributed responsibility for maintaining cache coherence among all of the cache controller in the multiprocessor. Basic Approach: write invalid & write update. • Write invalid protocol – there can be multiple readers but only one writer at a time, only one cache can write to the line. • Write update protocol – there can be multiple writer as well as multiple readers. ->when a processor wishes to update a shared line, the word to be distributed to all others, and caches containing that line can update it.

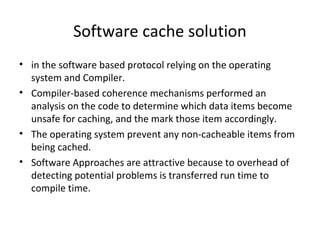

- 7. Software cache solution • in the software based protocol relying on the operating system and Compiler. • Compiler-based coherence mechanisms performed an analysis on the code to determine which data items become unsafe for caching, and the mark those item accordingly. • The operating system prevent any non-cacheable items from being cached. • Software Approaches are attractive because to overhead of detecting potential problems is transferred run time to compile time.

- 8. ?