vxl.vdk.TranThanhPhong

- 1. 1 GIß╗ÜI THIß╗åU Tß╗öNG QUAN VI Xß╗¼ L├Ø ŌĆō VI ─ÉIß╗ĆU KHIß╗éN CHŲ»ŲĀNG 1

- 2. 2 Nß╗śI DUNG VI xß╗Ł l├Į v├Ā Hß╗ć thß╗æng vi xß╗Ł l├Į1 Vi ─æiß╗üu khiß╗ān2 ├ön tß║Łp hß╗ć thß╗æng sß╗æ hß╗Źc3

- 3. 3 VI Xß╗¼ L├Ø ß╗©NG Dß╗żNG V├ĆO ─É├éU ?

- 4. 4 VI Xß╗¼ L├Ø L├Ć G├ī ? ’üČSß╗▒ kß║┐t hß╗Żp cß╗¦a 2 kß╗╣ thuß║Łt: ’āśM├Īy t├Łnh kß╗╣ thuß║Łt sß╗æ v├Ā ’āśC├Īc mß║Īch vi ─æiß╗ćn tß╗Ł.

- 5. 5 Lß╗ŖCH Sß╗¼ PH├üT TRIß╗éN VI Xß╗¼ L├Ø ’üČLß╗ŗch sß╗Ł ph├Īt triß╗ān gß║»n liß╗ün vß╗øi sß╗▒ ph├Īt triß╗ān cß╗¦a c├Īc vi mß║Īch ─æiß╗ćn tß╗Ł. ’üČGiai ─æoß║Īn 1 (1971 - 1973) ─æ├óy l├Ā giai ─æoß║Īn khß╗¤i ─æß║¦u cß╗¦a vi xß╗Ł l├Į. C├Īc vi xß╗Ł l├Į n├Āy ─æß╗üu c├│ ─æß╗Ö d├Āi tß╗½ dß╗» liß╗ću ngß║»n, tß╗æc ─æß╗Ö l├Ām viß╗ćc thß║źp, tß║Łp lß╗ćnh ─æŲĪn giß║Żn nhŲ░ 4004, 8008. ’üČGiai ─æoß║Īn 2 (1974 - 1977) tß║Łp lß╗ćnh phong ph├║ hŲĪn v├Ā c├│ khß║Ż n─āng ph├ón biß╗ćt ─æß╗ŗa chß╗ē bß╗Ö nhß╗ø v├Ā dung lŲ░ß╗Żng ─æß║┐n 64 K byte, tß╗æc ─æß╗Ö xß╗Ł l├Į t─āng l├¬n v├Āi Mhz. ─Éß║Īi diß╗ćn cho giai ─æoß║Īn n├Āy nhŲ░ 6800, 6809 cß╗¦a Motorola; 8085, 8080 cß╗¦a Intel v├Ā Z80 cß╗¦a Zilog.

- 6. 6 Lß╗ŖCH Sß╗¼ PH├üT TRIß╗éN VI Xß╗¼ L├Ø ’üČGiai ─æoß║Īn 3 (1978 - 1982) c├Īc bß╗Ö vi xß╗Ł l├Į giai ─æoß║Īn n├Āy l├Ā c├Īc vi xß╗Ł l├Į 16 Bit tß╗æc ─æß╗Ö l├Ām viß╗ćc l├¬n ─æß║┐n 10 Mhz. ’üČGiai ─æoß║Īn 4 (1984 ─æß║┐n nay) ’āśVXL 32 bit 80386/80486 v├Ā 64 bit Pentium/ Pentium II / Pentium III cß╗¦a Intel, Core Duo.. ’āśVXL 32 bit 68020/ 68030/ 68040/ 68060 cß╗¦a Motorola. ’āś─Éß║Ęc ─æiß╗ām cß╗¦a VXL trong giai ─æoß║Īn n├Āy l├Ā bus ─æß╗ŗa chß╗ē ─æß╗üu l├Ā 32 bit v├Ā c├│ khß║Ż n─āng l├Ām viß╗ćc vß╗øi bß╗Ö nhß╗ø ß║Żo.

- 7. 7 Hß╗å THß╗ÉNG VI Xß╗¼ L├Ø L├Ć G├ī? ’üČ─Éß╗ā sß╗Ł dß╗źng vi xß╗Ł l├Į cß║¦n phß║Żi thiß║┐t kß║┐ hß╗ć thß╗æng gß╗ōm c├│ c├Īc th├Ānh phß║¦n sau: ’āś Vi xß╗Ł l├Į ’āś C├Īc bß╗Ö nhß╗ø ’āś C├Īc IC ngoß║Īi vi ’üČ─Éß╗ā thiß║┐t kß║┐ ─æŲ░ß╗Żc hß╗ć thß╗æng vi xß╗Ł l├Į cß║¦n phß║Żi biß║┐t y├¬u cß║¦u ─æiß╗üu khiß╗ān l├Ā g├¼!

- 8. 8 Hß╗å THß╗ÉNG VI Xß╗¼ L├Ø ’üČVi X├Č├╗ Ly├╣: th├Č├»c hie├żn ch├Č├┤ng tr├¼nh va├Ė ├▒ie├Āu khie├źn ’üČBo├ż nh├┤:├╣ ch├Č├╣a ch├Č├┤ng tr├¼nh va├Ė d├Č├Ą lie├żu. ’üČNgoa├»i vi: du├Ėng ├▒e├ź xua├Īt nha├żp d├Č├Ą lie├żu v├┤├╣i be├ón ngoa├Ėi. ’āś Ca├╣c kho├Īi na├Ėy lie├ón ke├Īt v├┤├╣i nhau ta├»o tha├Ėnh mo├żt he├ż tho├Īng vi x├Č├╗ ly├╣. ’āś Ye├óu ca├Āu ├▒ie├Āu khie├źn ca├Ėng nhie├Āu th├¼ he├ż tho├Īng ca├Ėng ph├Č├╣c ta├»p ’āś Du├Ė nhu ca├Āu ├▒ie├Āu khie├źn ├▒├┤n gia├╗n ŌĆō th├¼ he├ż tho├Īng cu├Ąng pha├╗i co├╣ ├▒a├Āy ├▒u├╗ ca├╣c kho├Īi tre├ón.

- 9. 9 SŲĀ ─Éß╗Æ KHß╗ÉI Hß╗å THß╗ÉNG VI Xß╗¼ L├Ø CPU ROM RAM Mß║Īch giao tiß║┐p ngoß║Īi vi (IO) Bus dß╗» liß╗ću (Data Bus) Bus ─æß╗ŗa chß╗ē (Address Bus) Bus ─æiß╗üu khiß╗ān (Control Bus) Input Output

- 10. 10 N─āng Lß╗▒c Cß╗¦a Vi Xß╗Ł L├Į ’üČ Chiß╗üu d├Āi cß╗¦a tß╗½ dß╗» liß╗ću cß╗¦a VXL: ’āś Mß╗Śi vxl l├Ām viß╗ćc vß╗øi c├Īc tß╗½ dß╗» liß╗ću c├│ ─æß╗Ö d├Āi cß╗æ ─æß╗ŗnh. ’āś Tß╗½ dß╗» liß╗ću thŲ░ß╗Øng d├╣ng 8 bit ß╗®ng vß╗øi 1 byte. ’āś ─Éß╗Ö d├Āi tß╗½ dß╗» liß╗ću trong bß╗Ö nhß╗ø bß║▒ng ─æß╗Ö d├Āi tß╗½ dß╗» liß╗ću trong vxl.

- 11. 11 N─āng Lß╗▒c Cß╗¦a Vi Xß╗Ł L├Į ’üČSß╗æ lŲ░ß╗Żng ├┤ nhß╗ø m├Ā VXL c├│ thß╗ā truy xuß║źt: ’āś Mß╗Śi tß╗½ dß╗» liß╗ću chß╗®a trong 1 ├┤ nhß╗ø ’āś Mß╗Śi ├┤ nhß╗ø trong bß╗Ö nhß╗ø c├│ mß╗Öt ─æß╗ŗa chß╗ē. ŌĆó VXL muß╗æn truy xuß║źt dß╗» liß╗ću trong ├┤ nhß╗ø phß║Żi tß║Īo ─æß╗ŗa chß╗ē cß╗¦a ├┤ nhß╗ø ─æ├│. ’āś VXL c├│ thß╗ā giao tiß║┐p vß╗øi bß╗Ö nhß╗ø c├│ dung lŲ░ß╗Żng c├Āng lß╗øn th├¼ vxl ─æ├│ c├Āng mß║Īnh. ’üČV├Ł Dß╗ź: ŌĆó 8 bit c├│ 16 ─æŲ░ß╗Øng ─æß╗ŗa chß╗ē: 216 = 65.536 ├┤ nhß╗ø ŌĆó 16 bit c├│ 20 ─æŲ░ß╗Øng ─æß╗ŗa chß╗ē: 220 = 1.024.000 ├┤ nhß╗ø ŌĆó 32 bit (386) truy xuß║źt 4G ├┤ nhß╗ø.

- 12. 12 N─āng Lß╗▒c Cß╗¦a Vi Xß╗Ł L├Į ’üČTß╗æc ─æß╗Ö l├Ām viß╗ćc cß╗¦a vi xß╗Ł l├Į: ’āśTß║¦n sß╗æ xung clock quyß║┐t ─æß╗ŗnh. ’āśTß║¦n sß╗æ xung clock ─æŲ░ß╗Żc nh├Ā sß║Żn xuß║źt qui ─æß╗ŗnh ’āśTß╗æc ─æß╗Ö c├Āng nhanh khß║Ż n─āng xß╗Ł l├Į lß╗ćnh c├Āng nhanh.

- 13. 13 Cß║żU TR├ÜC Cß╗”A VI Xß╗¼ L├Ø ’üČ─ÉŲĪn vß╗ŗ xß╗Ł l├Į logic sß╗æ hß╗Źc ALU: Arithmetic Logic Unit: ’üČ C├Īc thanh ghi: ’āśAccumulator, ’āśPC: Program Counter, ’āśSR: Status Register, ’āśSP: Stack Pointer, ’āśThanh ghi ─æß╗ŗa chß╗ē ├┤ nhß╗ø, ’āśThanh ghi lß╗ćnh (IR: Instruction Register) ’üČ Khß╗æi ─æiß╗üu khiß╗ān logic (Control logic) v├Ā khß╗æi giß║Żi m├Ż lß╗ćnh (Instruction Decoder).

- 14. 14 C├üC THANH GHI QUAN TRß╗īNG ’üČThanh ghi l├Ā g├¼? ’üČThanh ghi: phß║¦n quan trß╗Źng trong vxl. ’üČD├╣ng ─æß╗ā xß╗Ł l├Į dß╗» liß╗ću, c├│ chiß╗üu d├Āi theo tß╗½ng chß╗®c n─āng trong vxl. ’üČ Sß╗æ lŲ░ß╗Żng thanh ghi c├Āng lß╗øn ngŲ░ß╗Øi lß║Łp tr├¼nh c├Āng dß╗ģ d├Āng, tß╗æc ─æß╗Ö xß╗Ł l├Į chŲ░ŲĪng tr├¼nh nhanh. ’üČMß╗Śi loß║Īi vxl c├│ sß╗æ lŲ░ß╗Żng thanh ghi v├Ā chß╗®c n─āng thanh ghi kh├Īc nhau.

- 15. 15 THANH GHI Dß╗ŖCH ’üČThanh ghi c├│ cß║źu tß║Īo gß╗ōm c├Īc trigger nß╗æi tiß║┐p vß╗øi nhau ’üČChß╗®c n─āng: ’āś─Éß╗ā lŲ░u trß╗» tß║Īm thß╗Øi th├┤ng tin ’āśDß╗ŗch chuyß╗ān th├┤ng tin ’üČLŲ░u ├Į: cß║Ż thanh ghi v├Ā bß╗Ö nhß╗ø ─æß╗üu d├╣ng ─æß╗ā lŲ░u trß╗» th├┤ng tin, nhŲ░ng thanh ghi c├│ chß╗®c n─āng dß╗ŗch chuyß╗ān th├┤ng tin.

- 16. 16 PH├éN LOß║ĀI THANH GHI Dß╗ŖCH ’üČV├Āo nß╗æi tiß║┐p ra nß╗æi tiß║┐p ’āśSIPI ’üČV├Āo nß╗æi tiß║┐p ra song song ’āśSIPO ’üČV├Āo song song ra nß╗æi tiß║┐p ’āśPISO ’üČV├Āo song song ra song song ’āśPIPO 0 1 0 1 0 0 11 0 1 0 1 0 0 11 0 1 0 1 0 0 11 0 1 0 1 0 0 11

- 17. 17 Cß║żU TR├ÜC V├Ć NGUY├ŖN L├Ø L├ĆM VIß╗åC Cß╗”A THANH GHI Dß╗ŖCH

- 18. 18 THANH GHI A ’üČThanh ghi A (Accumulator: thanh chß╗®a) ’üČQuan trß╗Źng, lu├┤n c├│ trong mß╗Źi vxl, chß╗®a dß╗» liß╗ću khi t├Łnh to├Īn v├Ā xß╗Ł l├Į. ’āśC├Īc ph├®p to├Īn sß╗æ hß╗Źc, logic ─æß╗üu xß║Ży ra giß╗»a ALU v├Ā A ’üČTruyß╗ün dß╗» liß╗ću tß╗½ bß╗Ö nhß╗ø hay tß╗½ c├Īc thanh ghi b├¬n trong vxl ra c├Īc thiß║┐t bß╗ŗ ngoß║Īi vi th├¼ dß╗» liß╗ću phß║Żi chß╗®a trong thanh ghi A. ’üČSß╗æ bit cß╗¦a thanh ghi A l├Ā ─æŲĪn vß╗ŗ ─æo cß╗¦a vxl, nß║┐u vxl 8 bit th├¼ thanh ghi A c├│ ─æß╗Ö d├Āi l├Ā 8 bit.

- 19. 19 THANH GHI PC (Program Counter) ’üČPC: thanh ghi quan trß╗Źng nhß║źt cß╗¦a vi xß╗Ł l├Į ’üČQuß║Żn l├Į lß╗ćnh m├Ā vxl ─æang thß╗▒c hiß╗ćn v├Ā ─æiß╗üu khiß╗ān viß╗ćc lß║źy lß╗ćnh thß╗▒c hiß╗ćn kß║┐ tiß║┐p. ’üČThanh ghi PC trong vxl c├│ ─æß╗Ö d├Āi lß╗øn hŲĪn chiß╗üu d├Āi tß╗½ dß╗» liß╗ću cß╗¦a vxl. ’üČNß╗Öi dung chß╗®a trong thanh ghi PC ch├Łnh l├Ā nß╗Öi dung chß╗®a trong thanh ghi ─æß╗ŗa chß╗ē. ’üČTrŲ░ß╗øc khi vxl thß╗▒c hiß╗ćn chŲ░ŲĪng tr├¼nh th├¼ PC phß║Żi ─æŲ░ß╗Żc nß║Īp 1 con sß╗æ. ’āśSß╗æ ─æ├│ l├Ā: ─æß╗ŗa chß╗ē cß╗¦a ├┤ nhß╗ø chß╗®a lß╗ćnh ─æß║¦u ti├¬n cß╗¦a chŲ░ŲĪng tr├¼nh.

- 20. 20 Thao t├Īc t├¼m nß║Īp lß╗ćnh v├Ā thß╗▒c hiß╗ćn lß╗ćnh NPC M├Ż lß╗ćnh M├Ż lß╗ćnh M├Ż lß╗ćnh N N+1 N+2 IR Vi Xß╗Ł L├Į (CPU) Bß╗Ö Nhß╗ø (ROM) Bus ─æß╗ŗa chß╗ē Bus dß╗» liß╗ću M├Ż lß╗ćnh TG─ÉC N

- 21. 21 THANH GHI IR ’üČThanh ghi IR d├╣ng ─æß╗ā chß╗®a lß╗ćnh vxl ─æang thß╗▒c hiß╗ćn. ’üČMß╗Öt chu kß╗│ lß╗ćnh bao gß╗ōm ─æ├│n lß╗ćnh tß╗½ bß╗Ö nhß╗ø v├Ā thß╗▒c hiß╗ćn lß╗ćnh. ’üČTrong qu├Ī tr├¼nh thß╗▒c hiß╗ćn lß╗ćnh, bß╗Ö giß║Żi m├Ż lß╗ćnh ─æß╗Źc nß╗Öi dung cß╗¦a thanh ghi lß╗ćnh IR. ’üČMa├Ą le├żnh t├Č├Ė thanh ghi IR ├▒├Č├┤├»c ├▒├Ča va├Ėo ├▒├┤n v├▓ gia├╗i ma├Ą le├żnh va├Ė ├▒ie├Āu khie├źn.

- 22. 22 THANH GHI SR (Status Rigester) ’üČ Thanh ghi SR l├Ā thanh ghi cß╗Ø, d├╣ng ─æß╗ā lŲ░u kß║┐t quß║Ż cß╗¦a mß╗Öt sß╗æ lß╗ćnh kiß╗ām tra. ’üČ Zero bit: bit Z = 1 khi kß║┐t quß║Ż l├Ā 0, ngŲ░ß╗Żc lß║Īi Z =0 ’üČ Negative bit: bit N=1 khi bit MSB cß╗¦a thanh ghi =1 ’üČ Carry/Borrow bit: l├Ā bit carry khi thß╗▒c hiß╗ćn ph├®p cß╗Öng C =1 khi tr├Ān ngŲ░ß╗Żc lß║Īi C = 0. L├Ā bit Borrow khi thß╗▒c hiß╗ćn ph├®p trß╗½, borrow=0 khi sß╗æ bß╗ŗ trß╗½ lß╗øn hŲĪn sß╗æ trß╗½ ’üČ Intermediate carry: giß╗æng bit C nhŲ░ng c├│ t├Īc dß╗źng vß╗øi cß╗Öng /trß╗½ 4 bit thß║źp. ’üČ Interrupt Flag: Bit IF =1 khi ngŲ░ß╗Øi lß║Łp tr├¼nh cho ph├®p ngß║»t. ’üČ Overflow: bit n├Āy bß║▒ng 1 khi bit tr├Ān cß╗¦a ph├®p cß╗Öng vß╗øi bit dß║źu cß╗¦a dß╗» liß╗ću. ’üČ Parity: bit P=1 khi cho ph├®p kiß╗ām tra chß║│n. Z N C I IF O P 1

- 23. 23 THANH GHI CON TRß╗Ä (STACK POINTER) ’üČChß╗®c n─āng cß╗¦a thanh ghi SP gß║¦n giß╗æng vß╗øi PC, d├╣ng ─æß╗ā quß║Żn l├Į bß╗Ö nhß╗ø ng─ān xß║┐p khi muß╗æn lŲ░u trß╗» dß╗» liß╗ću tß║Īm thß╗Øi v├Āo ng─ān xß║┐p. ’üČSP tß╗▒ ─æß╗Öng di chuyß╗ān ─æß║┐n ├┤ nhß╗ø kß║┐ tiß║┐p ’üČNgŲ░ß╗Øi lß║Łp tr├¼nh phß║Żi thiß║┐t lß║Łp gi├Ī trß╗ŗ ban ─æß║¦u cho SP. ’üČTß╗Ģ chß╗®c SP l├Ā LIFO: LAST IN FIRST OUT.

- 24. 24 Hß╗å THß╗ÉNG BUS ’üČBus ├▒├▓a ch├” (Address bus): ’āś ├æe├ź chuye├źn ta├╗i ca├╣c bit ├▒├▓a ch├”. ’āś La├Ė loa├»i bus 1 chie├Āu (CPU-MEM hay I/O). ’āś ├æe├ź xa├╣c ├▒├▓nh bo├ż nh├┤├╣ hoa├½c thie├Īt b├▓ ngoa├»i vi ma├Ė CPU ca├Ān trao ├▒o├źi tho├óng tin. ’āś ├æe├ź xa├╣c ├▒├▓nh dung l├Č├┤├»ng bo├ż nh├┤├╣ hoa├½c ngoa├»i vi ma├Ė CPU co├╣ kha├╗ na├¬ng truy xua├Īt.

- 25. 25 Hß╗å THß╗ÉNG BUS ’üČBus d├Č├Ą lie├żu (Data bus): ’üČ ├æe├ź chuye├źn ta├╗i ca├╣c bit d├Č├Ą lie├żu. ’üČ La├Ė loa├»i bus 2 chie├Āu (CPU Ōåö MEM-I/O). ’üČ ├æe├ź xa├╣c ├▒├▓nh so├Ī bit d├Č├Ą lie├żu ma├Ė CPU co├╣ kha├╗ na├¬ng x├Č├╗ ly├╣ cu├Ėng mo├żt lu├╣c.

- 26. 26 Hß╗å THß╗ÉNG BUS ’üČ Bus ├▒ie├Āu khie├źn (Control bus): ’üČ├æe├ź chuye├źn ta├╗i ca├╣c bit ├▒ie├Āu khie├źn (mo├Żi ├▒├Č├┤├Ėng da├óy la├Ė mo├żt t├Łn hie├żu ├▒ie├Āu khie├źn kha├╣c nhau). ’üČLa├Ė loa├»i bus 1 chie├Āu (CPU ŌåÆ MEM-I/O hoa├½c MEM-I/O ŌåÆ CPU). ’üČ─Ée├ź ├▒ie├Āu khie├źn ca├╣c kho├Īi kha├╣c trong he├ż va├Ė nha├żn t├Łn hie├żu ├▒ie├Āu khie├źn t├Č├Ė ca├╣c kho├Īi ├▒o├╣ ├▒e├ź pho├Īi

- 27. 27 SUY NGH─© ’üČMu n vxl l├Ām vi c g├¼ ng i d├╣ngß╗æ ß╗ć Ų░ß╗Ø ph i l p tr├¼nh (viß║Ż ß║Ł t ch ng tr├¼nh)ß║┐ Ų░ŲĪ . ’āś Ch ng tr├¼nh l u ├óu vxlŲ░ŲĪ Ų░ ß╗¤ ─æ ─æß╗ā l y l nh v├Ā th c hi n l nh ├│?ß║ź ß╗ć ß╗▒ ß╗ć ß╗ć ─æ ’üČTrong l├║c l├Ām vi c vxl c n c tß╗ć ß║¦ ß║ź t m c├Īc d li u, khi c n vxl dß║Ī ß╗» ß╗ć ─æß╗ā ß║¦ ß╗» li u l y ra th c hi n ti p c├Īcß╗ć ß║ź ß╗▒ ß╗ć ß║┐ c├┤ng vi c.ß╗ć ’āśNh v y c├Īc d li u n├Āy ph iŲ░ ß║Ł ß╗» ß╗ć ß║Ż c l u ├óu─æŲ░ß╗Ż Ų░ ß╗¤ ─æ ?

- 28. 28 Bß╗ś NHß╗Ü B├üN Dß║¬N ’üČROM: bß╗Ö nhß╗ø chŲ░ŲĪng tr├¼nh, lŲ░u trß╗» chŲ░ŲĪng tr├¼nh ─æiß╗üu khiß╗ān hoß║Īt ─æß╗Öng cß╗¦a to├Ān hß╗ć thß╗æng. ’üČRAM: bß╗Ö nhß╗ø dß╗» liß╗ću, lŲ░u trß╗» dß╗» liß╗ću tß║Īm thß╗Øi, c├Īc ß╗®ng dß╗źng v├Ā kß║┐t quß║Ż t├Łnh to├Īn.

- 29. 29 Hoß║Īt ─Éß╗Öng Cß╗¦a Bß╗Ö Nhß╗ø ’üČNhß║Łn ─æß╗ŗa chß╗ē ─æß╗ā chß╗Źn ├┤ nhß╗ø cß║¦n truy xuß║źt. ’üČNhß║Łn t├Łn hiß╗ću ─æiß╗üu khiß╗ān ─æß╗ā thß╗▒c hiß╗ćn viß╗ćc truy xuß║źt (xuß║źt / nhß║Łp). ’üČNhß║Łp dß╗» liß╗ću ─æß╗ā lŲ░u v├Āo ├┤ nhß╗ø (GHI: WRITE) ’üČXuß║źt dß╗» liß╗ću ra (─Éß╗īC:READ) ’üČKiß╗ām tra t├Łn hiß╗ću cho ph├®p ─æß╗ā biß║┐t bß╗Ö nhß╗ø c├│ ─æŲ░ß╗Żc ph├®p truy xuß║źt kh├┤ng.

- 30. 30 Bß╗æ Tr├Ł Ch├ón Theo Chß╗®c N─āng Bß╗Ö Nhß╗ø I7 I6 I5 I4 I3 I2 I1 I0 DATA INPUT A0 A1 A2 A3 A4 A5 A6 ─ÉIA CHß╗ł O7 O6 O5 O4 O3 O2 O1 O0 DATA OUTPUT READ / WRITE CS (CHß╗īN CHIP)

- 31. 31 Bß╗æ Tr├Ł Ch├ón Theo Chß╗®c N─āng Bß╗Ö Nhß╗ø OE RW ─ÉIA CHß╗ł A0 A1 A2 A3 A4 A5 A6 DATA D0 D1 D2 D3 D4 D5 D6 CS

- 32. 32 C├Īch X├Īc ─Éß╗ŗnh Bß╗Ö Nhß╗ø ’üČDß╗▒a v├Āo sß╗æ ─æŲ░ß╗Øng ─æß╗ŗa chß╗ēDß╗▒a v├Āo sß╗æ ─æŲ░ß╗Øng ─æß╗ŗa chß╗ē ’āś VD: Bß╗Ö nhß╗ø c├│ 10 ─æŲ░ß╗Øng ─æß╗ŗa chß╗ēVD: Bß╗Ö nhß╗ø c├│ 10 ─æŲ░ß╗Øng ─æß╗ŗa chß╗ē ŌĆó 221010 =1024bit = 1KBIT=1024bit = 1KBIT ’üČDß╗▒a v├Āo m├Ż sß╗æ bß╗Ö nhß╗ø; M├Ż sß╗æ: XX YYYYDß╗▒a v├Āo m├Ż sß╗æ bß╗Ö nhß╗ø; M├Ż sß╗æ: XX YYYY ’āśXX: loß║Īi bß╗Ö nhß╗øXX: loß║Īi bß╗Ö nhß╗ø 27: UV-EPROM27: UV-EPROM 28: EEPROM28: EEPROM 61,62: SRAM61,62: SRAM 40,41: DRAM40,41: DRAM ’üČYYYY: dung lŲ░ß╗Żng cß╗¦a bß╗Ö nhß╗øYYYY: dung lŲ░ß╗Żng cß╗¦a bß╗Ö nhß╗ø ’āśDung lŲ░ß╗Żng = YYYY (Kbit) hoacDung lŲ░ß╗Żng = YYYY (Kbit) hoac ’āśDung lŲ░ß╗Żng = YYYY / 8 (KByte)Dung lŲ░ß╗Żng = YYYY / 8 (KByte)..

- 33. 33 C├Īch X├Īc ─Éß╗ŗnh Bß╗Ö Nhß╗ø ’üČVD: Bß╗Ö nhß╗ø 27256,VD: Bß╗Ö nhß╗ø 27256, ’āś 27 Bß╗Ö nhß╗ø UV-EPROM27 Bß╗Ö nhß╗ø UV-EPROM ’āś256 Dung lŲ░ß╗Żng = 256 (Kbit) = 32 (KB)256 Dung lŲ░ß╗Żng = 256 (Kbit) = 32 (KB) ’āś 15 ─ÉŲ░ß╗Øng ─æß╗ŗa chß╗ē15 ─ÉŲ░ß╗Øng ─æß╗ŗa chß╗ē..

- 34. 34 Bß╗ś NHß╗Ü ROM Pha├ón loa├»i bß╗Ö nhß╗ø ROM: ’üČPROM (Programmable ROM): ROM la├żp tr├¼nh ├▒├Č├┤├»c ’üČEPROM (Eraseable PROM): ROM la├żp tr├¼nh va├Ė xo├╣a ├▒├Č├┤├»c ’üČUV-EPROM (Ultra Violet EPROM): ROM la├żp tr├¼nh, xo├╣a ba├©ng tia c├Č├»c t├Łm ’üČEEPROM (Electric EPROM): ROM la├żp tr├¼nh va├Ė xo├╣a ba├©ng t├Łn hie├żu ├▒ie├żn ’üČFlash ROM: ROM la├żp tr├¼nh va├Ė xo├╣a ba├©ng t├Łn hie├żu ├▒ie├żn.

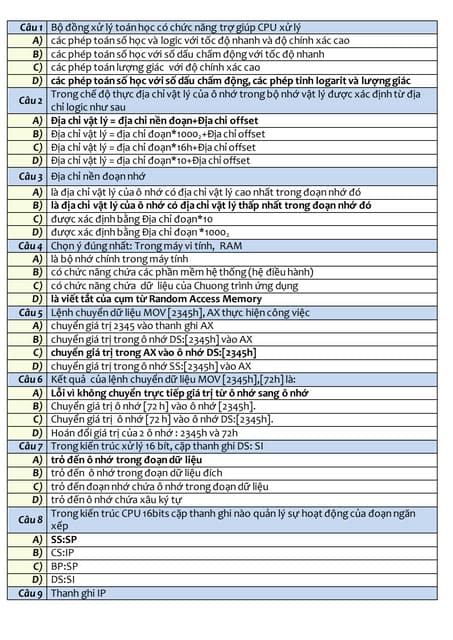

- 36. 36 EPROM 2716 A0 A1 A2 A3 A4 A5 A6 A7 A9 A10 CE OE VPP D0 D1 D2 D3 D4 D5 D6 D7 OE : (output enable) [0] ─æiß╗üu khiß╗ān cho ph├®p bß╗Ö nhß╗ø xuß║źt dß╗» liß╗ću ra b├¬n ngo├Āi. CE : (chip enable) [0] ─æiß╗üu khiß╗ān cho ph├®p bß╗Ö nhß╗ø l├Ām viß╗ćc. VPP: [1] nß║Īp dß╗» liß╗ću, chŲ░ŲĪng tr├¼nh v├Āo bß╗Ö nhß╗ø Chß║┐ ─æß╗Ö CE OE Data ─Éß╗Źc 0 0 Dout Chß╗Ø 1 XX High Z Lß║Łp tr├¼nh EPROM 0 XX Vpp [1] Din

- 37. 37 Bß╗ś NHß╗Ü RAM RAM(Random Access Memory): bß╗Ö nh d li uß╗ø ß╗» ß╗ć ’üČSRAM (Static RAM): RAM t nh─® ’üČDRAM (Dynamic RAM): RAM ng─æß╗Ö ’üČC├Īc ch├ón Data k t h p I/Oß║┐ ß╗Ż .

- 38. 38 SŲĪ ─Éß╗ō Ch├ón Bß╗Ö Nhß╗ø Ram 6116 A0 A1 A2 A3 A4 A5 A6 A7 A9 A10 WR OE CS D0 D1 D2 D3 D4 D5 D6 D7

- 39. 39 Bß║Żng Trß║Īng Th├Īi Chß║┐ ─æß╗Ö WR CS OE Data Kh├┤ng chß╗Źn X 1 X Tß╗Ģng trß╗¤ cao Cß║źm xuß║źt 1 0 1 Tß╗Ģng trß╗¤ cao ─Éß╗Źc Data 1 0 0 Dout Ghi Data 0 0 1 Din A0 A1 A2 A3 A4 A5 A6 A7 A9 A10 WR OE CS D0 D1 D2 D3 D4 D5 D6 D7

- 40. 40 Kß║┐t Nß╗æi Bß╗Ö Nhß╗ø V├Ā VXL ┬ĄP┬ĄP┬ĄP┬ĄP IC NHß╗Ü ROM IC NHß╗Ü ROM IC NHß╗Ü RAM IC NHß╗Ü RAM BUS ─Éß╗ŖA CHß╗ł BUS Dß╗« LIß╗åU BUS ─ÉIß╗ĆU KHIß╗éN

- 41. 41 Hoß║Īt ─Éß╗Öng Ghi Dß╗» Liß╗ću ┬ĄP┬ĄP┬ĄP┬ĄP IC NHß╗Ü RAMIC NHß╗Ü RAM BUS ─Éß╗ŖA CHß╗ł BUS Dß╗« LIß╗åU BUS ─ÉIß╗ĆU KHIß╗éN 1.Tß║Īo ─æß╗ŗa chß╗ē cß║¦n lŲ░u, ─æß║Ęt l├¬n bus ─æß╗ŗa chß╗ē 2. ─ÉŲ░a data cß║¦n lŲ░u l├¬n bus dß╗» liß╗ću 3. VXL t├Īc ─æß╗Öng t├Łn hiß╗ću ─æiß╗üu khiß╗ān ghi 4. IC nhß╗ø x├Īc ─æß╗ŗnh ─æß╗ŗa chß╗ē ├┤ nhß╗ø cß║¦n lŲ░u 5. Data tß╗½ bus truyß╗ün v├Āo ├┤ nhß╗ø WRData

- 42. 42 Hoß║Īt ─Éß╗Öng ─Éß╗Źc Dß╗» Liß╗ću ┬ĄP┬ĄP┬ĄP┬ĄP IC NHß╗Ü RAM / ROMIC NHß╗Ü RAM / ROM BUS ─Éß╗ŖA CHß╗ł BUS Dß╗« LIß╗åU BUS ─ÉIß╗ĆU KHIß╗éN 1.Tß║Īo ─æß╗ŗa chß╗ē cß║¦n ─æß╗Źc, ─æß║Ęt l├¬n bus ─æß╗ŗa chß╗ē 5. ─ÉŲ░a dß╗» liß╗ću cß║¦n ─æß╗Źc v├Āo VXL 2. VXL t├Īc ─æß╗Öng t├Łn hiß╗ću ─æiß╗üu khiß╗ān ─æß╗Źc 3. IC nhß╗ø x├Īc ─æß╗ŗnh ─æß╗ŗa chß╗ē ├┤ nhß╗ø cß║¦n ─æß╗Źc 4. Data tß╗½ ├┤ nhß╗ø ─æß║Ęt l├¬n bus OEData

- 43. 43 SŲĪ ─Éß╗ō Nguy├¬n L├Į Kß║┐t Nß╗æi D 74LS373ALE P0.0 P0.7 PSEN A0 A7 D0 D7 P2.0 P2.7 A8 A15 OE CE EA G 8031 ROM

- 44. 44 BUS ĐA HỢP

- 45. 45 Hoß║Īt ─Éß╗Öng Xuß║źt ─Éß╗ŗa Chß╗ē Tß╗øi ROM D 74LS373ALE P0.0 P0.7 PSEN A0 A7 D0 D7 P2.0 P2.7 A8 A12 OE CE EA G 8051 ROM 1. Gß╗Łi ─æß╗ŗa chß╗ē tß╗øi ROM 2. 74373 chß╗æt ─æß╗ŗa chß╗ē v├Ā gß╗Łi sang ROM ─Éß╗ŗa chß╗ē

- 46. 46 Hoß║Īt ─Éß╗Öng ─Éß╗Źc Dß╗» Liß╗ću Tß╗½ ROM D 74LS373ALE P0.0 P0.7 PSEN A0 A7 D0 D7 P2.0 P2.7 A8 A12 OE CE EA G 8051 ROM Address 3. ROM gß╗Łi lß╗ćnh vß╗ü V─ÉK

- 47. 47 VXL Kß║┐t Nß╗æi Nhiß╗üu Bß╗Ö Nhß╗ø ┬ĄP 74138 74138 A10 ├Ę A0 D7├ĘD0 CS1 OE 2716 ROM1 CS8 OE 2716 ROM8 6116 Ram1 6116 Ram8 CS8CS1 OE OE WR WRWR RD RDRDRD WR ─Éß║┐n CS1 Ram1 ─Éß║┐n CS8 Ram8 ─Éß║┐n CS1 Rom1 ─Éß║┐n CS1 Rom8 A B C A B C A11 A12 A13

- 48. 48 SŲĀ ─Éß╗Æ KHß╗ÉI M├üY T├ŹNH PC

- 49. 49 Hß╗ć thß╗æng VXL c├│ ph├╣ hß╗Żp ─æiß╗üu khiß╗ān trong c├┤ng nghiß╗ćp kh├┤ng? ’üČVxl xß╗Ł l├Į dß╗» liß╗ću theo byte, word. ŌĆó Hß╗ć thß╗æng Vi Xß╗Ł L├Į : Vi xß╗Ł l├Į + Bß╗Ö Nhß╗ø + Thiß║┐t bß╗ŗ ngoß║Īi vi ’üČC├Īc ─æß╗æi tŲ░ß╗Żng ─æiß╗üu khiß╗ān trong c├┤ng nghiß╗ćp theo tß╗½ng bit. ’āś1 Relay, 1 ─æß╗Öng cŲĪ, 1 tiß║┐p ─æiß╗āmŌĆ” ’ü▒Ca├╣c nha├Ė che├Ī ta├»o ├▒a├Ą t├Łch h├┤├»p: o Bo├ż nh├┤├╣ va├Ė o Ca├╣c thie├Īt b├▓ ngoa├»i vi o VXL ŌĆō ca├╗i tie├Īn cho phu├Ė h├┤├»p v├┤├╣i ├▒ie├Āu khie├źn CN ’ü▒Ta├»o tha├Ėnh mo├żt IC go├»i la├Ė vi ├▒ie├Āu khie├źn (Microcontroller).

- 50. 50 VI ─ÉIß╗ĆU KHIß╗éN Vi Xß╗Ł L├Į Bß╗Ö Nhß╗ø Thiß║┐t bß╗ŗ ngß╗Źai vi Vi ─Éiß╗üu Khiß╗ān

- 51. 51 Ų»U ─ÉIß╗éM Cß╗”A VI ─ÉIß╗ĆU KHIß╗éN ’üČDe├Ż s├Č├╗ du├»ng trong ca├╣c ├Č├╣ng du├»ng. ’üČKho├óng ├▒o├Ėi ho├╗i ng├Č├┤├Ėi s├Č├╗ du├»ng pha├╗i hie├źu bie├Īt l├Č├┤├»ng kie├Īn th├Č├╣c qua├╣ nhie├Āu nh├Č ng├Č├┤├Ėi s├Č├╗ du├»ng VXL. ’üČV├┤├╣i ng├Č├┤├Ėi ba├®t ├▒a├Āu th├¼ s├Č├╗ du├»ng VXL la├Ė ├▒ie├Āu ra├Īt kho├╣, ma├Īt nhie├Āu th├┤├Ėi gian, trong khi ├▒o├╣ mong muo├Īn la├Ė s├Č├╗ du├»ng ├▒├Č├┤├»c ngay.

- 52. 52 C├üC Hß╗ī VI ─ÉIß╗ĆU KHIß╗éN TH├öNG Dß╗żNG ’üČHa├Ąng ATMEL: ’āśAT89C51, AT89S51, AT89S8252, AT89S52 ’āśAVR: 8515, ATMega8, ATMega16...ŌĆ” ’üČHa├Ąng PHILIPS: 89V51RD1, 89V51RD2 ’üČHa├Ąng MICROCHIP: ’āśPIC: 16F84, 16F877A, 18F452...

- 53. 53 Hß╗å THß╗ÉNG Sß╗¼ Dß╗żNG VI ─ÉIß╗ĆU KHIß╗éN CPU ROM RAM ngoß║Īi vi (IO) Bus dß╗» liß╗ću (Data Bus) Bus ─æß╗ŗa chß╗ē (Address Bus) Bus ─æiß╗üu khiß╗ān (Control Bus) Input Output

- 54. 54 ─Éß║ČC TRŲ»NG C├üC Hß╗ī VI ─ÉIß╗ĆU KHIß╗éN ’üČNguß╗ōn cung cß║źp ’üČXung clock ’üČBß╗Ö ─æß╗ŗnh thß╗Øi (timer) ’üČWatchdog ’üČReset ’üČNgß║»t ’üČADC ’üČTruyß╗ün th├┤ng nß╗æi tiß║┐p ’üČBß╗Ö so s├Īnh analog ’üČPWM.

- 55. 55 KIß║ŠN TR├ÜC VI ─ÉIß╗ĆU KHIß╗éN ’üČVon Neumann

- 56. 56 KIß║ŠN TR├ÜC VI ─ÉIß╗ĆU KHIß╗éN ’üČHARVARD

- 57. 57 ├öN Tß║¼P Hß╗å THß╗ÉNG Sß╗É ’üČC├Īc hß╗ć thß╗æng sß╗æ hß╗Źc: ’āśThß║Łp ph├ón (decimal) ’āśNhß╗ŗ ph├ón (binary) ’āśB├Īt ph├ón (octal) ’āśThß║Łp lß╗źc ph├ón (hexadecimal) ’āśBCD ’üČChuyß╗ān ─æß╗Ģi giß╗»a c├Īc sß╗æ: ’āśDec’āåbinary ’āśBinary ’āåhex ’āśHex ’āåbinary ’āśHex ’āådec ’āśDec ’āåhex.

- 58. 58 C├üCH BIß╗éU DIß╗äN ’üČThß║Łp ph├ón: (D) ’āśVD: 82510 = 8x102 + 2 x101 + 5x100 ’üČNhß╗ŗ ph├ón: (B) ’āśVD: 11102 = 1x 23 + 1x 22 + 1x 21 + 0x 20 ’āś100011102 ’üČB├Īt ph├ón:(O) ’āśVD: 2378 = 2x 82 +3x 81 + 7x 80 ’üČThß║Łp lß╗źc ph├ón: (H) ’āśVD: 2AC16 = 2x 162 + 10x 161 + 12x 160 .

- 59. 59 CHUYß╗éN ─Éß╗öI ’üČBinary ’āå Dec ’üČDec ’āå Binary 3 2 1 0 2 101011 1 2 0 2 1 2 1 2 11= ├Ś + ├Ś + ├Ś + ├Ś = 28/2 ŌåÆ 14 dŲ░ 0 (LSB) 14/2 ŌåÆ 7 dŲ░ 0 7/2 ŌåÆ 3 dŲ░ 1 3/2 ŌåÆ 1 dŲ░ 1 1/2 ŌåÆ 0 dŲ░ 1 (MSB) ’āå 111002 .

- 61. 61 CHUYß╗éN ─Éß╗öI ’üČBinary ’ā© Hexadecimal ’āś100111112 = 1001 1111 9 F BT: 11101111000011102 ’üČHexadecimal ’ā© Binary ’āśFE3C16 ŌĆó F = 11112 ŌĆó E = 11102 ŌĆó 3 = 00112 ŌĆó C = 11002 ’ā© 11111110001111002.

- 63. 63 CHUYß╗éN ─Éß╗öI ’üČHexadecimal ’ā© Dec ’āś2AC16 = 2 x 162 + 10 x 161 + 12 x 160 = 512 + 160 + 12 = 684 ’üČDec ’ā© Hexadecimal ŌĆó 238/16 ŌåÆ 14 dŲ░ 14 (E) (LSB) ŌĆó 14/16 ŌåÆ 0 dŲ░ 14 (E) (MSB) ’ā© EE16.

- 64. 64 CHUYß╗éN ─Éß╗öI ’üČOctal ’ā© Binary ’āś1778 ŌĆó 1 = 0012 ŌĆó 7 = 1112 ŌĆó 7 = 1112 ’ā© 0011111112 ’üČBinary ’ā© Octal ’āś1101110012 ’āś110111001 = 110 111 001 6 7 1 ’ā© 6718.

- 65. 65 C├üC PH├ēP TO├üN HAI Sß╗É NHß╗Ŗ PH├éN ’üČSß╗æ ├óm ’üČCß╗Öng sß╗æ nhß╗ŗ ph├ón ’üČTrß╗½ sß╗æ nhß╗ŗ ph├ón ’üČNh├ón sß╗æ nhß╗ŗ ph├ón ’üČChia sß╗æ nhß╗ŗ ph├ón.

- 66. 66 Sß╗æ ├ém ’üČSß╗æ ├óm v├Ā dŲ░ŲĪng 4 bit

- 67. 67 C├Īch T├¼m Sß╗æ ├ém ’üČVD: -6 ’āś0110 +6 ’āś1001 b├╣ 1 cß╗Öng 1 ŌĆōŌĆōŌĆōŌĆō 1010 l├Ā sß╗æ - 6.

- 68. 68 Cß╗Öng 2 Sß╗æ Nhß╗ŗ Ph├ón ’üČC├┤ng thß╗®c: ’āś0 + 0 = 0 ’āś0 + 1 = 1 ’āś1 + 0 = 1 ’āś1 + 1 = 10 tß║Īo ra mß╗Öt bit nhß╗ø l├Ā (1) ’āś1 + 1 + 1 = 11 tß║Īo ra mß╗Öt bit nhß╗ø l├Ā (1).

- 69. 69 Cß╗Öng 2 Sß╗æ Nhß╗ŗ Ph├ón ’üČVD: 01000011 v├Ā 00100010 01000011 cß╗Öt 1: 1 + 0 = 1 + 00100010 cß╗Öt 2 : 1 + 1 = 10 ŌĆōŌĆōŌĆōŌĆōŌĆōŌĆōŌĆōŌĆōŌĆō cß╗Öt 3: 0 + nhß╗ø = 1 01100101 cß╗Öt 4 : 0 + 0 = 0 cß╗Öt 5 : 0 + 0 = 0 cß╗Öt 6 : 0 + 1 = 1 cß╗Öt 7 : 1 + 0 = 1 cß╗Öt 8 : 0 + 0 = 0.

- 70. 70 Trß╗½ 2 Sß╗æ Nhß╗ŗ Ph├ón ’üČChuyß╗ān sß╗æ bß╗ŗ trß╗½ th├Ānh sß╗æ ├óm ’üČCß╗Öng hai sß╗æ vß╗øi nhau ’āśVD: 0110 trß╗½ cho sß╗æ 0010 0010 sß╗æ bß╗ŗ trß╗½ 1101 b├╣ 1 cß╗Öng 1 ŌĆōŌĆōŌĆōŌĆō 1110 ’āśCß╗Öng lß║Īi: 0110 sß╗æ trß╗½ + 1110 sß╗æ ├óm cß╗¦a sß╗æ bß╗ŗ trß╗½ ŌĆōŌĆōŌĆōŌĆōŌĆōŌĆō 0100.

- 71. 71 Nh├ón v├Ā Chia 2 Sß╗æ Nhß╗ŗ Ph├ón ’üČC├┤ng thß╗®c nh├ón: ’āś0 x 0 = 0 ’āś0 x 1 = 0 ’āś1 x 0 = 0 ’āś1 x 1 = 1 ’üČNh├ón b├¼nh thŲ░ß╗Øng nhŲ░ nh├ón sß╗æ thß║Łp ph├ón ’üČChia: TŲ░ŲĪng tß╗▒ nhŲ░ chia 2 sß╗æ thß║Łp ph├ón.

- 72. 72

![36

EPROM

2716

A0

A1

A2

A3

A4

A5

A6

A7

A9

A10

CE

OE

VPP

D0

D1

D2

D3

D4

D5

D6

D7

OE : (output enable) [0] ─æiß╗üu khiß╗ān

cho ph├®p bß╗Ö nhß╗ø xuß║źt dß╗» liß╗ću ra b├¬n

ngo├Āi.

CE : (chip enable) [0] ─æiß╗üu khiß╗ān cho

ph├®p bß╗Ö nhß╗ø l├Ām viß╗ćc.

VPP: [1] nß║Īp dß╗» liß╗ću, chŲ░ŲĪng tr├¼nh v├Āo

bß╗Ö nhß╗ø

Chế độ CE OE Data

─Éß╗Źc 0 0 Dout

Chß╗Ø 1 XX High Z

Lß║Łp tr├¼nh

EPROM

0 XX Vpp [1]

Din](https://image.slidesharecdn.com/chuong1tongquanvxlvdk-130613052122-phpapp02/85/vxl-vdk-TranThanhPhong-36-320.jpg)