DLF-Microprocessor_02_2017-18 SAE2B microprocessor

- 2. SAE2BŌĆō Digital Electronics & Microprocessor 2 Unit : I ŌĆō Overview ’ü▒ Number System ’ü▒ Binary System ’ü▒ Binary Code ’ü▒ Logic Gates ’ü▒ Boolean Algebra ’ü▒ Truth Tables ’ü▒ Universal Gates ’ü▒ Simplification of Boolean functions ’ü▒ Karnaugh Map ’ü▒ Combinational Logic

- 3. TM SAE2BŌĆō Digital Electronics & Microprocessor 3 Number System ’ü▒ Number System is a system of representing letters or numbers in computer understandable form. ’ü▒ Examples ŌĆō Binary, Decimal, Octal and Hexadecimal Number System Base Digits or Symbols included Binary 2 0,1 Decimal 10 0,1,2,3,4,5,6,7,8,9 Octal 8 0,1,2,3,4,5,6,7 Hexadecimal 16 0,1,2,3,4,5,6,7,8,9,A, B,C,D,E,F

- 4. Binary System A binary number system is made up of only 0s and 1s. Example : 001010 ŌĆó Conversion from any Number system to Decimal ŌĆó Conversion from decimal to other system ŌĆó Conversion from Binary to Octal / Hexadecimal ŌĆó Conversion from Octal / Hexadecimal to binary ŌĆó Conversion from Decimal to other system Code Conversion SAE2BŌĆō Digital Electronics & Microprocessor 4

- 5. 5 Binary Codes ’üĄ Codes are alternate representations for the binary numbers. ’üĄ Different codes are used for binary numbers. Commonly used are 1. BCD (Binary Coded Decimal) Code a) 8421 b) 2421 c) 4221 2. Excess-3 Code 3. Gray Code SAE2BŌĆō Digital Electronics & Microprocessor

- 6. 6 Logic Gates EXCLUSIVE OR a b a.b a b a+b a a' a b (a+b)' a b (a.b)' a b a ’āģ b a b a.b & a b a+b + AND a a' 1 a b (a.b)' & a b (a+b)' ’é│1 a b a ’āģ b =1 OR NOT NAND NOR Symbol set 1 Symbol set 2 (ANSI/IEEE Standard 91-1984) SAE2BŌĆō Digital Electronics & Microprocessor

- 7. SAE2BŌĆō Digital Electronics & Microprocessor 7 ’üĄ Commutative Law A + B = B + A A . B = B . A ’üĄ Associative Law A + (B + C) = (A + B) + C A (BC) = (AB) C ’üĄ Distributive Law A (B + C) = AB + AC Boolean Algebra

- 8. SAE2BŌĆō Digital Electronics & Microprocessor 8 Rules specific to Boolean Algebra 1a. A + 0 = A 2a. A + 1 = 1 3a. A + A = A 4a. A + AŌĆÖ = 1 5a. AŌĆÖŌĆÖ = A 6a. A + AB = A 7a. A + AŌĆÖB = A + B 8a. A + BC = (A + B) (A + C) 9a. AB + AŌĆÖC + BC = AB + AŌĆÖC 1b. A . 1 = A 2b. A . 0 = 0 3b. A . A = A 4b. A . AŌĆÖ = 0 5b. AŌĆÖŌĆÖ = A 6b. A (A + B) = A 7b. A (AŌĆÖ + B) = AB 8b. A (B + C) = AB + AC 9b. (A+B) (AŌĆÖ+C) (B+C) = (A+B) (AŌĆÖ + C)

- 9. SAE2BŌĆō Digital Electronics & Microprocessor 9 ŌĆó The AND and OR functions can be shown to be related to each other through the following equations. Theorem 1: ŌĆĢThe complement of a product is equal to the sum of individual complements.ŌĆ¢ In other words, (AB)ŌĆś = AŌĆś + BŌĆś or NAND = Bubbled OR Theorem 2: ŌĆĢThe complement of a sum is equal to the product of individual complements.ŌĆ¢ In other words, (A + B)ŌĆś = AŌĆś . BŌĆś or NOR = Bubbled AND DemorganŌĆÖs Laws

- 10. SAE2BŌĆō Digital Electronics & Microprocessor 10 Truth Table A truth table is a mathematical table used in logicŌĆöspecifically in connection with Boolean algebra and Boolean functions - which sets out the functional values of logical expressions on each of their functional arguments, that is, for each combination of values taken by their logical variables.

- 11. SAE2BŌĆō Digital Electronics & Microprocessor 11 ’üĄ Universal gates are the ones which can be used for implementing any gate like AND, OR and NOT, or any combination of these basic gates. ’üĄ NAND and NOR gates are universal gates. ’üĄ But there are some rules that need to be followed when implementing NAND or NOR based gates. Universal Gates

- 12. SAE2BŌĆō Digital Electronics & Microprocessor 12 Sum of Products and Product of Sums Any given truth table can be converted into a logical expression, by either SOP or POS method. ŌĆó To obtain SOP expression, a) Take the cases where output is a logical 1 b) Represent each case as a product of the variables, such that output is 1. This product is known as a minterm. c) ORing the minterms gives us the SOP expression. ŌĆó To obtain POS expression, a) Take the cases where output is a logical 0. b) Represent each case as a sum of the variables, such that output is 0. This product is known as a maxterm. c) ANDing the maxterms gives us the POS expression.

- 13. SAE2BŌĆō Digital Electronics & Microprocessor 13 ŌĆó Karnaugh maps provide a systematic method to obtain simplified sum-of- products (SOPs) Boolean expressions. ŌĆó This is a compact way of representing a truth table and is a technique that is used to simplify logic expressions. ŌĆó It is ideally suited for four or less variables, becoming cumbersome for five or more variables. ŌĆó A K-map of n variables will have 2n squares. ŌĆó Each square represents either a minterm or maxterm. ŌĆó For a Boolean expression, product terms are denoted by 1's, while sum terms are denoted by 0's - but 0's are often left blank. Karnaugh Maps (K-Maps)

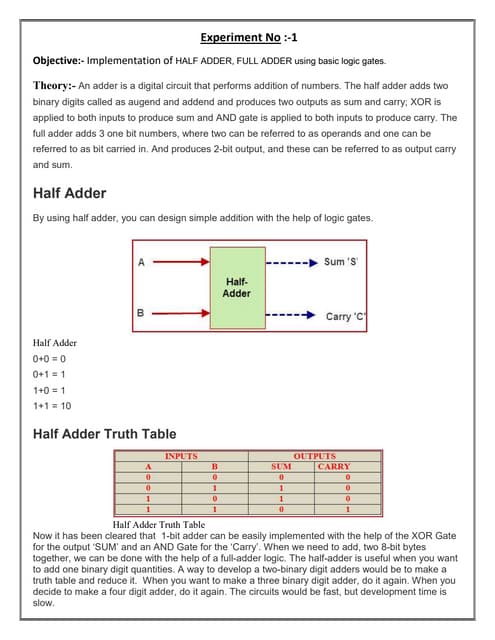

- 14. SAE2BŌĆō Digital Electronics & Microprocessor 14 A combinational circuit can have an n number of inputs and m number of outputs. . Combinational Logic Some of the Combinational circuits are 1. Half Adder 2. Full Adder 3. Half Subtractor 4. Full subtractor

- 15. SAE2BŌĆō Digital Electronics & Microprocessor 15 Combinational Logic Design also holds 1. Decoder 2. Encoder 3. Multiplexer 4. Demultiplexer Combinational Logic Design

- 16. SAE2BŌĆō Digital Electronics & Microprocessor Unit : II ŌĆō Overview ’ü▒ Sequential Logic ’ü▒ Flip-Flops ’ü▒ Shift Register ’ü▒ Counters 16

- 17. SAE2BŌĆō Digital Electronics & Microprocessor 17 ’ü▒ The outputs of a sequential logic circuit depend on both the current inputs and on previous inputs and outputs of the circuit. ’ü▒ Sequential elements have storage elements that record the state of the circuit. In other words, the state information combined with the inputs is generating the outputs. ’ü▒ The state and inputs also combine to generate a new state of the circuit. ’ü▒ The same inputs in a sequential circuit may generate different outputs and different new states, depending on the circuitŌĆÖs current state. Sequential Logic

- 18. SAE2BŌĆō Digital Electronics & Microprocessor 18 ’ü▒ A bi-stable device i.e. a circuit with only 2 stable states, namely the ŌĆś0ŌĆÖ state and the ŌĆś1ŌĆÖ state. ’ü▒ Ability to retain its state and store a bit of information. ’ü▒ It is one-bit memory cell. ’ü▒ A flip-flop has 2 outputs and they complement each other. ’ü▒ Types of Flip Flop ŌĆō SR Flip Flop, JK Flip Flop, D Flip Flop, T Flip Flop. Flip-Flops

- 19. SAE2BŌĆō Digital Electronics & Microprocessor 19 ’ü▒ A common form of register used in computers and in many other types of logic circuits is a shift register. ’ü▒ It is simply a set of flip flops (usually D latches or RS flip-flops) connected together so that the output of one becomes the input of the next, and so on in series. ’ü▒ It is called a shift register because the data is shifted through the register by one bit position on each clock pulse. Shift Register

- 20. SAE2BŌĆō Digital Electronics & Microprocessor 20 Serial-in Serial-out Register ’ü▒ On the leading edge of the first clock pulse, the signal on the D input is latched in the first flip flop. ’ü▒ On the leading edge of the next clock pulse, the contents of the first flip- flop is stored in the second flip-flop, and the signal which is present at the D input is stored is the first flip-flop, etc. ’ü▒ Because the data is entered one bit at a time, this called a serial-in shift register. Since there is only one output, and data leaves the shift register one bit at a time, then it is also a serial out shift register.

- 21. SAE2BŌĆō Digital Electronics & Microprocessor 21 Parallel-in Parallel-out Register ’ü▒ Parallel input can be provided through the use of the preset and clear inputs to the flip-flop. ’ü▒ The parallel loading of the flip-flop can be synchronous (i.e., occurs with the clock pulse) or asynchronous (independent of the clock pulse) depending on the design of the shift register. ’ü▒ Parallel output can be obtained from the outputs of each flip-flop as shown in Figure.

- 22. SAE2BŌĆō Digital Electronics & Microprocessor 22 Counters ’ü▒ Counter is a register which counts the sequence in binary form. ’ü▒ The state of counter changes with application of clock pulse. ’ü▒ The counter is binary or non-binary. ’ü▒ The total number of states in counter is called as modulus. ’ü▒ If counter is modulus-n, then it has n different states. ’ü▒ State diagram of counter is a pictorial representation of counter states directed by arrows in graph. 000 100 111 110 101 001 010 011 State diagram of mod-8 counter

- 23. SAE2BŌĆō Digital Electronics & Microprocessor 23 Asynchronous (Ripple) Counters ’ü▒ All Flip-Flops are in toggle mode. ’ü▒ The clock input is applied. ’ü▒ Count enable = 1. ’ü▒ Counter counts from 0000 to 1111.

- 24. SAE2BŌĆō Digital Electronics & Microprocessor 24 In synchronous counters, the clock inputs of all the flip-flops are connected together and are triggered by the input pulses. Thus, all the flip-flops change state simultaneously (in parallel). ’ü▒ After the 3rd clock pulse, both outputs of FF0 and FF1 are HIGH. The positive edge of the 4th clock pulse will cause FF2 to change its state due to the AND gate. Synchronous Counter ’ü▒ The J and K inputs of FF0 are connected to HIGH. FF1 has its J and K inputs connected to the output of FF0, and the J and K inputs of FF2 are connected to the output of an AND gate that is fed by the outputs of FF0 and FF1.

- 25. SAE2BŌĆō Digital Electronics & Microprocessor 25 Up / Down Counter Bidirectional counters, also known as Up/Down counters, are capable of counting in either direction through any given count sequence and they can be reversed at any point within their count sequence by using an additional control input

- 26. SAE2BŌĆō Digital Electronics & Microprocessor Unit : II ŌĆō Overview ’ü▒Microprocessors ’ü▒Microprocessor Architecture ’ü▒Peripheral/Externally Initiated Operations ’ü▒Memory and its classification ’ü▒8085 Instruction Set ’ü▒ Addressing Modes 26

- 27. SAE2BŌĆō Digital Electronics & Microprocessor 27 Microprocessors ’āś Multipurpose, clock-driven, register-based electronic device. ’āś Reads binary instructions from memory. ’āś Accepts data as input. ’āś Process data according to instructions. ’āś Provides result as output.

- 28. SAE2BŌĆō Digital Electronics & Microprocessor 28 ’ü▒ A microcomputer is a small, relatively inexpensive computer with a microprocessor as its central processing unit (CPU). ’ü▒ It includes a microprocessor, memory, and minimal input/output (I/O) circuitry mounted on a single printed circuit board. Micro Computer Assembly Language ’ü▒ An assembly language is a low-level programming language for microprocessors and other programmable devices. ’ü▒ An assembly language implements a symbolic representation of the machine code needed to program a given CPU architecture. ’ü▒ Assembly language is also known as assembly code.

- 29. SAE2BŌĆō Digital Electronics & Microprocessor 29 Microprocessor Architecture ’é¦ Microprocessor is digital device designed with ’é¦ Register ’é¦ Flip-flop ’é¦ Timing element

- 30. SAE2BŌĆō Digital Electronics & Microprocessor 30 8085 Bus Structure

- 31. SAE2BŌĆō Digital Electronics & Microprocessor 31 Address Bus ’āś Group of 16 lines generally identified as A0 to A15. ’āś It is unidirectional (bits flow in one direction). ’āś Identifies the peripherals or a memory location through these line. ’āś Carry a 16-bit address. ’āś Capable of identifying 216 = 65,536 (64K) memory locations.

- 32. SAE2BŌĆō Digital Electronics & Microprocessor 32 Data Bus ’āś Group of 8 lines used for data flow (D0 to D7) ’āśBidirectional : data flow both direction between MPU and memory and peripherals. ’āś The largest number that can appear on the data bus is 1111 1111 (i.e. 25510) ’āśHandles up to 28=256 (i.e 00 to FF ) numbers.

- 33. SAE2BŌĆō Digital Electronics & Microprocessor 33 Control Bus ’āś Comprised of various signal lines that carry synchronization signals. ’āś MPU generates specific control signal for every operation. ’āś Used to identify the device type which MPU intends to communicate. ’āś Eg: To read data from the memory MPU sends the control signal called Memory Read.

- 34. SAE2BŌĆō Digital Electronics & Microprocessor 34 8085 Pin Diagram and Signals

- 35. SAE2BŌĆō Digital Electronics & Microprocessor 35 Classifications of the functions 1. Microprocessor-initiated operations. 2. Internal operations. 3. Peripheral (or externally) initiated operations.

- 36. SAE2BŌĆō Digital Electronics & Microprocessor 36 Internal Data Operations ’ü▒Internal architecture of the 8085 microprocessor determines how and what operations can be performed. ’ü▒The operations are: ’ü▒ Store 8-bit data. ’ü▒ Perform arithmetic and logical operations. ’ü▒ Test for conditions. ’ü▒ Sequence the execution of instruction. ’ü▒Store data temporarily in the Stack.

- 37. SAE2BŌĆō Digital Electronics & Microprocessor 37 Peripheral/Externally Initiated Operations ’ü▒ External devices can initiate the MPU operations. ’ü▒ Individual pins on the MPU chip are assigned for various operations like: ’āś Reset ’āś Interrupt ’āś Ready ’āś Hold

- 38. SAE2BŌĆō Digital Electronics & Microprocessor 38 ’āś Two basic categories of computer memory: ŌĆō Primary stores small amounts of data and information that will be immediately used by the CPU. ŌĆō Secondary stores much larger amounts of data and information (an entire software program, for example) for extended periods of time. Memory and its classification

- 39. SAE2BŌĆō Digital Electronics & Microprocessor 39 Memory and Instruction Fetch ’āś All instructions are stored in memory. ’āś To run a program, the individual instructions must be read from the memory in sequence, and executed. ’āś Instruction fetch ’āś Decode instruction ’āś Get operands ’āś Execute operation

- 40. SAE2BŌĆō Digital Electronics & Microprocessor 40 Instruction Fetch Operation

- 41. SAE2BŌĆō Digital Electronics & Microprocessor 41 8085 Instruction Set ’āś An instruction is a binary pattern designed inside a microprocessor to perform a specific function. ’āśThe entire group of instructions that a microprocessor supports is called Instruction Set. ’āś 8085 has 246 instructions. ’āśEach instruction is represented by an 8-bit binary value. ’āśThese 8-bits of binary value is called Op-Code or Instruction Byte.

- 42. SAE2BŌĆō Digital Electronics & Microprocessor 42 Addressing Modes ’ü▒ Every instruction has to operate on a data. ’ü▒The method of specifying the data to be operated by the instruction is called Addressing. ’ü▒The 8085 has 5 types of addressing: 1. Immediate Addressing 2. Direct Addressing 3. Register Addressing 4. Register Indirect Addressing. 5. Implied Addressing

- 43. SAE2BŌĆō Digital Electronics & Microprocessor 43 Arithmetic Operations The 8085 microprocessor performs various arithmetic operations, such as addition, subtraction, increment, and decrement. 1.ADD 2.ADI 3.SUB 4.SUI 5.INR 6.DCR

- 44. SAE2BŌĆō Digital Electronics & Microprocessor 44 ’āśMicroprocessor is basically a programmable logic chip. ’āśIt can perform all the logic functions of the hard-wired logic through its instruction set. ’āśThey are: ’āś AND ’āś OR ’āś Ex OR ’āś NOT Logical Operations

- 45. SAE2BŌĆō Digital Electronics & Microprocessor 45 Branching Instructions ’āś Most powerful instructions because they allow the microprocessor to change the sequence of a program. ’āś Change may be unconditional or under certain test conditions. ’āś Instruct the microprocessor to go to a different memory location. ’āś Types: 1. Jump Instructions. 2. Call and Return instructions. 3. Restart instructions.

- 46. SAE2BŌĆō Digital Electronics & Microprocessor 46 Jump Instructions ’āś Specify the memory location explicitly. ’āś They are 3-byte instructions. ’āś One byte for operation code, followed by a 16-bit memory address. ’āś Classified into: 1. Unconditional Jump. 2. Conditional Jump.

- 47. SAE2BŌĆō Digital Electronics & Microprocessor 47 JMP 16-bit address: ’āś Jump unconditionally ’āś The program sequence is transferred to the memory location specified by the 16-bit address given in the operand. Example: JMP 2034H or JMP XYZ(Label name) Unconditional Jump

- 48. SAE2BŌĆō Digital Electronics & Microprocessor 48 Conditional Jumps ’āś Allow the microprocessor to make decisions based on certain conditions indicated by flags. ’āś Check the flag conditions to change or not. ’āś Flags used by jump instructions: 1. Carry flag 2. Zero flag 3. Sign flag 4. Parity flag

- 49. SAE2BŌĆō Digital Electronics & Microprocessor Unit : IV ŌĆō Overview ’ü▒ Time Delay Using One Register ’ü▒ Time Delay Using a Register Pair ’ü▒ Using a Loop within Loop Technique ’ü▒ Counter Design with Time Delay ’ü▒ Stack and Subroutines ’ü▒ BCD to Binary Conversion and Vice-versa ’ü▒ BCD to HEX Conversion and Vice-versa ’ü▒ Binary to ASCII Conversion and Vice-versa ’ü▒ BCD Addition and Subtraction 49

- 50. SAE2BŌĆō Digital Electronics & Microprocessor 50 Time Delay ’āś Procedure used to design a specific delay. ’āś A register is loaded with a number , depending on the time delay required and then the register is decremented until it reaches zero by setting up a loop with conditional jump instruction. ’āś Time delay using One register:

- 51. SAE2BŌĆō Digital Electronics & Microprocessor 51 Time Delay using Register Pair Label Opcode Operand Comments T state LXI B,2384H Load BC with 16-bit count 10 LOOP: DCX B Decrement BC by 1 6 MOV A,C Place contents of C in A 4 ORA B OR B with C to set Zero flag 4 JNZ LOOP if result not equal to 0 , 10/7 jump back to loop Time Delay in Loop TL= T * Loop T states * N10 = 0.5 * 24* 9092 = 109 ms Time Delay using LOOP within a LOOP MVI B,38H 7T Delay in Loop TL1=1783.5 ╬╝s LOOP2: MVI C,FFH 7T Delay in Loop TL2= (0.5*21+TL1)*56 LOOP1: DCR C 4T =100.46ms JNZ LOOP1 10/7 T DCR B 4T JNZ LOOP 2 10/7T

- 52. SAE2BŌĆō Digital Electronics & Microprocessor 52 Flowchart of a counter with time delay

- 53. SAE2BŌĆō Digital Electronics & Microprocessor 53 ’ü▒ STACK is a group of memory location in the R/W memory that is used for temporary storage of binary information during the execution of a program. ’ü▒ The programmer can store and retrieve the contents of a register pair by using PUSH and POP. The Stack

- 54. SAE2BŌĆō Digital Electronics & Microprocessor 54 ’é¦ A subroutine is a group of instructions that will be used repeatedly in different locations of the program. ’āś Rather than repeat the same instructions several times, they can be grouped into a subroutine that is called from the different locations. ’āś Instructions used in subroutine are CALL, RET,RTE and RST SUBROUTINE

- 55. SAE2BŌĆō Digital Electronics & Microprocessor 55 SOLUTION: ’āś Step 1: 0111 0010 -> 0000 0010 Unpacked BCD1. -> 0000 0111 Unpacked BCD2. ’āś Step 2: Multiply BCD2 by 10 = (7x10) ’āś Step 3: Add BCD1 to the answer in step2 Example:7210=01110010BCD BCD - TO - BINARY CONVERSION

- 56. SAE2BŌĆō Digital Electronics & Microprocessor 56 SOLUTION: ’āś Step 1: 0111 0010 -> 0000 0010 Unpacked BCD1. -> 0000 0111 Unpacked BCD2. ’āś Step 2: Multiply BCD2 by 10 = (7x10) ’āś Step 3: Add BCD1 to the answer in step2 Example:7210=01110010BCD BCD - TO - BINARY CONVERSION

- 57. SAE2BŌĆō Digital Electronics & Microprocessor 57 BINARY-TO-BCD CONVERSION Example : Assume the binary number is 1111 1111 2(FFH)=25510 To represent this number in BCD requires twelve bits or three BCD digits, labeled here as BCD3 (MSB) ,BCD2 and BCD1(LSB). =0010 0101 0101 BCD3 BCD2 BCD1

- 58. SAE2BŌĆō Digital Electronics & Microprocessor 58 BCD to HEX conversion ’ü▒ Initialize memory pointer to 4150H. ’ü▒ Get the most significant Digit(MSD) ’ü▒ Multiply the MSD by ten using repeated addition ’ü▒ Add the least significant digit (LSD)to the result to obtained in previous step. ’ü▒ Store hex data in memory. ’ü▒ Input :4150:02(MSD), 4151:09(LSD) ’ü▒ Output:4152:1DH

- 59. SAE2BŌĆō Digital Electronics & Microprocessor 59 HEX to BCD Conversion ’āś Initialize memory pointer to 4150H. ’āś Get the hexa decimal number ’āś Perform repeated addition for n number of times ’āś Adjust for BCD in each step ’āś Store BCD data in memory. Input :4150:FF Output: 4151:55(LSD) 4152:02(MSD)

- 60. SAE2BŌĆō Digital Electronics & Microprocessor 60 BINARY TO ASCII LDA 2050H : Take the binary number in the accumulator CPA 0AH : Compare the given number with 0AH JC SKIP 7 : If number < 9 no need to add 7 ADI 07H : Else, add 7 to the accumulator SKIP 7 : ADI 30H :Add 30h to accumulator STA 2051H :Store the ASCII result in memory HLT :End the program

- 61. SAE2BŌĆō Digital Electronics & Microprocessor 61 BCD ADDITION ’āś The 8085 provides a special instruction DAA(decimal adjust accumulator) to perform BCD addition. ’āś The DAA instruction is included immediately after an addition or increment instruction. ’āś The maximum in two digit BCD(8 bits) is 99.

- 62. SAE2BŌĆō Digital Electronics & Microprocessor 62 BCD Subtraction ’āś The DAA cannot be used directly to perform BCD subtraction because DAA instruction requires an addition to be performed first. ’āś So, 10ŌĆśs complement method is employed. Example : 85-39 9ŌĆśs complement of 39=99-39=60 (each digit is subtracted from 9) 10ŌĆśs complement of 39=9ŌĆśs complement+1=60+1=61 Therefore 85+61=46(with carry 1(should be omitted))

- 63. SAE2BŌĆō Digital Electronics & Microprocessor Unit : V ŌĆō Overview ’ü▒ Interrupt ’ü▒ Vectored Interrupts ’ü▒ Interfacing I/O Devices ’ü▒ Basic Interfacing Concepts ’ü▒ DMA 63

- 64. SAE2BŌĆō Digital Electronics & Microprocessor 64 Interrupts ’üĮ Interrupt is a process where an external device can get the attention of the microprocessor. ŌŚ” The process starts from the I/O device ŌŚ” The process is asynchronous. TYPES OF INTERRUPT SOFTWARE HARDWARE VECTORED AND NON VECTORED

- 65. SAE2BŌĆō Digital Electronics & Microprocessor 65 The 8085 Interrupts Interrupt name Maskable Vectored VECTOR ADDRESS TRAP No Yes 0024H RST 7.5 Yes Yes 003CH RST 6.5 Yes Yes 0034H RST 5.5 Yes Yes 002CH INTR Yes No --

- 66. SAE2BŌĆō Digital Electronics & Microprocessor 66 8085 Interrupts

- 67. The 8085 Vectored Interrupt Process In vectored interrupts, the processor automatically branches to the specific address in response to an interrupt. SAE2BŌĆō Digital Electronics & Microprocessor 67

- 68. SAE2BŌĆō Digital Electronics & Microprocessor 68 The 8085 Non-Vectored Interrupt Process 1. The interrupt process should be enabled using the EI instruction. 2. The 8085 checks for an interrupt during the execution of every instruction. 3. If INTR is high, MP completes current instruction, disables the interrupt and sends INTA (Interrupt acknowledge) signal to the device that interrupted 4. INTA allows the I/O device to send a RST instruction through data bus. 5. Upon receiving the INTA signal, MP saves the memory location of the next instruction on the stack and the program is transferred to ŌĆŚcallŌĆś location (ISR Call) specified by the RST instruction

- 69. 6. Microprocessor Performs the ISR. 7. ISR must include the ŌĆŚEIŌĆś instruction to enable the further interrupt within the program. 8. RET instruction at the end of the ISR allows the MP to retrieve the return address from the stack and the program is transferred back to where the program was interrupted. The 8085 Non-Vectored Interrupt Process SAE2BŌĆō Digital Electronics & Microprocessor 69

- 70. SAE2BŌĆō Digital Electronics & Microprocessor 70 Interface is the path for communication between two components. Interfacing is of two types, memory interfacing and I/O interfacing. Basic Interfacing Concepts

- 71. SAE2BŌĆō Digital Electronics & Microprocessor 71 Direct Memory Access ’āś Process of communication or data transfer controlled by an external peripheral. ’āś Ex: Data transfer between a floppy and R/W memory of the system. ’āś 8085A has two pins for this type of communication ŌĆó HOLD ŌĆó HLDA

- 72. SAE2BŌĆō Digital Electronics & Microprocessor 72 Direct Memory Access 0 ROM RAM Peripherals DMA C n Memory Mapped I/O Time to do 1000 xfers in 1 msec: 1 DMA set-up sequence: @ 50 msec 1 interrupt: @ 2 msec 1 interrupt service sequence: @ 48 msec 100msec .0001 second of CPU time CPU sends a starting address, direction(R/W), and word count to DMAC. Then issues "start". DMAC provides; Peripheral controller Handshake signals Memory Addresses Handshake signals CPU IOC device Memory DMAC I/O