Electronic devices-and-circuit-theory-10th-ed-boylestad-chapter-13

- 1. Chapter 13 Linear-Digital ICs

- 2. Linear Digital ICs Comparators Digital/analog converters Timers Voltage-controlled oscillators Phase-locked loop circuits Interface circuits Copyright ┬®2009 by Pearson Education, Inc. Upper Saddle River, New Jersey 07458 ŌĆó All rights reserved. Electronic Devices and Circuit Theory, 10/e Robert L. Boylestad and Louis Nashelsky 2

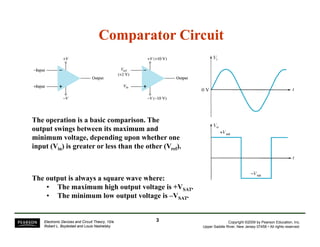

- 3. Comparator Circuit The operation is a basic comparison. The output swings between its maximum and minimum voltage, depending upon whether one input (Vin) is greater or less than the other (Vref). The output is always a square wave where: ŌĆó The maximum high output voltage is +VSAT. ŌĆó The minimum low output voltage is ŌĆōVSAT. Copyright ┬®2009 by Pearson Education, Inc. Upper Saddle River, New Jersey 07458 ŌĆó All rights reserved. Electronic Devices and Circuit Theory, 10/e Robert L. Boylestad and Louis Nashelsky 3

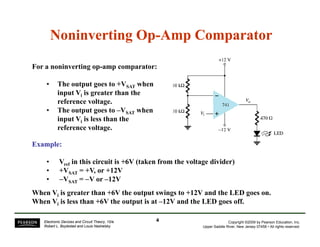

- 4. Noninverting Op-Amp Comparator For a noninverting op-amp comparator: ŌĆó The output goes to +VSAT when input Vi is greater than the reference voltage. ŌĆó The output goes to ŌĆōVSAT when input Vi is less than the reference voltage. Example: ŌĆó Vref in this circuit is +6V (taken from the voltage divider) ŌĆóŌĆó +VSAT = +V, or +12V ŌĆó ŌłÆVSAT = ŌłÆV or ŌĆō12V When Vi is greater than +6V the output swings to +12V and the LED goes on. When V is less than +6V the 12V off Vi output is at ŌĆōand the LED goes off. Copyright ┬®2009 by Pearson Education, Inc. Upper Saddle River, New Jersey 07458 ŌĆó All rights reserved. Electronic Devices and Circuit Theory, 10/e Robert L. Boylestad and Louis Nashelsky 4

- 5. Inverting Op-Amp Comparator For an inverting op-amp comparator: ŌĆó The output goes to ŌĆōVSAT when input Vi is greater than the reference voltage. ŌĆó The output goes to +VSAT when input Vi is less than the reference voltage. Example: ŌĆó Vref in this circuit is +6V (taken from the voltage divider) ŌĆóŌĆó +VSAT = +V, or +12V ŌĆó ŌłÆVSAT = ŌłÆV or ŌĆō12V When Vi is greater than +6V the output swings to ŌĆō12V and the LED goes off. When V is less than +6V the on Vi output is at +12V and the LED goes on. Copyright ┬®2009 by Pearson Education, Inc. Upper Saddle River, New Jersey 07458 ŌĆó All rights reserved. Electronic Devices and Circuit Theory, 10/e Robert L. Boylestad and Louis Nashelsky 5

- 6. Comparator ICs Advantages: ŌĆó Faster switching ŌĆó Built-in noise immunity ŌĆó Outputs capable of directly driving loads Copyright ┬®2009 by Pearson Education, Inc. Upper Saddle River, New Jersey 07458 ŌĆó All rights reserved. Electronic Devices and Circuit Theory, 10/e Robert L. Boylestad and Louis Nashelsky 6

- 7. Digital-Analog Converters Types: ŌĆó Digital-to-analog converters (ADCs) ŌĆó Analog-to-digital converters (DACs) Copyright ┬®2009 by Pearson Education, Inc. Upper Saddle River, New Jersey 07458 ŌĆó All rights reserved. Electronic Devices and Circuit Theory, 10/e Robert L. Boylestad and Louis Nashelsky 7

- 8. Digital-to Analog Converter: Ladder Network Version Output Voltage, Vo: 3 D 2 D 2 D 2 D 2 3 2 2 4 ref 1 1 0 0 o V 2 V ├Ś + ├Ś + ├Ś + ├Ś = ref 2 4 V Voltage Resolution: Copyright ┬®2009 by Pearson Education, Inc. Upper Saddle River, New Jersey 07458 ŌĆó All rights reserved. Electronic Devices and Circuit Theory, 10/e Robert L. Boylestad and Louis Nashelsky 8

- 9. Analog-to-Digital Converters Types: ŌĆó Dual Slope Conversion ŌĆó Ladder Network Conversion Copyright ┬®2009 by Pearson Education, Inc. Upper Saddle River, New Jersey 07458 ŌĆó All rights reserved. Electronic Devices and Circuit Theory, 10/e Robert L. Boylestad and Louis Nashelsky 9

- 10. Analog-to-Digital Conversion Dual Slope Conversion The analog input voltage is applied to an integrator or ramp-generator circuit. The digital output is obtained from a digital counter that is operated during both positive and negative slope (ramp) intervals of the integrator. Copyright ┬®2009 by Pearson Education, Inc. Upper Saddle River, New Jersey 07458 ŌĆó All rights reserved. Electronic Devices and Circuit Theory, 10/e Robert L. Boylestad and Louis Nashelsky 10

- 11. Dual Slope Conversion Rising Slope For a fixed interval the analog voltage is applied to the integrator. The integrator output rises to some positive level. This positive voltage is applied to a comparator. At the end of the fixed interval, the counter is reset to 0. An electronic switch connects the integrator input to a fixed input or reference voltage. Falling Slope The integrator output decreases at a fixed rate. The counter advances during this time. When the integrator output (connected to the comparator input) falls below the reference level of the comparator comparator, control logic stops the counter counter.The digital counter output is the digital conversion of the analog input. Copyright ┬®2009 by Pearson Education, Inc. Upper Saddle River, New Jersey 07458 ŌĆó All rights reserved. Electronic Devices and Circuit Theory, 10/e Robert L. Boylestad and Louis Nashelsky 11

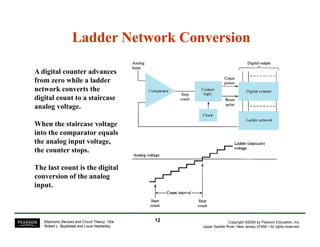

- 12. Ladder Network Conversion A digital counter advances from zero while a ladder network converts the digital count to a staircase analog voltage. When the staircase voltage into the comparator equals the analog input voltage, the counter stops. The last count is the digital conversion of the analog input. Copyright ┬®2009 by Pearson Education, Inc. Upper Saddle River, New Jersey 07458 ŌĆó All rights reserved. Electronic Devices and Circuit Theory, 10/e Robert L. Boylestad and Louis Nashelsky 12

- 13. Resolution of Analog-to-Digital Converters The resolution depends on the amount of voltage per step (digital bit): ref 2 n V where n is the number of digital bits Example: A 12-bit ADC with a 10V reference level has the following resolution: V ref = 10V = 2.4mV 2n 212 12 Copyright ┬®2009 by Pearson Education, Inc. Upper Saddle River, New Jersey 07458 ŌĆó All rights reserved. Electronic Devices and Circuit Theory, 10/e Robert L. Boylestad and Louis Nashelsky 13

- 14. Analog-to-Digital Conversion Time The conversion time depends on the clock frequency of the counter. T 2 n f conv = where Tconv = conversion time (seconds) n = number of binary bits f = clock frequency for the counter Example: A 12bit ADC with a 1MHz clock has a maximum conversion time. 4.1ms 212 ŌÄø 1 ŌÄ× 1MHz ŌĤŌÄĀ = ŌÄ£ŌÄØ Copyright ┬®2009 by Pearson Education, Inc. Upper Saddle River, New Jersey 07458 ŌĆó All rights reserved. Electronic Devices and Circuit Theory, 10/e Robert L. Boylestad and Louis Nashelsky 14

- 15. 555 Timer Circuit The 555 Timer is an example of a versatile Timer IC. Astable Operation The timer output is a repetitive square wave. The output frequency can be calculated as shown here. Copyright ┬®2009 by Pearson Education, Inc. Upper Saddle River, New Jersey 07458 ŌĆó All rights reserved. Electronic Devices and Circuit Theory, 10/e Robert L. Boylestad and Louis Nashelsky 15

- 16. 555 Timer Circuit Monostable Operation The timer output is a one shot pulse. When an input is received it triggers a one shot pulse. The time for which the output remains high can be calculated as shown. Copyright ┬®2009 by Pearson Education, Inc. Upper Saddle River, New Jersey 07458 ŌĆó All rights reserved. Electronic Devices and Circuit Theory, 10/e Robert L. Boylestad and Louis Nashelsky 16

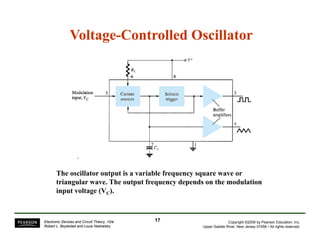

- 17. Voltage-Controlled Oscillator The oscillator output is a variable frequency square wave or triangular wave. The output frequency depends on the modulation input voltage (VC). Copyright ┬®2009 by Pearson Education, Inc. Upper Saddle River, New Jersey 07458 ŌĆó All rights reserved. Electronic Devices and Circuit Theory, 10/e Robert L. Boylestad and Louis Nashelsky 17

- 18. 566 Voltage-Controlled Oscillator The output frequency can be calculated as shown in the graph. Note that the formula also indicates other circuit parameters that affect the output frequency. Copyright ┬®2009 by Pearson Education, Inc. Upper Saddle River, New Jersey 07458 ŌĆó All rights reserved. Electronic Devices and Circuit Theory, 10/e Robert L. Boylestad and Louis Nashelsky 18

- 19. Phase-Locked Loop The input signal is a frequency and the output signal is a voltage representing the difference in frequency between the input and the internal VCO. Copyright ┬®2009 by Pearson Education, Inc. Upper Saddle River, New Jersey 07458 ŌĆó All rights reserved. Electronic Devices and Circuit Theory, 10/e Robert L. Boylestad and Louis Nashelsky 19

- 20. Basic Operation of the Phase-Locked Loop Three operating modes: Lock fi = fVCO Tracking fi ŌēĀ fVCO, but the fVCO adjusts until fVCO= fi Out-of-Lock fi ŌēĀŌēĀ fVCO, and they never will be the same Copyright ┬®2009 by Pearson Education, Inc. Upper Saddle River, New Jersey 07458 ŌĆó All rights reserved. Electronic Devices and Circuit Theory, 10/e Robert L. Boylestad and Louis Nashelsky 20

- 21. Phase-Locked Loop: Lock Mode The input frequency and the internal VCO output frequency are applied to the phase comparator. If they are the same, the phase comparator output voltage indicates no error. This no-error voltage is filtered and amplified before it is made available to the output. The no-error voltage is also applied to the internal VCO input to maintain the VCOŌĆÖs output frequency. Copyright ┬®2009 by Pearson Education, Inc. Upper Saddle River, New Jersey 07458 ŌĆó All rights reserved. Electronic Devices and Circuit Theory, 10/e Robert L. Boylestad and Louis Nashelsky 21

- 22. Phase-Locked Loop: Tracking Mode If the input frequency does not equal the VCO frequency then the phase comparator outputs an error voltage. This error voltage is filtered and amplified and made available to the output. The error voltage is also applied to the VCO input. This causes the VCO to change output frequency. This looping continues until the VCO has adjusted to the new input frequency and they are equal again. Copyright ┬®2009 by Pearson Education, Inc. Upper Saddle River, New Jersey 07458 ŌĆó All rights reserved. Electronic Devices and Circuit Theory, 10/e Robert L. Boylestad and Louis Nashelsky 22

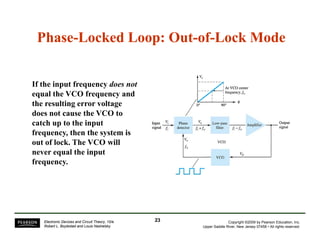

- 23. Phase-Locked Loop: Out-of-Lock Mode If the input frequency does not equal the VCO frequency and the resulting error voltage does not cause the VCO to catch up to the input frequency, then the system is out of lock. The VCO will never equal the input frequency. Copyright ┬®2009 by Pearson Education, Inc. Upper Saddle River, New Jersey 07458 ŌĆó All rights reserved. Electronic Devices and Circuit Theory, 10/e Robert L. Boylestad and Louis Nashelsky 23

- 24. Phase-Locked Loop: Frequency Ranges Lock RangeŌĆöThe range of input frequencies for which the VCO will track. Capture Range ŌĆöA narrow range of frequencies into which the input frequency must fall before the VCO can track. If the input frequency falls out of the lock range it must first enter into the capture range. Copyright ┬®2009 by Pearson Education, Inc. Upper Saddle River, New Jersey 07458 ŌĆó All rights reserved. Electronic Devices and Circuit Theory, 10/e Robert L. Boylestad and Louis Nashelsky 24

- 25. Phase-Locked Loop Applications: ŌĆó FM demodulator ŌĆó Frequency Synthesizer ŌĆó FSK decoder Copyright ┬®2009 by Pearson Education, Inc. Upper Saddle River, New Jersey 07458 ŌĆó All rights reserved. Electronic Devices and Circuit Theory, 10/e Robert L. Boylestad and Louis Nashelsky 25

- 26. Interface Circuitry Interface circuitry: ŌĆó Driving loads ŌĆó Producing output signals at proper voltage or current levels ŌĆó Impedance matching ŌĆó Strobing or timing signals Copyright ┬®2009 by Pearson Education, Inc. Upper Saddle River, New Jersey 07458 ŌĆó All rights reserved. Electronic Devices and Circuit Theory, 10/e Robert L. Boylestad and Louis Nashelsky 26

- 27. Interface Circuitry: Dual Line Drivers The input is TTL digital logic signal levels. The output is capable of driving TTL or CMOS devise circuits. Copyright ┬®2009 by Pearson Education, Inc. Upper Saddle River, New Jersey 07458 ŌĆó All rights reserved. Electronic Devices and Circuit Theory, 10/e Robert L. Boylestad and Louis Nashelsky 27

- 28. RS-232-to-TTL Converter The input is RS-232 electronic industry standard for serial communications. The output will drive TTL circuitry. Copyright ┬®2009 by Pearson Education, Inc. Upper Saddle River, New Jersey 07458 ŌĆó All rights reserved. Electronic Devices and Circuit Theory, 10/e Robert L. Boylestad and Louis Nashelsky 28