Fajrul fallah

- 1. Shift Register Pengertian dan Penggunaanya By: Fajrul fallah

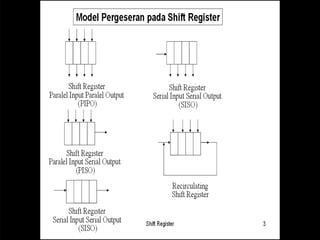

- 2. Shift Register adalah suatu register dimana informasi dapat bergeser (digeserkan). Dalam register geser flip-flop saling dikoneksi, sehingga isinya dapat digeserkan dari satu flip- flop ke flip-flop yang lain, kekiri atau kekanan atas perintah denyut lonceng (Clock).

- 3. Dalam alat ukur digit, register dipakai untuk mengingat data yang sedang ditampilkan. Ada 4 Shift Register yaitu: 1.SISO (Serial Input Serial Output) • Register geser SISO ada tiga macam yaitu: a) Shift Right Register (SRR)/Register geser kanan b) Shift Left Register (SLR)/Register geser kiri c) Shift Control Register dapat berfungsi sebagai SSR maupun SLR

- 4. 2.Register Geser SIPO • Adalah register geser dengan masukan data secara serial dan keluaran data secara parelel. • Cara kerja: • Masukan-masukan data secara deret akan dikeluarkan oleh D-FF setelah masukan denyut lonceng dari 0 ke 1. Keluaran data/informasi serial akan dapat dibaca secara paralel setelah diberikan satu komando (Read Out). Bila dijalan masuk Read Out diberi logik 0, maka semua keluaran AND adalah 0 dan bila Read Out diberi logik 1, maka pintu-pintu AND menghubung langsungkan sinyal-sinyal yang ada di Q masing-masing flip-flop.

- 5. 3.Register Geser PIPO • Adalah register geser dengan masukan data secara jajar/paralel dan keluaran jajar/paralel. • Cara kerja: • Sebelum dimasuki data rangkaian direset dulu agar keluaran Q semuanya 0. Setelah itu data dimasukkan secara paralel pada input D-FF dan data akan diloloskan keluar secara paralel setelah flip-flop mendapat pulsa clock dari 0 ke 1.

- 6. 4.Register geser PISO • Adalah register geser dengan masukan data secara paralel dan dikeluarkan secara deret/serial. • Rangkaian diatas merupakan register geser dengan panjang kata 4 bit. Semua jalan masuk clock dihubungkan jajar. Data-data yang ada di A, B, C, D dimasukkan ke flip-flop secara serempak, apabila dijalan masuk Data Load diberi logik 1.