FPGA ve VHDL Ders - 2

- 1. FPGA Alanda Programlanabilir Kapı Dizisi Dr. Serkan ¶Ů·ˇ¸é·ˇł˘Ä°

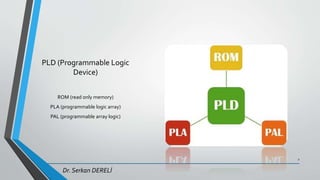

- 2. PLD (Programmable Logic Device) ROM (read only memory) PLA (programmable logic array) PAL (programmable array logic) 2 Dr. Serkan ¶Ů·ˇ¸é·ˇł˘Ä°

- 3. FPGATarihçesi 3 1966 • PROM Programlanabilir yalnızca okunabilir bellek ĂĽretimi 1969 • PROM Ticari olarak eriĹźilebilir duruma geldi 1971 • EPROM Silinebilir ve tekrar programlanabilir bellek ĂĽretimi gerçekleĹźti 1975 • PLA Programlanabilir mantık dizileri geliĹźtirildi. 1980 • PAL Programlanabilir dizi mantığı yapısı geliĹźtirildi. Dr. Serkan ¶Ů·ˇ¸é·ˇł˘Ä°

- 4. ROM (Read Only Memory) Yalnızca okunabilir bellek 4 Dr. Serkan ¶Ů·ˇ¸é·ˇł˘Ä°

- 5. PLA (Programmable Logic Array) - 1975 Programlanabilir Mantık Dizisi; giriĹźleri AND kapısı karşılarken çıkışlar OR kapısıyla sonlanır. Her iki kapı tĂĽrĂĽ de deÄźiĹźtirilebilir Ĺźekildedir. 5 Dr. Serkan ¶Ů·ˇ¸é·ˇł˘Ä°

- 6. PAL (Programmable Array Logic) - 1980 Programlanabilir Dizi Mantığı; giriĹźleri programlanabilir baÄźlantılarla oluĹźturulmaktadır. OR kapılarının baÄźlı olduÄźu çıkışlar ise sabit baÄźlantılar ile oluĹźturulur. Devrenin daha sade olması için bir bölĂĽm sabit baÄźlantı Ĺźekline dönĂĽĹźtĂĽrĂĽlmĂĽĹźtĂĽr. 6 Dr. Serkan ¶Ů·ˇ¸é·ˇł˘Ä°

- 7. CPLD (Complex PLD) - 1982 Ä°htiyaçlar arttığından devrelerin bĂĽyĂĽmesi gerekti. 7 Dr. Serkan ¶Ů·ˇ¸é·ˇł˘Ä°

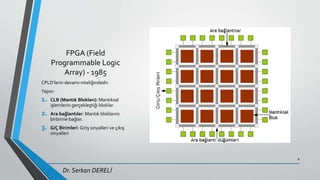

- 8. FPGA (Field Programmable Logic Array) - 1985 CPLD’lerin devamı niteliÄźindedir. Yapısı: 1. CLB (Mantık Blokları): Mantıksal iĹźlemlerin gerçekleĹźtiÄźi bloklar. 2. Ara baÄźlantılar: Mantık bloklarını birbirine baÄźlar. 3. G/Ç Birimleri: GiriĹź sinyalleri ve çıkış sinyalleri 8 Dr. Serkan ¶Ů·ˇ¸é·ˇł˘Ä°

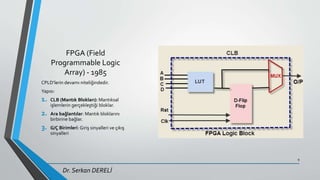

- 9. FPGA (Field Programmable Logic Array) - 1985 CPLD’lerin devamı niteliÄźindedir. Yapısı: 1. CLB (Mantık Blokları): Mantıksal iĹźlemlerin gerçekleĹźtiÄźi bloklar. 2. Ara baÄźlantılar: Mantık bloklarını birbirine baÄźlar. 3. G/Ç Birimleri: GiriĹź sinyalleri ve çıkış sinyalleri 9 Dr. Serkan ¶Ů·ˇ¸é·ˇł˘Ä°

- 10. Nexys 4 DDR • 15850 CLB • Her bir CLB’de 4 adet 6 giriĹźli LUT ve 8 adet FF 10 Dr. Serkan ¶Ů·ˇ¸é·ˇł˘Ä°

- 11. FPGAYapısı 11 Dr. Serkan ¶Ů·ˇ¸é·ˇł˘Ä°Dr. Serkan ¶Ů·ˇ¸é·ˇł˘Ä°

- 12. FPGA Ara baÄźlantı Düğümleri 12 Dr. Serkan ¶Ů·ˇ¸é·ˇł˘Ä°

- 13. Ă–rnekAra baÄźlantı DüğümüÇalışması 13 Dr. Serkan ¶Ů·ˇ¸é·ˇł˘Ä°

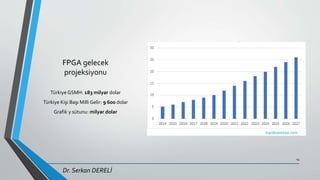

- 14. FPGA gelecek projeksiyonu TĂĽrkiye GSMH: 183 milyar dolar TĂĽrkiye KiĹźi Başı Milli Gelir: 9 600 dolar Grafik y sĂĽtunu: milyar dolar 14 Dr. Serkan ¶Ů·ˇ¸é·ˇł˘Ä°

- 15. FPGATasarım Akışı Sayısal devre tasarımlarının başından sonuna kadar geçireceği evrimdir. 15

- 16. FPGATasarım Akışı 16 Tasarım (VHDL veya Verilog) SimĂĽlasyon Sentezleme Lojik Elemanlar (NETLISTS) Ă–lçekleme (Mapping) YerleĹźtirme (Place) Yönlendirme (Route) Program (Bitstream) Dr. Serkan ¶Ů·ˇ¸é·ˇł˘Ä°

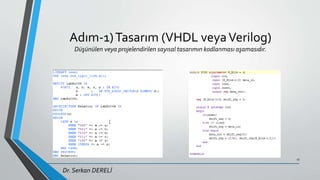

- 17. Adım-1)Tasarım (VHDL veyaVerilog) DüşünĂĽlen veya projelendirilen sayısal tasarımın kodlanması aĹźamasıdır. 17 Dr. Serkan ¶Ů·ˇ¸é·ˇł˘Ä°

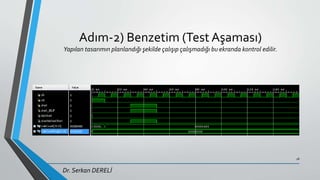

- 18. Adım-2) Benzetim (Test AĹźaması) Yapılan tasarımın planlandığı Ĺźekilde çalışıp çalışmadığı bu ekranda kontrol edilir. 18 Dr. Serkan ¶Ů·ˇ¸é·ˇł˘Ä°

- 19. Adım-3) Sentezleme (Synthesis) Kodun mantıksal karşılığının oluĹźturulduÄźu Ĺźemadır. 19 Dr. Serkan ¶Ů·ˇ¸é·ˇł˘Ä°

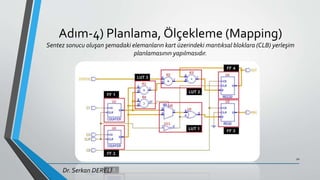

- 20. Adım-4) Planlama, Ă–lçekleme (Mapping) Sentez sonucu oluĹźan Ĺźemadaki elemanların kart ĂĽzerindeki mantıksal bloklara (CLB) yerleĹźim planlamasının yapılmasıdır. 20 Dr. Serkan ¶Ů·ˇ¸é·ˇł˘Ä°

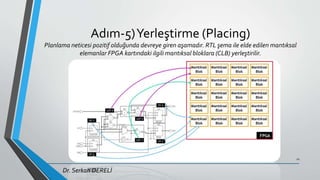

- 21. Adım-5)YerleĹźtirme (Placing) Planlama neticesi pozitif olduÄźunda devreye giren aĹźamadır. RTL Ĺźema ile elde edilen mantıksal elemanlar FPGA kartındaki ilgili mantıksal bloklara (CLB) yerleĹźtirilir. 21 Dr. Serkan ¶Ů·ˇ¸é·ˇł˘Ä°

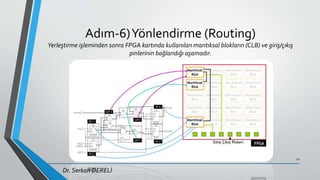

- 22. Adım-6)Yönlendirme (Routing) YerleĹźtirme iĹźleminden sonra FPGA kartında kullanılan mantıksal blokların (CLB) ve giriĹź/çıkış pinlerinin baÄźlandığı aĹźamadır. 22 Dr. Serkan ¶Ů·ˇ¸é·ˇł˘Ä°

- 23. Bölüm Sonu 23