FPGA ve VHDL Ders - 3

- 1. FPGA Alanda Programlanabilir Kap─▒ Dizisi Dr. Serkan DEREL─░ dereli@subu.edu.tr

- 2. VHDL (Very High Definition Language) ŌĆó VHSIC (Very High-Speed Integrated Circuit) ifadesinden d├Čn├╝┼¤t├╝r├╝lm├╝┼¤t├╝r. ŌĆó Donan─▒m tasar─▒m─▒ yapmak i├¦in kullan─▒l─▒r. ŌĆó ─░lk olarak USA Savunma Bakanl─▒─¤─▒nca kullan─▒ld─▒. Sonradan IEEE enstit├╝s├╝ne devredildi. ŌĆó ─░lk olarak 1987 y─▒l─▒nd─▒ standartla┼¤t─▒. ŌĆó Son olarak 1993 y─▒l─▒nda g├╝ncelle┼¤ti. Hali haz─▒rda kullan─▒lan kodlar bu s├╝r├╝me aittir. 2 Dr. Serkan DEREL─░ (dereli@subu.edu.tr)

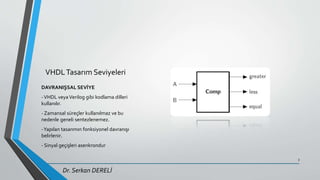

- 3. VHDLTasar─▒m Seviyeleri DAVRANI┼×SAL SEV─░YE -VHDL veyaVerilog gibi kodlama dilleri kullan─▒l─▒r. - Zamansal s├╝re├¦ler kullan─▒lmaz ve bu nedenle geneli sentezlenemez. -Yap─▒lan tasar─▒m─▒n fonksiyonel davran─▒┼¤─▒ belirlenir. - Sinyal ge├¦i┼¤leri asenkrondur 3 Dr. Serkan DEREL─░

- 4. VHDLTasar─▒m Seviyeleri RTL (Register Transfer Level) Seviyesi -Toplay─▒c─▒ ve kar┼¤─▒la┼¤t─▒r─▒c─▒ gibi fonksiyonel birimlerle beraber depolama ve veri se├¦ici (├¦oklay─▒c─▒) birimleri bar─▒nd─▒r─▒r. - Ortak bir saat sinyali kullan─▒l─▒r. - Sinyal gecikmeleri ve anl─▒k atlamalar sistemin ├¦al─▒┼¤mas─▒n─▒ etkilemez. 4 Dr. Serkan DEREL─░

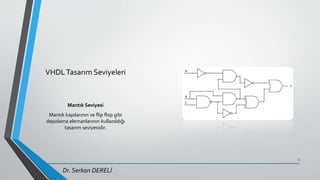

- 5. VHDLTasar─▒m Seviyeleri Mant─▒k Seviyesi Mant─▒k kap─▒lar─▒n─▒n ve flip flop gibi depolama elemanlar─▒n─▒n kullan─▒ld─▒─¤─▒ tasar─▒m seviyesidir. 5 Dr. Serkan DEREL─░

- 6. VHDLTasar─▒m Seviyeleri Donan─▒m (FPGA) Seviyesi En alt seviye tasar─▒m modelidir. Yap─▒lan tasar─▒mlar donan─▒m─▒n mant─▒k bloklar─▒na fiziksel olarak yerle┼¤tirilir. 6 Dr. Serkan DEREL─░

- 7. FPGA gelecek projeksiyonu 7 Dr. Serkan DEREL─░

- 8. D├╝nya b├Člgeler haritas─▒ 8 Dr. Serkan DEREL─░ (dereli@subu.edu.tr)

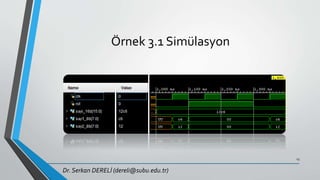

- 9. ├¢RNEK 3.1. Giri┼¤ine gelen 4-bitlik iki say─▒dan b├╝y├╝k, k├╝├¦├╝k veya e┼¤itlik durumlar─▒n─▒ ├¦─▒k─▒┼¤a aktaran devre tasar─▒m─▒n─▒ yap─▒n─▒z. 9 Dr. Serkan DEREL─░ (dereli@subu.edu.tr)

- 10. Ûrnek 3.1.VHDL kodu 10 Dr. Serkan DERELİ (dereli@subu.edu.tr)

- 11. Ûrnek 3.1 Simülasyon 11 Dr. Serkan DERELİ (dereli@subu.edu.tr)

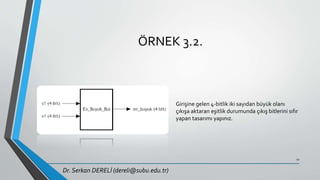

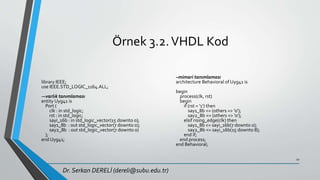

- 12. ├¢RNEK 3.2. Giri┼¤ine gelen 4-bitlik iki say─▒dan b├╝y├╝k olan─▒ ├¦─▒k─▒┼¤a aktaran e┼¤itlik durumunda ├¦─▒k─▒┼¤ bitlerini s─▒f─▒r yapan tasar─▒m─▒ yap─▒n─▒z. 12 Dr. Serkan DEREL─░ (dereli@subu.edu.tr)

- 13. VHDLTasar─▒m Modelleri ŌĆó Veri ak─▒┼¤ (Data Flow) modeli ŌĆó Davran─▒┼¤sal (Behavioral) model ŌĆó Yap─▒sal (Structural) Model 13 Dr. Serkan DEREL─░

- 14. Davran─▒┼¤sal Model ŌĆó Tasarlanan devrenin ├¦─▒k─▒┼¤lar─▒n─▒n giri┼¤lerine verdi─¤i tepkiyi modelleyen bir tasar─▒m stilidir. ŌĆó Devrenin giri┼¤ sinyallerine g├Čre davran─▒┼¤─▒n─▒ modellemektedir. ŌĆó Tasar─▒mc─▒ a├¦─▒s─▒ndan mant─▒k kap─▒lar─▒ y├Čn├╝yle devrenin nas─▒l g├Čr├╝nd├╝─¤├╝nden ziyade davran─▒┼¤─▒ ├Čnemlidir. 14 Dr. Serkan DEREL─░ (dereli@subu.edu.tr)

- 15. Yap─▒sal Model ŌĆó Bu modelde ger├¦ekle┼¤tirilen devre bir b├╝t├╝n olarak d├╝┼¤├╝n├╝ld├╝─¤├╝nde alt-tasar─▒mlar─▒n (component) bir araya getirdi─¤i bir sistem olarak ├Čn plana ├¦─▒kmaktad─▒r. ŌĆó Asl─▒nda bu sistemi bir araya getiren her bir alt- tasar─▒m davran─▒┼¤sal olarak ger├¦ekle┼¤tirilen tasar─▒m modellerinden olu┼¤maktad─▒r. ŌĆó G├╝n├╝m├╝zde yayg─▒n ┼¤ekilde kullan─▒m─▒ olan bu model ├Čzellikle b├╝y├╝k sistem tasar─▒mlar─▒nda tasar─▒mc─▒ya ziyadesiyle fayda sa─¤lamaktad─▒r. 15 Dr. Serkan DEREL─░ (dereli@subu.edu.tr)

- 16. VHDLTasar─▒m Bile┼¤enleri VHDL Tasar─▒m K├╝t├╝phana (Library) Varl─▒k (Entity) Mimari (Architecture) ŌĆó K├╝t├╝phane (Library) ŌĆó Varl─▒k (Entity) ŌĆó Mimari (Architecture) 16 Dr. Serkan DEREL─░ (dereli@subu.edu.tr)

- 17. K├╝t├╝phaneler (Libraries) ŌĆó use IEEE.std_logic_1164.all; std_logic, std_logic_vector t├╝rleri ile ilgili fonksiyonlar─▒ i├¦erir. ŌĆó use IEEE.numeric_std.all; std_logic_arith k├╝t├╝phanesinin alternatifidir. ŌĆó use IEEE.std_logic_signed.all; i┼¤aretli aritmetik fonksiyonlar─▒ i├¦erir. ŌĆó use IEEE.std_logic_arith.all; signed, unsigned, integer ve std_logic_vector t├╝rleri i├¦in aritmetik, d├Čn├╝┼¤t├╝rme ve kar┼¤─▒la┼¤t─▒rma fonksiyonlar─▒n─▒ i├¦erir. VHDL tasar─▒mda kullan─▒lacak kodlar─▒n i┼¤levlerini i├¦eren yap─▒lard─▒r. 17 Dr. Serkan DEREL─░ (dereli@subu.edu.tr)

- 18. Varl─▒k (Entity) entity Uyg41 is Port ( clk : in std_logic; rst : in std_logic; sayi_16b : in std_logic_vector(15 downto 0); say1_8b : out std_logic_vector(7 downto 0); say2_8b : out std_logic_vector(7 downto 0) ); end Uyg41; Tasar─▒m─▒n giri┼¤ de─¤erleri ile ├¦─▒k─▒┼¤ de─¤erlerinin tan─▒mland─▒─¤─▒ b├Čl├╝md├╝r. 18 Dr. Serkan DEREL─░ (dereli@subu.edu.tr)

- 19. Mimari (Architecture) 1. architecture Behavioral of Uyg41 is 2. ŌĆō sinyal ve de─¤i┼¤ken tan─▒mlamalar─▒ 3. begin 4. process1(clk,rst); 5. process2(say); 6. process3(esit); 7. ŌĆ” 8. end Behavioral; ŌĆó Yap─▒lan bir tasar─▒m─▒n ne i┼¤ yapt─▒─¤─▒ tam olarak bu b├Čl├╝mde tan─▒mlanmaktad─▒r. ŌĆó Tasarlanan sistemin s─▒ral─▒ veya paralel bir ┼¤ekilde ├¦al─▒┼¤aca─¤─▒ da bu b├Čl├╝mde ortaya ├¦─▒kmaktad─▒r. 19 Dr. Serkan DEREL─░ (dereli@subu.edu.tr)

- 20. ICT (information and communication technology)ŌĆÖyi elinde bulunduran 10 ├╝lke Kaynak: World Economic Forum https://www.weforum.org/agenda/2014 /04/top-10-countries-embracing- information-technology/ 20 Dr. Serkan DEREL─░ (dereli@subu.edu.tr)

- 21. ├¢RNEK 3.3. Giri┼¤ine gelen 16-bitlik say─▒y─▒ 8-bit ve 8-bit olmak ├╝zere ikiye b├Člerek ├¦─▒k─▒┼¤a aktaran VHDL tasar─▒m─▒ ger├¦ekle┼¤tiriniz. 21 Dr. Serkan DEREL─░ (dereli@subu.edu.tr)

- 22. ├¢rnek 3.2.VHDL Kod library IEEE; use IEEE.STD_LOGIC_1164.ALL; -ŌĆōvarl─▒k tan─▒mlamas─▒ entity Uyg41 is Port ( clk : in std_logic; rst : in std_logic; sayi_16b : in std_logic_vector(15 downto 0); say1_8b : out std_logic_vector(7 downto 0); say2_8b : out std_logic_vector(7 downto 0) ); end Uyg41; ŌĆōmimari tan─▒mlamas─▒ architecture Behavioral of Uyg41 is begin process(clk, rst) begin if (rst = '1') then say1_8b <= (others => '0'); say2_8b <= (others => '0'); elsif rising_edge(clk) then say1_8b <= sayi_16b(7 downto 0); say2_8b <= sayi_16b(15 downto 8); end if; end process; end Behavioral; 22 Dr. Serkan DEREL─░ (dereli@subu.edu.tr)

- 23. Ûrnek 3.1 Simülasyon 23 Dr. Serkan DERELİ (dereli@subu.edu.tr)

- 24. B├Čl├╝m Sonu 24