FPGA ve VHDL Ders - 4

- 1. FPGA Alanda Programlanabilir Kap? Dizisi Dr. Serkan DEREL? dereli@subu.edu.tr

- 2. VHDLTasar?m Bile?enleri VHDL Tasar?m K©╣t©╣phana (Library) Varl?k (Entity) Mimari (Architecture) ? K©╣t©╣phane (Library) ? Varl?k (Entity) ? Mimari (Architecture) 2 Dr. Serkan DEREL? (dereli@subu.edu.tr)

- 3. K©╣t©╣phaneler (Libraries) ? use IEEE.std_logic_1164.all; std_logic, std_logic_vector t©╣rleri ile ilgili fonksiyonlar? i?erir. ? use IEEE.numeric_std.all; std_logic_arith k©╣t©╣phanesinin alternatifidir. ? use IEEE.std_logic_signed.all; i?aretli aritmetik fonksiyonlar? i?erir. ? use IEEE.std_logic_arith.all; signed, unsigned, integer ve std_logic_vector t©╣rleri i?in aritmetik, d?n©╣?t©╣rme ve kar??la?t?rma fonksiyonlar?n? i?erir. VHDL tasar?mda kullan?lacak kodlar?n i?levlerini i?eren yap?lard?r. 3 Dr. Serkan DEREL? (dereli@subu.edu.tr)

- 4. Varl?k (Entity) entity Uyg41 is Port ( clk : in std_logic; rst : in std_logic; sayi_16b : in std_logic_vector(15 downto 0); say1_8b : out std_logic_vector(7 downto 0); say2_8b : out std_logic_vector(7 downto 0) ); end Uyg41; Tasar?m?n giri? de?erleri ile ??k?? de?erlerinin tan?mland??? b?l©╣md©╣r. 4 Dr. Serkan DEREL? (dereli@subu.edu.tr)

- 5. Mimari (Architecture) 1. architecture Behavioral of Uyg41 is 2. ©C sinyal ve de?i?ken tan?mlamalar? 3. begin 4. process1(clk,rst); 5. process2(say); 6. process3(esit); 7. ĪŁ 8. end Behavioral; ? Yap?lan bir tasar?m?n ne i? yapt??? tam olarak bu b?l©╣mde tan?mlanmaktad?r. ? Tasarlanan sistemin s?ral? veya paralel bir ?ekilde ?al??aca?? da bu b?l©╣mde ortaya ??kmaktad?r. 5 Dr. Serkan DEREL? (dereli@subu.edu.tr)

- 6. ?RNEK 4.1. Giri?ine gelen 16-bitlik say?y? 8-bit ve 8-bit olmak ©╣zere ikiye b?lerek ??k??a aktaran VHDL tasar?m? ger?ekle?tiriniz. 6 Dr. Serkan DEREL? (dereli@subu.edu.tr)

- 7. ?rnek 4.1.VHDL Kod library IEEE; use IEEE.STD_LOGIC_1164.ALL; -©Cvarl?k tan?mlamas? entity Uyg41 is Port ( clk : in std_logic; rst : in std_logic; sayi_16b : in std_logic_vector(15 downto 0); say1_8b : out std_logic_vector(7 downto 0); say2_8b : out std_logic_vector(7 downto 0) ); end Uyg41; ©Cmimari tan?mlamas? architecture Behavioral of Uyg41 is begin process(clk, rst) begin if (rst = '1') then say1_8b <= (others => '0'); say2_8b <= (others => '0'); elsif rising_edge(clk) then say1_8b <= sayi_16b(7 downto 0); say2_8b <= sayi_16b(15 downto 8); end if; end process; end Behavioral; 7 Dr. Serkan DEREL? (dereli@subu.edu.tr)

- 8. ?rnek 4.1. Sim©╣lasyon 8 Dr. Serkan DEREL? (dereli@subu.edu.tr)

- 9. VHDL Nesneleri veVeriTipleri 9 Dr. Serkan DEREL? (dereli@subu.edu.tr)

- 10. VHDL Nesneleri 10 Dr. Serkan DEREL? (dereli@subu.edu.tr) ? Sinyaller (Signal) ? De?i?kenler (Variable) ? Sabitler (Constaint)

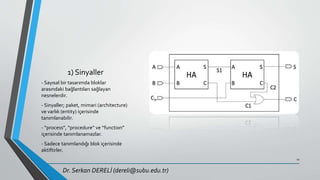

- 11. 1) Sinyaller - Say?sal bir tasar?mda bloklar aras?ndaki ba?lant?lar? sa?layan nesnelerdir. - Sinyaller; paket, mimari (architecture) ve varl?k (entity) i?erisinde tan?mlanabilir. - Ī░processĪ▒, Ī░procedureĪ▒ ve Ī░functionĪ▒ i?erisinde tan?mlanamazlar. - Sadece tan?mland??? blok i?erisinde aktiftirler. 11 Dr. Serkan DEREL? (dereli@subu.edu.tr)

- 12. Sinyaller ?RNEK 4.2. Sisteme gelen 8-bitlik bir say?n?n pozitif mi yoksa negatif mi oldu?unu ??k??a aktaran tasar?m? yap?n?z. 12 Dr. Serkan DEREL? (dereli@subu.edu.tr)

- 13. Sinyaller 13 Dr. Serkan DEREL? (dereli@subu.edu.tr)

- 14. ?rnek 4.2.VHDL Kod (Sinyal) library IEEE; use IEEE.STD_LOGIC_1164.ALL; entity isaret_biti is Port ( clk: in std_logic; rst: in std_logic; sayi: in std_logic_vector(7 downto 0); isaret: out std_logic ); end isaret_biti; ©Cmimari tan?mlamas? architecture Behavioral of isaret_biti is signal msb_bit: std_logic; begin process(clk,rst begin if rst='1' then isaret <= 'U'; elsif rising_edge(clk) then msb_bit <= sayi(7); if msb_bit='1' then isaret <= '1'; else isaret <= '0'; end if; end if; end process; end Behavioral; 14 Dr. Serkan DEREL? (dereli@subu.edu.tr)

- 15. ?rnek 4.2. Sim©╣lasyon (Sinyal) 15 Dr. Serkan DEREL? (dereli@subu.edu.tr)

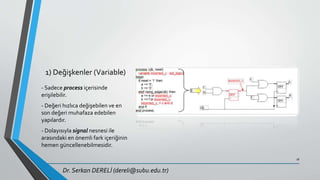

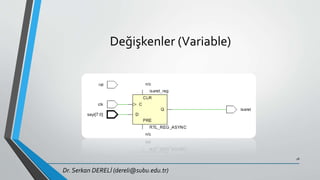

- 16. 1) De?i?kenler (Variable) - Sadece process i?erisinde eri?ilebilir. - De?eri h?zl?ca de?i?ebilen ve en son de?eri muhafaza edebilen yap?lard?r. - Dolay?s?yla signal nesnesi ile aras?ndaki en ?nemli fark i?eri?inin hemen g©╣ncellenebilmesidir. 16 Dr. Serkan DEREL? (dereli@subu.edu.tr)

- 17. De?i?kenler (Variable) ?RNEK 4.3. Sisteme gelen 8-bitlik bir say?n?n pozitif mi yoksa negatif mi oldu?unu ??k??a aktaran tasar?m? yap?n?z. 17 Dr. Serkan DEREL? (dereli@subu.edu.tr)

- 18. De?i?kenler (Variable) 18 Dr. Serkan DEREL? (dereli@subu.edu.tr)

- 19. ?rnek 4.3.VHDL Kod (Sinyal) varl?ktan?mlamas? ibrary IEEE; use IEEE.STD_LOGIC_1164.ALL; entity isaret_biti is Port ( clk: in std_logic; rst: in std_logic; sayi: in std_logic_vector(7 downto 0); isaret: out std_logic ); end isaret_biti; ©Cmimari tan?mlamas? architecture Behavioral of isaret_biti is begin process(clk,rst) variable msb_bit: std_logic; begin if rst='1' then isaret <= 'U'; elsif rising_edge(clk) then msb_bit := sayi(7); if msb_bit='1' then isaret <= '1'; else isaret <= '0'; end if; end if; end process; end Behavioral; 19 Dr. Serkan DEREL? (dereli@subu.edu.tr)

- 20. ?rnek 4.3. Sim©╣lasyon (Variable) 20 Dr. Serkan DEREL? (dereli@subu.edu.tr)

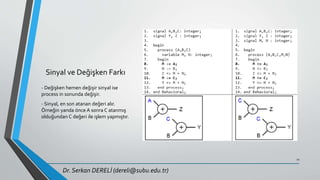

- 21. Sinyal ve De?i?ken Fark? - De?i?ken hemen de?i?ir sinyal ise process in sonunda de?i?ir. - Sinyal, en son atanan de?eri al?r. ?rne?in yanda ?nce A sonra C atanm?? oldu?undan C de?eri ile i?lem yapm??t?r. 21 Dr. Serkan DEREL? (dereli@subu.edu.tr)

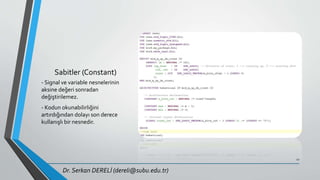

- 22. Sabitler (Constant) - Signal ve variable nesnelerinin aksine de?eri sonradan de?i?tirilemez. - Kodun okunabilirli?ini art?rd???ndan dolay? son derece kullan??l? bir nesnedir. 22 Dr. Serkan DEREL? (dereli@subu.edu.tr)

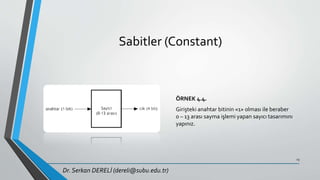

- 23. Sabitler (Constant) ?RNEK 4.4. Giri?teki anahtar bitinin ?1? olmas? ile beraber 0 ©C 13 aras? sayma i?lemi yapan say?c? tasar?m?n? yap?n?z. 23 Dr. Serkan DEREL? (dereli@subu.edu.tr)

- 24. Sabitler (Constant) 24 Dr. Serkan DEREL? (dereli@subu.edu.tr)

- 25. ?rnek 4.4.VHDL Kod (Sabitler) architecture Behavioral of sayici is constant ust: std_logic_vector(3 downto 0):="1101"; begin process (clk,rst) variable say : std_logic_vector(3 downto 0) := (others=>'0'); variable an : std_logic := '0'; ------------------------------- begin if (rst='1') then say := (others=>'0'); elsif rising_edge(clk) then an := anahtar; ------------------------------------------ if an='1' then say := say + 1; if say=ust then say := "0000"; end if; else null; end if; cik <= say; end if; end process; end Behavioral; Varl?ktan?mlamas? library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.STD_LOGIC_SIGNED.ALL; entity sayici is Port ( clk: in std_logic; rst: in std_logic; anahtar: in std_logic; cik: out std_logic_vector(3 downto 0) ); end sayici; 25 Dr. Serkan DEREL? (dereli@subu.edu.tr)

- 26. ?rnek 4.4. Sim©╣lasyon (Sabitler) 26 Dr. Serkan DEREL? (dereli@subu.edu.tr)

- 27. ?rnek 4.4.VHDL Kod (Sinyal Kullan?m?) architecture Behavioral of sayici is constant ust: std_logic_vector(3 downto 0):="1101"; signal an: std_logic := '0'; -------------------------------------- begin process(clk,rst) variable say : std_logic_vector(3 downto 0) := (others=>'0'); --variable an : std_logic := '0'; begin if (rst='1') then say := (others=>'0'); elsif rising_edge(clk) then an <= anahtar; ------------------------------------- if an='1' then say := say + 1; if say="1101" then say := "0000"; end if; else null; end if; cik <= say; end if; end process; end Behavioral; Varl?ktan?mlamas? library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.STD_LOGIC_SIGNED.ALL; entity sayici is Port ( clk: in std_logic; rst: in std_logic; anahtar: in std_logic; cik: out std_logic_vector(3 downto 0) ); end sayici; 27 Dr. Serkan DEREL? (dereli@subu.edu.tr)

- 28. ?rnek 4.4. Sim©╣lasyon (Sinyal) 28

- 29. B?l©╣m Sonu 29