introduction to embedded-converted new one

- 1. By: Dr. Vikas Mahor Department of Electronics Engineering Introduction to Embedded System

- 2. What is an Embedded System? ’üČ Embedded : means hidden inside so one canŌĆÖt see it . ’üČ System : means multiple components interfaced together for Doing specific task. ’üČ Embedded System : is a special-purpose computer system designed to perform certain dedicated functions. ’üČ Functionalities : are done by dedicated HW and SW with limited resources. ’üČ On average, a person interacts with 100s of embedded systems on daily basis.

- 3. What is an Embedded System?

- 4. Embedded Systems - Examples ŌĆó Any PC Mouse, Keyboard, or USB Device. ŌĆó Microcontroller: 8-bit.

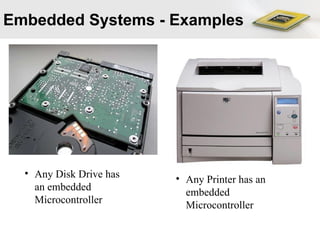

- 5. Embedded Systems - Examples ŌĆó Any Disk Drive has an embedded Microcontroller ŌĆó Any Printer has an embedded Microcontroller

- 6. Embedded Systems - Examples ŌĆó Product: Creative Labs Zen Vision:MVideo & MP3 Player. ŌĆó Microcontroller: TI TMS320 DSP. ŌĆó Canon EOS 30D Digital Camera. ŌĆó DIGIC II Image Processor.

- 7. Embedded Systems - Examples ŌĆó NASA's Twin Mars Rovers. ŌĆó Microprocessor: Radiation Hardened 20MHz PowerPC From IBM ŌĆó Commercial Real-time OS. ŌĆó Software and OS was developed during multi- year flight to Mars and downloaded using a radio link.

- 8. Embedded Systems - Examples ŌĆó Agilent Oscilloscope. ŌĆó Microprocessor: X86. ŌĆó OS: Windows XP. ŌĆó Product: Atronic Slot Machine. ŌĆó Microprocessor: X86. ŌĆó OS: Windows CE.

- 9. Embedded Systems - Examples ŌĆó Sphero BB-8 ŌĆó ARM Cortex-M4 core 32bit From ST

- 10. Embedded Systems - Examples Sphero BB-8 From inside

- 11. Embedded Systems - Examples ŌĆó BMW 745i ŌĆó Windows CE OS. ŌĆó 53 8-bit ┬ĄP. ŌĆó 11 32-bit ┬ĄP. ŌĆó 7 16-bit ┬ĄP. ŌĆó Multiple Networks.

- 12. Embedded Systems - Examples ŌĆó Sony Aiborobotic dog. ŌĆó Microprocessor: 64-bits MIPS RISC.

- 13. Embedded Systems - Examples

- 15. Computer Hardware Microprocessor A Large Memory: (Primary & Secondary) (Ram ,Rom ,Cache) Input Units: (Mouse, Keyboard ,Scanner ,et c.) Output Units: (Monitor ,Printer ,etc.) I/O Units: (FAX ,Ethernet,etc.) Storage Units: (Hard disk.)

- 18. Embedded System Hardware Microcontroller which contain : Processor, Timers, Interrupt controller, I/O Devices, Memories, Ports, etc. All on Single Chip Or System On Chip (SOC).

- 20. Microprocessor Microcontroller Higher Clock speed Slower clock speed CPU is stand-alone, RAM, ROM, I/O, timer are separate CPU,RAM, ROM, I/O and timer are all on a single chip Designer can decide on the amount of ROM, RAM and I/O ports Fix amount of on-chip ROM, RAM, I/O ports Expansive Cheap General-purpose Single-purpose High Access time for memory Low Access time for memory Very High power Low power

- 21. CPU Architectures 1) Princeton Architecture (Von Neumann Architecture) : Between 1945 & 1951 John von Neumann set down the structure, layout, interaction, cooperation, realization , implementation, functionality and activity for the whole computer as a system. The Von Neumann Architecture is characterized by: - ’üČ A memory, arithmetical-logical unit (ALU), control unit, input and output deviceŌĆ”. etc. ’üČ All parts of a computer are connected together by Bus. ’üČ Memory and Devices are controlled by CPU . ’üČ Data can pass through bus in half duplex mode to and from CPU. ’üČ Memory is split to small cells with the same size. Their ordinal numbers are called address numbers. ’üČ Each time CPU fetches a program instruction it may have to perform one or more read/write operation ŌĆ£instructionŌĆØ from/to data memory space. It must wait until these subsequent ŌĆ£instructionŌĆ£ are complete before it can fetch

- 22. CPU Architectures Princeton Architecture (Von Neumann Architecture) :

- 23. CPU Architectures Princeton Architecture (Von Neumann Architecture) :

- 24. CPU Architectures Princeton Architecture (Von Neumann Architecture) :

- 25. CPU Architectures 2) Harvard Architecture: The Harvard Mark II was finished at Harvard University in 1947 . It wasnŌĆÖt so modern as the computer from von Neumann team. But it introduced a slightly different architecture. Memory for data was separated from the memory for instruction. This concept is known as the HarvardArchitecture : ’üČ There is no need to make the two memories share characteristics. In particular, the word width, timing, implementation technology, and memory address structure can differ. ’üČ The CPU can read an instruction and perform a data memory access at the same time.. ’üČ This speeds up execution time but increases the cost of more hardware complexity. ’üČ If, for instance, every instruction run in the CPU requires an access to memory, the computer gains nothing for increased CPU speedŌĆöa problem referred to as being "memory bound".

- 27. Harvard Von Neumann Used in DSPs and other processors found in latest embedded systems and Mobile communication systems, audio, speech, image processing systems Used in conventional processo rs found in PCs and Servers, and embedded systems with only control functions. Control unit for two buses is more complicated and more expensive One bus is simpler for the control unit design The code is executed in parallel The code is executed serially and takes more clock cycles Avg computation speed is high Avg computation speed is low

- 28. CPU Architectures Which is the best ? For Processors : Von Neumann is used in Processors because, unlike MCUs, processors donŌĆÖt have internal memory or peripherals and the connection to memory is through external bus and Von Neumann is suitable because: ’üČ Cost: less buses means less cost. ’üČ Space: we donŌĆÖt need to waste large space of motherboard. ’üČ Processors mainly deal with only one memory, RAM which holds the data and instructions, so only one bus will be suitable and the slow access will be substituted by the high speed of the processor and using the cash memory. For Microcontroller : Harvard architecture is used in MCU because: ’üČ Microcontroller contains everything on the chip. RAM, flash, and peripherals and due to the small size using multiple buses is not an issue. ’üČ Microcontroller speed is not high so multiple buses will help with the limited speed of MCU.

- 29. CPU Structure The basic elements of the CPU are: ŌĆó ALU ’üČ Arithmetic & Logic Unit ’üČ Responsible for performing logic and arithmetic calculations. ŌĆó Floating-Point Unit (FPU) ’üČ performs arithmetic operations on floating point numbers. ŌĆó Registers ’üČ Registers are used to store data beside the ALU ’üČ Registers are used to transfer data to/from memory ’üČ Registers carry the inputs of ALU, as well as, receiving the output of the ALU. ŌĆó Internal CPU Bus ’üČ It is a special bus. ’üČ It is responsible for transferring data between registers, ALU, and system memory ŌĆó Control Unit ’üČ It is responsible for organizing the actions of the CPU ’üČ It can be thought of as the heart of the CPU

- 30. CPU Structure Arithmetic logic unit : ŌĆó ALU is a digital circuit that performs : ’üČ Arithmetic operations : o Add, Sub,ŌĆ”.etc. ’üČ Logical operations : o And, Or, Not,ŌĆ” etc. ŌĆó Operates and stores results in general registers ŌĆó Stores operation status in flag/status registers ’üČ Carry occurrence, overflow occurrence

- 31. CPU Structure FPU ( Floating-Point Unit): ŌĆó The FPU performs arithmetic operations on floating point numbers. ŌĆó An FPU is complicated to design, although the IEEE 754 standard helps to answer some of the specific questions about implementation ŌĆó 8086 : First computer to implement IEEE FP ŌĆó Three types of the Floating-Point Data : ’üČ The half-precision floating-point format (16-bit data) ’üČ The single-precision floating-point format (32-bit data) ’üČ The double-precision floating-point format (64-bit data)

- 32. CPU Structure IEEE Floating Point Standard 754 (FPS) 1. Half precision : ’üČ 16-bits ŌĆō 10-bit mantissa ŌĆō 5-bit exponent ŌĆō 1-bit sign 2. Single precision : ’üČ 32-bits ŌĆō 23-bit mantissa ŌĆō 8-bit exponent ŌĆō 1-bit sign 3. Double precision : ’üČ 64-bits ŌĆō 52-bit mantissa ŌĆō 11-bit exponent ŌĆō 1-bit sign 31 30 23 22 0 S Exponent Mantissa (bits 0-22) 63 62 52 51 0 S Exponent Mantissa (bits 0-51) 15 14 10 9 0 S Exponent Mantissa (bits 0-22)

- 33. Pipeline : ŌĆó Continuous and parallel streaming of instruction to the CPU. ŌĆó A method of achieving higher execution speed at same clock speed.

- 34. Pipeline :

- 35. Pipeline :

- 36. Instruction set architecture (ISA) ’ü« The computer ISA defines all of the programmer-visible components and operations of the computer ’ü« memory organization ’ü« address space -- how may locations can be addressed? ’ü« addressability -- how many bits per location? ’ü« register set ’ü« how many? what size? how are they used? ’ü« instruction set ’ü« opcodes ’ü« data types ’ü« addressing modes ’ü« ISA provides all information needed for someone that wants to write a program in machine language (or translate from a high-level language to machine language).

- 37. CISC & RISC CISC RISC Complex Instruction Set Computer Reduced Instruction set Computer More no of instructions Less no of instructions Programming is easy Programming is difficult 8085,8086,Pentium PIC,AVR, ARM Any instructions may refer memory Only LOAD/STORE refer memory Not pipelined or less pipelined Highly pipelined Small code sizes large code sizes Instructions generally take more than 1 clock to execute. Instructions execute in one clock cycle. Complex in Design Simple in Design

- 38. Memory Unit: ŌĆó Memory is a part of the Any Computer System used for data storage. ŌĆó Types of Memory : ’üČ Volatile Memory . ’üČ Non Volatile Memory .

- 39. Memory Unit: Volatile memory : RAM memory (Random Access Memory) : ŌĆó Refers to the ability to access any memory cell directly. RAM is much faster than ROM . It used to write and read data values while program running . ŌĆó Volatile : if you remove the power supply its contents are lost. ŌĆó Any variable used in a program is allocated into RAM. ŌĆó local variables, pointers, functions, recursive functions results in using large amounts of RAM ŌĆó Types Of RAM : ’üČ Dynamic RAM (DRAM) ’üČ Static RAM (SRAM)

- 40. Memory Unit: Static RAM Dynamic RAM

- 41. Static RAM (SRAM) Dynamic RAM (DRAM) Made From flip-flops. Made From capacitors High cost (per bit) Low cost (per bit) High using power Low using power Fast Slow Used in cache Memory Used in main memory Large In size Low in Size Will retain state forever Automatically discharges after sometime, need refreshing

- 42. Memory Unit:

- 43. Memory Unit:

- 44. Memory Unit: Cache Memory Small amount of memory that is faster than RAM ’üČSlower than registers ’üČBuilt using SRAM ’üČRange from few KB to few MB Use by CPU to store frequently used instructions & data ’üČSpatial & temporal locality Use multiple levels of cache ’üČL1 Cache ŌĆō Very fast, usually within CPU itself ’üČL2 Cache ŌĆō Slower than L1, but faster than RAM ’üČToday thereŌĆÖs even L3 Cache

- 45. Memory Unit: L1 & L2 Cache

- 47. Memory Unit: Caching in Multi-Core Systems

- 48. Memory Unit: Caching in Multi-Core Systems (Cont.)

- 49. Memory Unit: Core i7 Die & Major Components

- 50. Memory Unit: Non-Volatile memory : ŌĆó ROM(Read Only Memory): ’āś Permanent memory(Non-Volatile memory). ’āś Used as Program Memory in Micro-Controller. ’āś ROM generally slower than RAM. ’āś The size of program that can be written depends on ’āś Written upon programming the microcontroller. ’āś Can't be written/modified at run time. ŌĆó ROM Types: ’āś Masked ROM . ’āś OTP ROM . ’āś UV EPROM . ’āś EEPROM . ’āś Flash EEPROM .

- 51. Memory Unit: 1-Masked ROM (MPROM) : -Programmed by the manufacturer. -The term ŌĆśmaskedŌĆÖcomes from the manufacturing process. -In case of a large-scale production, the price is very low.

- 52. Memory Unit: 2-OTP (One Time Programmable): - Also called programmable ROM(PROM). - Enables programmer to download a program into it one time only. - Used when the firmware is stable and the product is shipping in bulk to customers. - If an error is detected after downloading, the only thing you can do is to download the correct program to another chip.

- 53. Memory Unit: 3- UV EPROM (UV Erasable Programmable ROM) - It enables data to be erased under strong ultraviolet light - After a few minutes it is possible to download a new pro gram - the package of this microcontroller has recognizableŌĆ£ŌĆØwi ndowŌĆØŌĆØon the upper side. It enables surface of the silicon chip to be lit by an UV lamp, which has as a result that complete program cleared and a new program download enabled

- 54. Memory Unit: 4-EEPROM(Electrically Erasable Programmable ROM) - Can be erased by exposing it to an electrical charge. - The contents of this memory may be changed during run time (similar to RAM),but remains permanently saved even if the power supply is off (similar to ROM) - EEPROM is often used to read and store values , created during operation, which must be permanently saved. - Acts as peripheral of microcontroller. - Take more time in read/write access than RAM - The max number to Write/Erase Cycles is usually100,000 but in Read is infinity

- 55. Memory Unit: 5-Flash EEPROM - Invented in the 80s in the laboratories of Intel. - Represented as the successor to the EEPROM. - Flash is normally organized as sectors (256B - 16KB). - Large blocks of memory erased at once, rather than one word at a time like EEPROM , So FLASH is much faster th an EEPROM . Take more time in read/write access than RAM - The max number to Write/Erase Cycles is usually10,000 but in Read is infinity

- 56. Memory Unit: Type Volatile ? Writeable ? Erase size Max Erase cycles Cost per bit speed SRAM Yes Yes Byte unlimited Expensive Fast DRAM Yes Yes Byte unlimited Moderate Moderate Masked ROM No NO -- -- Inexpensi ve Fast PROM No Once -- -- Moderate Fast EPROM No Yes Entire chip Limited(consult datasheet( Moderate Fast EEPROM No Yes byte Limited(consult datasheet( Expensive Fast to read slow to write FLASH No Yes sector Limited(consult datasheet) Moderate Fast to read slow to write

- 58. Microcontrollers Selection Criteria: AVR(Atmel) 8051(Intel) PIC(Microchip) HC11(Motorola) Architecture Harvard Von-Neumann Harvard Von Neumann Instruction Type RISC CISC RISC CISC Max speed 20MHz 24MHz 20MHz 8MHz Cycle/Instruction 1 12 4 8 Instruction/second 20MIPS 2MIPS 5MIPS 1MIPS N of Instructions 132 215 32 200 Max program size 256KB 32KB 64KB 32KB Data bus Width 16-bit 8-bit 14-bit 8-bit