KTMT-Chuong 7 -CĂĄc phÆ°ÆĄng phĂĄp vĂ o ra.pptx

- 1. Há»C VIá»N CĂNG NGHá» BÆŻU CHĂNH VIá»N THĂNG BĂI GIáșąNG MĂN KIáșŸN TRĂC MĂY TĂNH GiáșŁng viĂȘn: PháșĄm VÄn CÆ°á»ng Äiá»n thoáșĄi/E-mail: cuongpham.ptit@gmail.com WWW: https://sites.google.com/view/cuongpham/home CHÆŻÆ NG 7 â CĂC PHÆŻÆ NG PHĂP VĂO RA Dở LIá»U

- 2. Ná»I DUNG 1. Giá»i thiá»u cĂĄc phÆ°ÆĄng phĂĄp vĂ o ra dữ liá»u 2. VĂ o ra báș±ng thÄm dĂČ 3. NgáșŻt vĂ xá» lĂœ ngáșŻt ï¶ NgáșŻt vĂ phĂąn loáșĄi ngáșŻt ï¶ Chu trĂŹnh xá» lĂœ ngáșŻt 4. VĂ o ra báș±ng ngáșŻt ï¶ VĂ o ra báș±ng ngáșŻt ï¶ Giá»i thiá»u máșĄch Äiá»u khiá»n ngáșŻt 8259 5. VĂ o ra báș±ng DMA ï¶ VĂ o ra báș±ng DMA ï¶ Giá»i thiá»u máșĄch Äiá»u khiá»n DMA 8237

- 3. 7.1. Giá»i thiá»u cĂĄc phÆ°ÆĄng phĂĄp vĂ o ra dữ liá»u ï¶ Vai trĂČ của vĂ o ra dữ liá»u: ï§ LĂ phÆ°ÆĄng tiá»n giĂșp CPU giao tiáșżp vá»i tháșż giá»i bĂȘn ngoĂ i ï§ Cung cáș„p dữ liá»u Äáș§u vĂ o cho CPU xá» lĂœ ï§ Cung cáș„p phÆ°ÆĄng tiá»n Äá» CPU káșżt xuáș„t dữ liá»u Äáș§u ra ï¶ CĂĄc phÆ°ÆĄng phĂĄp vĂ o ra chĂnh: ï§ ThÄm dĂČ (polling) ï§ NgáșŻt (Interrupt) ï§ Truy nháșp trá»±c tiáșżp bá» nhá» (DMA-Direct Memory Access)

- 4. 7.1. Giá»i thiá»u cĂĄc phÆ°ÆĄng phĂĄp vĂ o ra dữ liá»u ï¶ CĂĄc cá»ng vĂ o ra của mĂĄy tĂnh ï§ PS/2: cá»ng ghĂ©p ná»i vá»i bĂ n phĂm vĂ chuá»t ï§ COM: cĂĄc cá»ng ghĂ©p ná»i ná»i tiáșżp ï§ LPT: cĂĄc cá»ng ghĂ©p ná»i song song ï§ IDE, SATA, SCSI: cĂĄc cá»ng ghĂ©p ná»i á» ÄÄ©a ï§ LAN: cá»ng ghĂ©p ná»i máșĄng cỄc bá» ï§ Audio: cá»ng ghĂ©p ná»i Ăąm thanh (speaker, mic vĂ line-in) ï§ Video: Cá»ng ghĂ©p ná»i vá»i mĂ n hĂŹnh (tÆ°ÆĄng tá»±) ï§ DVI : Cá»ng ghĂ©p ná»i vá»i mĂ n hĂŹnh (sá») ï§ USB: Cá»ng ghĂ©p ná»i theo chuáș©n USB âą USB 1.0: 12Mb/s âą USB 2.0: 480Mb/s âą USB 3.0: 1.5Gb/s (tÆ°ÆĄng lai)

- 5. 7.2. VĂ o ra báș±ng thÄm dĂČ ï¶ CÆĄ cháșż vĂ o ra báș±ng thÄm dĂČ: ï§ CPU quáșŁn lĂœ danh sĂĄch cĂĄc thiáșżt bá» vĂ o ra kĂšm theo Äá»a chá» cĂĄc cá»ng giao tiáșżp; ï§ CĂĄc thiáșżt bá» vĂ o ra Äá»nh kỳ cáșp nháșt tráșĄng thĂĄi sáș”n sĂ ng lĂ m viá»c của mĂŹnh lĂȘn cĂĄc bĂt cá» tráșĄng thĂĄi vĂ o ra của mĂŹnh; ï§ CPU Äá»nh kỳ láș§n lÆ°á»Łt âquĂ©tâ cĂĄc thiáșżt bá» vĂ o ra Äá» âÄá»câ cĂĄc bit cá» tráșĄng thĂĄi vĂ o ra; âą Náșżu gáș·p má»t thiáșżt bá» sáș”n sĂ ng lĂ m viá»c, 2 bĂȘn tiáșżn hĂ nh trao Äá»i dữ liá»u; âą Trao Äá»i dữ liá»u xong, CPU tiáșżp tỄc quĂ©t thiáșżt bá» khĂĄc. ï§ CPU lĂ bĂȘn chủ Äá»ng trong quĂĄ trĂŹnh trao Äá»i dữ liá»u

- 6. 7.2. VĂ o ra báș±ng thÄm dĂČ ï¶ ÆŻu Äiá»m: ï§ ÄÆĄn giáșŁn, dá» cĂ i Äáș·t ï§ CĂł thá» ÄÆ°á»Łc cĂ i Äáș·t báș±ng pháș§n má»m ï¶ NhÆ°á»Łc Äiá»m: ï§ Hiá»u quáșŁ tháș„p do CPU tá»n nhiá»u thá»i gian Äá» thÄm dĂČ cĂĄc thiáșżt bá» ï§ KhĂŽng thá»±c sá»± kháșŁ thi khi cĂł nhiá»u thiáșżt bá» trong danh sĂĄch thÄm dĂČ ï¶ á»šng dỄng của vĂ o ra báș±ng thÄm dĂČ: ï§ ThÄm dĂČ thÆ°á»ng ÄÆ°á»Łc sá» dỄng khi há» thá»ng khá»i Äá»ng: CPU thÄm dĂČ háș§u háșżt cĂĄc thiáșżt bá» Äá» xĂĄc láșp cáș„u hĂŹnh ï§ ThÄm dĂČ ÄÆ°á»Łc sá» dỄng trong quĂĄ trĂŹnh hoáșĄt Äá»ng vá»i cĂĄc thiáșżt bá» rá»i (removable) nhÆ° á» ÄÄ©a CD/DVD, á» má»m, ...

- 7. 7.2. VĂ o ra báș±ng thÄm dĂČ â khĂŽng Æ°u tiĂȘn ï¶ Ba thiáșżt bá» A, B, C ÄÆ°á»Łc thÄm dĂČ khĂŽng Æ°u tiĂȘn ï¶ CPU quĂ©t táș„t cáșŁ cĂĄc thiáșżt bá» trong má»t chu trĂŹnh thÄm dĂČ ï¶ CPU cĂł thá» trao Äá»i dữ liá»u vá»i nhiá»u hÆĄn 1 thiáșżt bá» trong má»t chu trĂŹnh thÄm dĂČ ï¶ CĂĄc thiáșżt bá» ÄÆ°á»Łc âthÄmâ láș§n lÆ°á»Łt, khĂŽng phỄ thuá»c vĂ o thiáșżt bá» Äứng trÆ°á»c chu trĂŹnh. ï¶ CPU báșŻt Äáș§u 1 chu trĂŹnh thÄm dĂČ má»i sau khi ÄĂŁ quĂ©t qua táș„t cáșŁ cĂĄc thiáșżt bá». Start A Ready? Exchange data with A Yes No B Ready? Exchange data with B Yes No C Ready? Exchange data with C Yes No

- 8. 7.2. VĂ o ra báș±ng thÄm dĂČ â cĂł Æ°u tiĂȘn ï¶ Ba thiáșżt bá» A, B, C ÄÆ°á»Łc thÄm dĂČ cĂł Æ°u tiĂȘn theo thứ tá»±: A, B, C; ï¶ CPU cĂł thá» quĂ©t táș„t cáșŁ cĂĄc thiáșżt bá» trong má»t chu trĂŹnh thÄm dĂČ ï¶ CPU chá» trao Äá»i dữ liá»u vá»i tá»i Äa 1 thiáșżt bá» trong má»t chu trĂŹnh thÄm dĂČ ï¶ CĂĄc thiáșżt bá» cĂł mức Æ°u tiĂȘn cao luĂŽn ÄÆ°á»Łc thÄm trÆ°á»c; ï¶ CĂĄc thiáșżt bá» cĂł mức Æ°u tiĂȘn tháș„p chá» ÄÆ°á»Łc thÄm náșżu cĂĄc thiáșżt bá» Äứng trÆ°á»c nĂł khĂŽng sáș”n sĂ ng. ï¶ CPU báșŻt Äáș§u 1 chu trĂŹnh thÄm dĂČ má»i ngay sau khi trao Äá»i dữ liá»u vá»i má»t thiáșżt bá». Start A Ready? Exchange data with A Yes No B Ready? Exchange data with B Yes No C Ready? Exchange data with C Yes No

- 9. 7.3 NgáșŻt vĂ xá» lĂœ ngáșŻt ï¶ NgáșŻt lĂ gĂŹ? ï§ NgáșŻt (Interrupt) lĂ má»t sá»± kiá»n mĂ CPU táșĄm dừng thá»±c hiá»n má»t chÆ°ÆĄng trĂŹnh Äá» thá»±c hiá»n má»t ÄoáșĄn chÆ°ÆĄng trĂŹnh khĂĄc theo yĂȘu cáș§u từ bĂȘn ngoĂ i; ï§ ThĂŽng thÆ°á»ng cĂĄc yĂȘu cáș§u từ bĂȘn ngoĂ i thÆ°á»ng xuáș„t phĂĄt từ cĂĄc thiáșżt bá» vĂ o ra. CĂĄc yĂȘu cáș§u nĂ y gá»i lĂ cĂĄc yĂȘu cáș§u ngáșŻt; ï§ ÄoáșĄn chÆ°ÆĄng trĂŹnh CPU thá»±c hiá»n trong thá»i gian ngáșŻt ÄÆ°á»Łc gá»i lĂ chÆ°ÆĄng trĂŹnh con phỄc vỄ ngáșŻt (CTCPVN). ï¶ CĂĄc CTCPVN lĂ cĂĄc ÄoáșĄn chÆ°ÆĄng trĂŹnh: ï§ ÄÆ°á»Łc viáșżt sáș”n vĂ lÆ°u trong ROM; ï§ Má»i CTCPVN cĂł nhiá»m vỄ riĂȘng vĂ thÆ°á»ng lĂ ÄáșŁm nhiá»m viá»c trao Äá»i dữ liá»u vá»i thiáșżt bá» vĂ o ra. ï¶ Khi nĂ o CPU kiá»m tra vĂ xá» lĂœ ngáșŻt: CPU kiá»m tra yĂȘu cáș§u ngáșŻt táșĄi chu kỳ Äá»ng há» cuá»i cĂčng của chu kỳ lá»nh.

- 10. 7.3 NgáșŻt vĂ xá» lĂœ ngáșŻt ï¶ PhĂąn loáșĄi ngáșŻt ï§ NgáșŻt cứng: lĂ cĂĄc ngáșŻt ÄÆ°á»Łc kĂch hoáșĄt bá»i cĂĄc bá» pháșn pháș§n cứng gá»i Äáșżn chĂąn NMI vĂ INTR của CPU; gá»m: âą NgáșŻt khĂŽng che ÄÆ°á»Łc NMI (Non-Maskable Interrupt): ngáșŻt gá»i Äáșżn chĂąn NMI của CPU, khĂŽng chá»u sá»± áșŁnh hÆ°á»ng của cá» ngáșŻt; VD: ngáșŻt Reset; âą NgáșŻt che ÄÆ°á»Łc INTR (Maskable Interrupt): ngáșŻt gá»i Äáșżn chĂąn INTR của CPU, chá»u sá»± chi phá»i của cá» ngáșŻt; Cá» IF=1 ï cho phĂ©p ngáșŻt, IF=0 ï cáș„m ngáșŻt. ï§ NgáșŻt má»m: lĂ cĂĄc ngáșŻt ÄÆ°á»Łc kĂch hoáșĄt bá»i cĂĄc chÆ°ÆĄng trĂŹnh thĂŽng qua lá»nh gá»i ngáșŻt INT <N>. N lĂ sá» hiá»u ngáșŻt, N=0-255. ï§ CĂĄc ngáșŻt ngoáșĄi lá»: lĂ cĂĄc ngáșŻt do cĂĄc lá»i náșŁy sinh trong quĂĄ trĂŹnh hoáșĄt Äá»ng của CPU: âą NgáșŻt chia cho 0 (divide by zero) âą NgáșŻt do trĂ n (overflow)

- 11. 7.3 NgáșŻt vĂ xá» lĂœ ngáșŻt ï¶ Tráșt tá»± Æ°u tiĂȘn trong xá» lĂœ cĂĄc yĂȘu cáș§u ngáșŻt ï§ CĂĄc yĂȘu cáș§u ngáșŻt ÄÆ°á»Łc gĂĄn má»t mức Æ°u tiĂȘn ï§ Khi nháșn ÄÆ°á»Łc nhiá»u yĂȘu cáș§u ngáșŻt Äá»ng thá»i, CPU sáșœ xá» lĂœ chĂșng theo mức Æ°u tiĂȘn Äá»nh trÆ°á»c ï¶ Mức Æ°u tiĂȘn cĂĄc yĂȘu cáș§u ngáșŻt (từ cao nháș„t Äáșżn tháș„p nháș„t) 1. NgáșŻt ná»i bá»: INT 0 (chia cho 0), INT N (N<>0) 2. NgáșŻt khĂŽng che ÄÆ°á»Łc NMI 3. NgáșŻt che ÄÆ°á»Łc INTR 4. NgáșŻt cháșĄy từng lá»nh: INT 1

- 12. 7.3 NgáșŻt vĂ xá» lĂœ ngáșŻt â BáșŁng vector ngáșŻt ï¶ Vi xá» lĂœ 8086/8088 cĂł 256 ngáșŻt ÄÆ°á»Łc ÄĂĄnh sá» từ 0-255 ï¶ Má»t vector ngáșŻt gá»m cĂĄc thĂŽng tin: ï§ Sá» hiá»u ngáșŻt N, N=0-255 hoáș·c 00-FFH ï§ Äá»a chá» Äáș§y Äủ chÆ°ÆĄng trĂŹnh con phỄc vỄ ngáșŻt (CTCPVN) lÆ°u trong bá» nhá» ROM. Äá»a chá» Äáș§y Äủ gá»m: âą Äá»a chá» ÄoáșĄn (CS) âą Äá»a chá» lá»ch (IP) ï¶ BáșŁng vector ngáșŻt lÆ°u thĂŽng tin vá» 256 vector ngáșŻt. Má»i báșŁn ghi của báșŁng gá»m cĂĄc thĂŽng tin: ï§ Sá» hiá»u ngáșŻt ï§ Äá»a chá» ÄoáșĄn vĂ Äá»a chá» lá»ch của CTCPVN.

- 13. 7.3 NgáșŻt vĂ xá» lĂœ ngáșŻt â BáșŁng vector ngáșŻt CS IP CS IP 00 01 FF BáșŁng vector ngáșŻt ROM BáșŻt Äáș§u ÄoáșĄn BáșŻt Äáș§u CTCPVN

- 14. 7.3 NgáșŻt vĂ xá» lĂœ ngáșŻt â Chu trĂŹnh xá» lĂœ ngáșŻt CTC ThĂąn CTC YĂȘu cáș§u ngáșŻt CPU tá»±: âą LÆ°u t.ghi cá» FR âą XoĂĄ IF vĂ TF âą LÆ°u CS vĂ IP âą Láș„y Ä/c CTCPVN CTCPVN ThĂąn CTCPVN IRET CPU tá»±: âą KhĂŽi phỄc CS vĂ IP âą KhĂŽi phỄc FR âą Äáș·t cá» IF vĂ TF CĂĄc lá»nh lÆ°u giĂĄ trá» cĂĄc thanh ghi dĂčng chung CĂĄc lá»nh khĂŽi phỄc giĂĄ trá» cĂĄc thanh ghi dĂčng chung TáșĄm dừng CTC Tiáșżp tỄc CTC

- 15. 7.3 NgáșŻt vĂ xá» lĂœ ngáșŻt â Chu trĂŹnh xá» lĂœ ngáșŻt 1. Khi nháșn ÄÆ°á»Łc yĂȘu cáș§u ngáșŻt, CPU thá»±c hiá»n cĂĄc viá»c: a. HoĂ n táș„t lá»nh Äang thá»±c hiá»n của chÆ°ÆĄng trĂŹnh chĂnh (CTC) b. LÆ°u giĂĄ trá» của thanh ghi cá» FR vĂ o ngÄn xáșżp c. XoĂĄ cá» ngáșŻt IF vĂ cá» báș«y TF d. LÆ°u giĂĄ trá» của cĂĄc t.ghi CS vĂ IP vĂ o ngÄn xáșżp e. Từ sá» hiá»u ngáșŻt N, láș„y Äá»a chá» của CTCPVN từ báșŁng vector ngáșŻt 2. NáșĄp Äá»a chá» của CTCPVN vĂ o CS vĂ IP, CPU thá»±c hiá»n CPCPVN, gá»m: a. LÆ°u giĂĄ trá» cĂĄc thanh ghi dĂčng chung vĂ o ngÄn xáșżp b. Thá»±c hiá»n mĂŁ chĂnh của CTCPVN c. KhĂŽi phỄc giĂĄ trá» cĂĄc thanh ghi dĂčng chung 3. Gáș·p lá»nh IRET káșżt thĂșc CTCPVN, CPU thá»±c hiá»n cĂĄc viá»c: a. KhĂŽi phỄc giĂĄ trá» của CS vĂ IP b. KhĂŽi phỄc giĂĄ trá» của thanh ghi cá» FR c. Äáș·t cá» ngáșŻt IF vĂ cá» báș«y TF 4. CPU tiáșżp tỄc thá»±c hiá»n lá»nh tiáșżp theo của CTC (náș±m sau lá»nh xáșŁy ra ngáșŻt).

- 16. 7.3 VĂ o ra báș±ng ngáșŻt â Chu trĂŹnh vĂ o ra báș±ng ngáșŻt 1. Thiáșżt bá» vĂ o ra cĂł nhu cáș§u trao Äá»i dữ liá»u, gá»i yĂȘu cáș§u ngáșŻt Äáșżn chĂąn tĂn hiá»u INTR của CPU; 2. Khi nháșn ÄÆ°á»Łc yĂȘu cáș§u ngáșŻt, CPU thá»±c hiá»n cĂĄc viá»c: a. HoĂ n táș„t lá»nh Äang thá»±c hiá»n của chÆ°ÆĄng trĂŹnh chĂnh (CTC) b. LÆ°u giĂĄ trá» của thanh ghi cá» FR vĂ o ngÄn xáșżp c. XoĂĄ cá» ngáșŻt IF vĂ cá» báș«y TF d. LÆ°u giĂĄ trá» của cĂĄc t.ghi CS vĂ IP vĂ o ngÄn xáșżp e. Gá»i tĂn hiá»u xĂĄc nháșn ngáșŻt Äáșżn thiáșżt bá» vĂ o ra qua chĂąn tĂn hiá»u INTA 3. Nháșn ÄÆ°á»Łc hiá»u xĂĄc nháșn ngáșŻt của CPU, thiáșżt bá» vĂ o ra gá»i sá» hiá»u ngáșŻt N Äáșżn CPU 4. Nháșn ÄÆ°á»Łc sá» hiá»u ngáșŻt N, CPU láș„y Äá»a chá» của CTCPVN tÆ°ÆĄng ứng từ báșŁng vector ngáșŻt

- 17. 7.3 VĂ o ra báș±ng ngáșŻt â Chu trĂŹnh vĂ o ra báș±ng ngáșŻt 5. NáșĄp Äá»a chá» của CTCPVN vĂ o CS vĂ IP, CPU thá»±c hiá»n CPCPVN, gá»m: a. LÆ°u giĂĄ trá» cĂĄc thanh ghi dĂčng chung vĂ o ngÄn xáșżp b. Thá»±c hiá»n mĂŁ chĂnh của CTCPVN: Äá»ng thá»i thá»±c hiá»n viá»c trao Äá»i dữ liá»u vá»i thiáșżt bá» vĂ o ra c. KhĂŽi phỄc giĂĄ trá» cĂĄc thanh ghi dĂčng chung 6. Gáș·p lá»nh IRET káșżt thĂșc CTCPVN, CPU thá»±c hiá»n cĂĄc viá»c: a. KhĂŽi phỄc giĂĄ trá» của CS vĂ IP b. KhĂŽi phỄc giĂĄ trá» của thanh ghi cá» FR c. Äáș·t cá» ngáșŻt IF vĂ cá» báș«y TF 7. CPU tiáșżp tỄc thá»±c hiá»n lá»nh tiáșżp theo của CTC (náș±m ngay sau lá»nh xáșŁy ra ngáșŻt).

- 18. 7.3 VĂ o ra báș±ng ngáșŻt â ÆŻu vĂ nhÆ°á»Łc Äiá»m ï¶ ÆŻu Äiá»m ï§ Hiá»u quáșŁ hÆĄn vĂ o ra báș±ng thÄm dĂČ, do CPU khĂŽng pháșŁi thÄm dĂČ từng thiáșżt bá» ï¶ NhÆ°á»Łc Äiá»m ï§ Phức táșĄp hÆĄn vĂ o ra báș±ng thÄm dĂČ ï§ Cáș§n máșĄch pháș§n cứng Äá» Äiá»u khiá»n ngáșŻt ï¶ BĂȘn chủ Äá»ng trong vĂ o ra báș±ng ngáșŻt: ï§ Thiáșżt bá» vĂ o ra

- 19. 7.3 MáșĄch Äiá»u khiá»n ngáșŻt 8259A ï¶ TrÆ°á»ng hợp cĂł nhiá»u yĂȘu cáș§u ngáșŻt che ÄÆ°á»Łc (ngáșŻt gá»i Äáșżn chĂąn INTR), máșĄch Äiá»u khiá»n ngáșŻt 8259A thÆ°á»ng ÄÆ°á»Łc sá» dỄng Äá» giáșŁi quyáșżt váș„n Äá» Æ°u tiĂȘn xá» lĂœ cĂĄc yĂȘu cáș§u ngáșŻt. ï¶ Vi máșĄch 8259A ÄÆ°á»Łc gá»i lĂ máșĄch Äiá»u khiá»n ngáșŻt láșp trĂŹnh ÄÆ°á»Łc (Programmable Interrupt Controller - PIC). ï§ LĂ má»t vi máșĄch cụ lá»n cĂł thá» xá» lĂœ trÆ°á»c ÄÆ°á»Łc 8 yĂȘu cáș§u ngáșŻt vá»i cĂĄc mức Æ°u tiĂȘn khĂĄc nhau Äá» táșĄo ra má»t yĂȘu cáș§u ngáșŻt ÄÆ°a Äáșżn Äáș§u vĂ o INTR của CPU 8086. ï§ Náșżu ná»i táș§ng 1 máșĄch 8259A chủ vá»i 8 máșĄch 8259A thợ ta cĂł thá» nĂąng tá»ng sá» cĂĄc yĂȘu cáș§u ngáșŻt vá»i cĂĄc mức Æ°u tiĂȘn khĂĄc nhau lĂȘn thĂ nh 64.

- 20. 7.3 PIC 8259A â SÆĄ Äá» chĂąn vĂ cĂĄc tĂn hiá»u D0-D7 Dữ liá»u RD, WR Äá»c, Ghi (mức tháș„p) A0 Äá»a chá» thanh ghi CS Chá»n chip CAS0-2 GhĂ©p táș§ng vá»i PIC khĂĄc SP XĂĄc Äá»nh PIC chủ (master SP=1) thợ (slave SP=0) EN Má» Äá»m dữ liá»u INT YĂȘu cáș§u ngáșŻt ghĂ©p vá»i INTR của CPU INTA XĂĄc nháșn ngáșŻt ghĂ©p vá»i INTA của CPU D0-D7 TĂn hiá»u dữ liá»u ghĂ©p vá»i bus dữ liá»u của CPU

- 21. 7.3 PIC 8259A â SÆĄ Äá» khá»i

- 22. 7.3 PIC 8259A â SÆĄ Äá» khá»i ï¶ Thanh ghi Interrupt Request Register (IRR): ghi nhá» cĂĄc yĂȘu cáș§u ngáșŻt cĂł táșĄi Äáș§u vĂ o IRi. ï¶ Khá»i Priority resolver: xĂĄc Äá»nh thứ tá»± Æ°u tiĂȘn của cĂĄc yĂȘu cáș§u ngáșŻt. ï¶ Thanh ghi Interrupt Service Register (ISR): ghi nhá» cĂĄc yĂȘu cáș§u ngáșŻt Äang ÄÆ°á»Łc phỄc vỄ trong sá» cĂĄc yĂȘu cáș§u ngáșŻt IRi. ï¶ Thanh ghi Interrupt Mask Register (IMR): ghi nhá» máș·t náșĄ ngáșŻt Äá»i vá»i cĂĄc yĂȘu cáș§u ngáșŻt IRi.

- 23. 7.3 PIC 8259A â SÆĄ Äá» khá»i ï¶ Logic Äiá»u khiá»n (Control Logic): khá»i nĂ y cĂł nhiá»m vỄ gá»i yĂȘu cáș§u ngáșŻt tá»i INTR của 8086 khi cĂł tĂn hiá»u táșĄi cĂĄc chĂąn IRi vĂ nháșn tráșŁ lá»i cháș„p nháșn yĂȘu cáș§u ngáșŻt INTA từ CPU Äá» rá»i Äiá»u khiá»n viá»c ÄÆ°a ra kiá»u ngáșŻt trĂȘn buĂœt dữ liá»u. ï¶ Äá»m buĂœt dữ liá»u (Data Bus Buffer): dĂčng Äá» phá»i ghĂ©p 8259A vá»i bus dữ liá»u của CPU. ï¶ Logic Äiá»u khiá»n ghi/Äá»c (Read/Write Logic): Äiá»u khiá»n viá»c ghi cĂĄc từ Äiá»u khiá»n vĂ Äá»c cĂĄc từ tráșĄng thĂĄi của 8259A. ï¶ Khá»i Äá»m ná»i táș§ng vĂ so sĂĄnh (Cascade buffer/ comparator): ghi nhá» vĂ so sĂĄnh sá» hiá»u của cĂĄc máșĄch 8259A cĂł máș·t trong há» vi xá» lĂœ.

- 24. 7.3 PIC 8259A â GhĂ©p ná»i vá»i CPU

- 25. 7.3 PIC 8259A â GhĂ©p ná»i nhiá»u táș§ng vá»i CPU

- 26. 7.3 Láșp trĂŹnh cho PIC 8259A ï¶ PIC ÄÆ°á»Łc láșp trĂŹnh thĂŽng qua viá»c náșĄp cĂĄc giĂĄ trá» thĂch hợp cho 7 thanh ghi của 8259A: ï§ 4 từ khá»i táșĄo ICW (Initialization Control Word) ï§ 3 từ Äiá»u khiá»n hoáșĄt Äá»ng OCW (Operation Control Word) ï¶ ICW xĂĄc láșp cháșż Äá» hoáșĄt Äá»ng cho PIC-8259A ï¶ OCW Äiá»u khiá»n 8259A hoáșĄt Äá»ng á» cĂĄc cháșż Äá» khĂĄc nhau

- 27. 7.3 L.trĂŹnh PIC 8259A â XĂĄc láșp cháșż Äá» lĂ m viá»c BĂt Äá»a chá» A0 = 0 ï ICW1 A0 = 1 ï ICW2, 3, 4

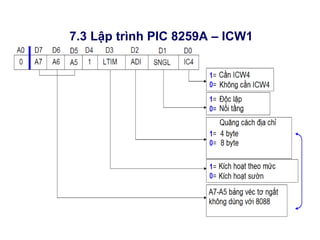

- 28. 7.3 Láșp trĂŹnh PIC 8259A â ICW1

- 29. 7.3 Láșp trĂŹnh PIC 8259A â ICW2 ï¶ XĂĄc Äá»nh sá» hiá»u ngáșŻt

- 30. 7.3 Láșp trĂŹnh PIC 8259A â ICW2 ï¶ ICW2 vá»i 8088/8086

- 31. 7.3 Láșp trĂŹnh PIC 8259A â ICW3

- 32. 7.3 Láșp trĂŹnh PIC 8259A â ICW4

- 33. 7.3 Láșp trĂŹnh PIC 8259A â VĂ dỄ ï¶ XĂĄc Äá»nh cĂĄc từ khá»i táșĄo cho 8259 ghĂ©p ná»i vá»i 8086 á» cháșż Äá» Äá»c láșp, trong há» cĂł Äá»m bus, cháșż Äá» Æ°u tiĂȘn cá» Äá»nh vĂ vá»i EOI thÆ°á»ng, IR kĂch hoáșĄt theo mức, tĂn hiá»u IR ÄÆ°á»Łc gĂĄn sá» hiá»u ngáșŻt 50H.

- 34. 7.3 Láșp trĂŹnh PIC 8259A â OCW1

- 35. 7.3 Láșp trĂŹnh PIC 8259A â OCW2

- 36. 7.3 PIC 8259 â TrĂŹnh tá»± xá» lĂœ cĂĄc sá»± kiá»n ï¶ CĂĄc tĂn hiá»u yĂȘu cáș§u ngáșŻt do thiáșżt bá» vĂ o/ra gá»i tá»i PIC lĂ m cho cĂĄc bĂt tÆ°ÆĄng ứng trong IRR ÄÆ°á»Łc báșt lĂȘn ï¶ PIC xem xĂ©t cĂĄc yĂȘu cáș§u ngáșŻt vĂ bĂĄo hiá»u cho CPU khi cáș§n (INTR) ï¶ CPU xĂĄc nháșn ngáșŻt báș±ng cĂĄch ÄÆ°a ra INTA ï¶ Khi nháșn ÄÆ°á»Łc INTA, PIC xĂła bĂt tÆ°ÆĄng ứng trong IRR vĂ bĂt Æ°u tiĂȘn cao nháș„t của ISR ÄÆ°á»Łc báșt ï¶ CPU ÄÆ°a ra INTA thứ 2, PIC ÄÆ°a ra 1 byte dữ liá»u vá» sá» hiá»u ngáșŻt ï¶ Káșżt thĂșc chu kỳ ngáșŻt. Náșżu dĂčng AEOI thĂŹ bit ISR bá» xĂła vĂ o cuá»i xung INTA thứ 2. Náșżu khĂŽng, bĂt ISR giữ nguyĂȘn cho Äáșżn khi cĂł cĂąu lá»nh EOI.

- 37. 7.4 VĂ o ra báș±ng DMA â Giá»i thiá»u ï¶ Trong cĂĄc phÆ°ÆĄng phĂĄp vĂ o ra báș±ng thÄm dĂČ vĂ ngáșŻt thiáșżt bá» vĂ o ra trao Äá»i dữ liá»u vá»i bá» nhá» thĂŽng qua CPU. ï¶ PhÆ°ÆĄng phĂĄp vĂ o ra báș±ng DMA (Direct Memory Access) cho phĂ©p thiáșżt bá» vĂ o ra trao Äá»i dữ liá»u trá»±c tiáșżp vá»i bá» nhá» theo khá»i, khĂŽng thĂŽng qua CPU; ï¶ DMA thĂch hợp khi cáș§n trao Äá»i dữ liá»u vá»i khá»i lÆ°á»Łng lá»n trong khoáșŁng thá»i gian ngáșŻn. CPU Memory I/O CPU Memory I/O DMAC VĂ o ra báș±ng ngáșŻt vĂ thÄm dĂČ VĂ o ra báș±ng DMA

- 38. 7.4 VĂ o ra báș±ng DMA â Giá»i thiá»u ï¶ DMAC (DMA Controller) thay máș·t CPU Äiá»u khiá»n quĂĄ trĂŹnh trao Äá»i dữ liá»u trá»±c tiáșżp giữa thiáșżt bá» vĂ o ra vĂ bá» nhá»; ï¶ DMA cĂł tá»c Äá» cao hÆĄn nhiá»u láș§n so vá»i vĂ o ra báș±ng thÄm dĂČ vĂ ngáșŻt. VĂ dỄ, vá»i VXL 8088: ï§ VĂ o ra báș±ng DMA máș„t 4 chu kỳ Äá»ng há» Äá» chuyá»n 1 byte thiáșżt bá» ngoáșĄi vi vĂ o bá» nhá»; ï§ VĂ o ra thĂŽng qua CPU máș„t 39 chu kỳ Äá»ng há» Äá» chuyá»n 1 byte thiáșżt bá» ngoáșĄi vi vĂ o bá» nhá»: ;Sá» chu kỳ Äá»ng há» LAP: MOV AL, [SI]; 10 OUT PORT, AL; 10 INC SI; 2 LOOP LAP; 17 ; Cá»ng: 39 chu kỳ

- 39. 7.4 VĂ o ra báș±ng DMA â Há» VXL vá»i DMAC CPU HOLD Bá» nhá» Thiáșżt bá» vĂ o/ra Bá» Äiá»u khiá»n DMA HLDA DRQ DACK Bus há» thá»ng

- 40. 7.4 VĂ o ra báș±ng DMA â Chu trĂŹnh vĂ o ra báș±ng DMA 1. Thiáșżt bá» vĂ o ra cĂł yĂȘu cáș§u trao Äá»i dữ liá»u gá»i yĂȘu cáș§u DRQ Äáșżn CPU thĂŽng qua DMAC; 2. DMAC chuyá»n yĂȘu cáș§u DRQ thĂ nh HRQ vĂ gá»i Äáșżn chĂąn tĂn hiá»u HOLD của CPU; 3. Nháșn ÄÆ°á»Łc yĂȘu cáș§u sá» dỄng bus HRQ, CPU: a. Gá»i cĂĄc tham sá» Äiá»u khiá»n trao Äá»i dữ liá»u vĂ tĂn hiá»u xĂĄc nháșn yĂȘu cáș§u sá» dỄng bus HACK cho DMAC qua chĂąn tĂn hiá»u HLDA; b. Tá»± tĂĄch ra khá»i bus há» thá»ng (100% cĂĄc tĂn hiá»u của bus A vĂ D vĂ má»t sá» tĂn hiá»u của bus C) 4. Nháșn ÄÆ°á»Łc HACK, DMAC chiáșżm quyá»n Äiá»u khiá»n bus há» thá»ng vĂ gá»i tĂn hiá»u xĂĄc nháșn DACK cho thiáșżt bá» vĂ o ra; 5. DMAC Äiá»u khiá»n quĂĄ trĂŹnh trao Äá»i dữ liá»u trá»±c tiáșżp giữa thiáșżt bá» vĂ o ra vĂ bá» nhá»; 6. Káșżt thĂșc quĂĄ trĂŹnh DMA, DMAC tráșŁ quyá»n Äiá»u khiá»n bus cho CPU.

- 41. 7.4 VĂ o ra báș±ng DMA â ÆŻu vĂ nhÆ°á»Łc Äiá»m ï¶ ÆŻu Äiá»m: ï§ Hiá»u suáș„t ráș„t cao do dữ liá»u ÄÆ°á»Łc trao Äá»i trá»±c tiáșżp theo khá»i giữa thiáșżt bá» vĂ o ra vĂ bá» nhá» khĂŽng thĂŽng qua CPU ï¶ NhÆ°á»Łc Äiá»m: ï§ Phức táșĄp hÆĄn vĂ o ra báș±ng thÄm dĂČ vĂ ngáșŻt ï§ Cáș§n máșĄch pháș§n cứng Äá» Äiá»u khiá»n quĂĄ trĂŹnh DMA ï¶ BĂȘn chủ Äá»ng trong vĂ o ra báș±ng DMA: ï§ Thiáșżt bá» vĂ o ra

- 42. 7.4 MáșĄch Äiá»u khiá»n DMA 8237 ï¶ Há» trợ 4 kĂȘnh DMA Äá»c láșp ï¶ Tá»± Äá»ng khá»i táșĄo Äá»c láșp cho táș„t cáșŁ cĂĄc kĂȘnh ï¶ Äiá»u khiá»n cho phĂ©p hoáș·c cáș„m từng yĂȘu cáș§u DMA riĂȘng láș» ï¶ Truyá»n từ bá» nhá» tá»i bá» nhá» ï¶ Khá»i táșĄo cĂĄc khá»i bá» nhá» ï¶ Tá»± Äá»ng tÄng/giáșŁm Äá»a chá» ï¶ Tá»c Äá» truyá»n dữ liá»u tá»i 1.6MB/s vá»i 8237A á» 5MHz

- 43. 7.4 CĂĄc tĂn hiá»u của 8237

![7.4 VĂ o ra báș±ng DMA â Giá»i thiá»u

ï¶ DMAC (DMA Controller) thay máș·t CPU Äiá»u khiá»n quĂĄ trĂŹnh

trao Äá»i dữ liá»u trá»±c tiáșżp giữa thiáșżt bá» vĂ o ra vĂ bá» nhá»;

ï¶ DMA cĂł tá»c Äá» cao hÆĄn nhiá»u láș§n so vá»i vĂ o ra báș±ng thÄm

dĂČ vĂ ngáșŻt. VĂ dỄ, vá»i VXL 8088:

ï§ VĂ o ra báș±ng DMA máș„t 4 chu kỳ Äá»ng há» Äá» chuyá»n 1 byte thiáșżt

bá» ngoáșĄi vi vĂ o bá» nhá»;

ï§ VĂ o ra thĂŽng qua CPU máș„t 39 chu kỳ Äá»ng há» Äá» chuyá»n 1

byte thiáșżt bá» ngoáșĄi vi vĂ o bá» nhá»:

;Sá» chu kỳ Äá»ng há»

LAP: MOV AL, [SI]; 10

OUT PORT, AL; 10

INC SI; 2

LOOP LAP; 17

; Cá»ng: 39 chu kỳ](https://image.slidesharecdn.com/ktmt-chuong7-ccphngphpvora-240625190955-b05b5cc7/85/KTMT-Chuong-7-Cac-ph-ng-phap-vao-ra-pptx-38-320.jpg)

![[PPT11] BĂ i 7 - Äá»c - VĂ tĂŽi váș«n muá»n máșč....ppt](https://cdn.slidesharecdn.com/ss_thumbnails/ppt11bi7-c-vtivnmunm-250305063122-6e221a47-thumbnail.jpg?width=560&fit=bounds)

![[PPT11] BĂ i 7 - Äá»c - CĂ Mau quĂȘ xứ.pptx](https://cdn.slidesharecdn.com/ss_thumbnails/ppt11bi7-c-cmauqux-250305070313-62766c8d-thumbnail.jpg?width=560&fit=bounds)