LLVM Overview

0 likes993 views

LLVM is a set of reusable compiler and toolchain technologies that includes an intermediate representation (IR), optimizers, code generators, and debugging tools. It decouples the front end and back end of compilers to support multiple languages and instruction sets. LLVM works by taking source code, generating LLVM IR, running optimizations on the IR, and creating object files, assembly, or machine code. The IR uses static single assignment form and phi nodes to simplify analysis and optimization.

1 of 20

Downloaded 39 times

![Static Single Assignment

Let's consider the following code:

int main(int argc, const char* argv[])

{

int i = 1;

i = i * 2;

return 0;

}

Which yields us...](https://image.slidesharecdn.com/llvmoverview-140624080020-phpapp02/85/LLVM-Overview-11-320.jpg)

![define void @func(i1 zeroext %first, i1 zeroext %second) #0 {

%1 = alloca i8, align 1

%2 = alloca i8, align 1

%third = alloca i8, align 1

%3 = zext i1 %first to i8

store i8 %3, i8* %1, align 1

%4 = zext i1 %second to i8

store i8 %4, i8* %2, align 1

%5 = load i8* %1, align 1 ; Decide what's first || second

%6 = trunc i8 %5 to i1 ; and store it in %6

br i1 %6, label %10, label %7 ; The actually interesting part, labeled %0

; <label>:7

%8 = load i8* %2, align 1

%9 = trunc i8 %8 to i1

br label %10 ; labeled %7

; <label>:10 ; preds = %7, %0

%11 = phi i1 [ true, %0 ], [ %9, %7 ] ; ... yield true if came from %0, otherwise yield %9

%12 = zext i1 %11 to i8

store i8 %12, i8* %third, align 1

ret void

}](https://image.slidesharecdn.com/llvmoverview-140624080020-phpapp02/85/LLVM-Overview-17-320.jpg)

Ad

Recommended

04a intro while

04a intro whilehasfaa1017

╠²

The document discusses repetition (looping) control structures in C++, including count-controlled, sentinel-controlled, and flag-controlled loops. It covers the general form of the while statement, how to properly initialize and update the loop control variable, and provides examples of using while loops to output a series of numbers, calculate a sum, and display even numbers between ranges.Evaluation of postfix expression

Evaluation of postfix expressionAkhil Ahuja

╠²

This document discusses postfix notation for evaluating mathematical expressions. It begins by explaining that postfix notation, also called reverse polish notation, writes operators after their operands. It then covers the precedence of operators in postfix notation and the fundamental principles of evaluating a postfix expression using a stack. Key advantages of postfix notation are that operator precedence is unnecessary and the order of evaluation is determined by the position of operators and operands. An example is provided to demonstrate how to manually evaluate a postfix expression step-by-step using a stack.Project on digital vlsi design

Project on digital vlsi designDINESH DEVIREDDY

╠²

This document describes the implementation of an 8-bit Booth multiplier using Verilog code. It includes an introduction to Booth's multiplication algorithm, which multiplies two signed binary numbers in two's complement notation. The architecture of the 8-bit Booth multiplier is shown in a block diagram. Verilog code for the Booth multiplier is provided, along with a testbench. Schematic and symbol diagrams illustrate the design. Simulation waveforms confirm the multiplier works as intended. In conclusion, Booth multipliers are found to have advantages over combinational multipliers in terms of area and complexity.Infix to postfix

Infix to postfixSaeed Farooqi

╠²

Mohammad Saeed Farooqi presented on data structures and algorithms. He discussed infix, postfix, and prefix notation, operator precedence, evaluating postfix expressions using stacks, and converting infix to postfix using stacks. He provided examples and algorithms for postfix expression evaluation and converting between infix, postfix, and prefix notation.Tcs nqt 2019 p 1

Tcs nqt 2019 p 1Phaneendra Bolla

╠²

This document discusses a Java program to determine if a given year is a leap year or not. It presents the algorithm, which checks if the year is divisible by 4 or 400 with a remainder of 0, in which case it returns 1, otherwise it returns 0. The code implements this by taking user input, passing it to a leap() method that performs the check, and prints the return value. It provides example outputs showing it correctly identifies 2016 and 2048 as leap years, and 1803 as a non-leap year.Tcs nqt 2019 p 2

Tcs nqt 2019 p 2Phaneendra Bolla

╠²

This document describes a Java program to check if a given number is prime or not. It takes input from the user and first checks if the number is positive using a check() method. If positive, it calls a prime() method that uses modulo operation to test for divisibility to return true if prime, false if not. It handles exceptions for non-integer input as well. The algorithm and program are explained step-by-step with sample outputs shown.Recursion

RecursionNikxjon

╠²

Recursion in C allows functions to call themselves, known as recursive functions. Recursion can result in elegant code by breaking problems down into similar subproblems, but it risks infinite loops unless an exit condition is defined. Examples of using recursion in C include calculating factorials and generating the Fibonacci sequence, where recursive functions call themselves with decreasing arguments until a base case is reached.computer notes - Evaluating postfix expressions

computer notes - Evaluating postfix expressionsecomputernotes

╠²

The document discusses evaluating postfix expressions using a stack. It provides an algorithm to evaluate a postfix expression by pushing operands onto a stack and popping operands to apply operators. An example is worked through step-by-step. It also discusses converting infix expressions to postfix by pushing operators onto a stack and handling operator precedence.20BCE1734.pdf

20BCE1734.pdfMridul Jadon

╠²

This document describes two programs that implement synchronization between two threads accessing a critical section. The first program uses Peterson's solution with a global count variable that is incremented by one thread and decremented by the other. The second program uses semaphores for synchronization, with one thread incrementing and the other decrementing a shared variable. Both aim to safely update the variable value through the critical section five times each.Mycasestudy

MycasestudyEmmanuel college

╠²

The document discusses infix, postfix, and prefix notations for mathematical expressions. It provides examples to illustrate the differences between the notations. The key points are:

- Infix notation writes operators between operands, like "X + Y". Postfix writes operators after operands, like "XY+". Prefix writes operators before operands, like "+ XY".

- Expressions can be converted between the notations algorithmically by fully parenthesizing the expression and moving operators to the position of matching parentheses.

- Converting an expression to postfix moves operators to the position of the right parenthesis, while prefix moves operators to the left parenthesis position.Chap 3 c++

Chap 3 c++Widad Jamaluddin

╠²

This document provides an overview of input and output operations, preprocessor directives, and debugging syntax errors in C++. It discusses including the iostream and string libraries for input/output and string processing. It covers input and output statements using cin and cout, constants, and increment/decrement operators. The document also reviews preprocessor directives like #include and #define, and manipulators for formatting output. It concludes with debugging syntax errors and understanding semantics.Infix-Postfix expression conversion

Infix-Postfix expression conversionRashmiranja625

╠²

The document discusses converting infix expressions to postfix expressions using a stack. It defines infix and postfix expressions, provides examples of each, and presents an algorithm that uses a stack to scan an infix expression from left to right and output an equivalent postfix expression. Key steps include pushing operators to the stack based on precedence and popping operators to the output when encountering operands and parentheses.Infix to Postfix Conversion Using Stack

Infix to Postfix Conversion Using StackSoumen Santra

╠²

The document describes the algorithm for converting infix expressions to postfix notation using a stack. It outlines the steps for handling operands, operators, and parentheses while traversing the infix expression. The implementation is presented in C programming language with a sample code demonstrating the conversion process.Looping in c language

Looping in c languageInfinity Tech Solutions

╠²

The document discusses control statements and looping in C programming, focusing on loop types such as 'for', 'while', and 'do-while'. It explains the basic structure and differences between entry-controlled and exit-controlled loops, along with syntax examples for each type of loop. Additionally, it provides potential exam questions related to loop control statements.Conversion of Infix To Postfix Expressions

Conversion of Infix To Postfix Expressions Kulachi Hansraj Model School Ashok Vihar

╠²

Stacks have several application areas including:

1) When functions are called to save return addresses and local variables.

2) To convert infix expressions to postfix form by acting as a placeholder.

3) To evaluate postfix expressions by holding operands and intermediate results.Booth algorithm

Booth algorithmSaif Al-Kalbani

╠²

This document presents two algorithms for multiplication: multiplication of unsigned numbers and Booth's algorithm. It includes outlines, requirements, design choices, flowcharts and code demonstrations for each algorithm. The requirements are to write a program that takes decimal inputs, displays step-by-step traces, and does not crash on invalid inputs. The algorithms are implemented in C++ sequentially according to flowcharts. Booth's algorithm handles signed numbers using 2's complement representation.Assignment8

Assignment8Sunita Milind Dol

╠²

This document discusses implementing a top-down predictive parser using predictive parsing techniques. It explains the theory behind predictive parsing, including how to construct a transition diagram from a grammar to write a predictive parsing program. An example grammar and input string are provided to demonstrate how the predictive parser would parse the string step-by-step using the transition diagrams. The document concludes by mentioning an example predictive parsing program that was implemented.Arrays c4 c5

Arrays c4 c5Omar Al-Sabek

╠²

The document discusses arrays and matrices in Pascal programming. It defines arrays as collections of related data elements that all have the same data type. Matrices are two-dimensional arrays that have rows and columns. The document shows how to declare, initialize, and fill arrays and matrices using loops. It also demonstrates accessing individual elements and printing the contents.Technical questions

Technical questionsKirthan S Holla

╠²

This document contains 25 multiple choice questions about data types, operators, functions, structures, and control flow statements in C programming. For each question there are 4 possible answers with one being identified as the correct answer. The questions cover a range of fundamental C programming concepts and test understanding of how different language constructs work.Programming in Arduino (Part 2)

Programming in Arduino (Part 2)Niket Chandrawanshi

╠²

The document discusses various control structures and functions used in Arduino programming including decision making structures like if, else if, else statements and switch case statements. It also covers different types of loops like while, do-while and for loops that allow repeating blocks of code. Functions are described as reusable blocks of code that perform tasks and help organize a program. Strings can be implemented as character arrays or using the String class, and various string functions are provided to manipulate and work with strings.Programming in Arduino (Part 1)

Programming in Arduino (Part 1)Niket Chandrawanshi

╠²

The document provides a comprehensive overview of data types in Arduino programming using C, detailing various data types such as int, char, float, and their respective memory usage and examples. It also explains the concept of variable scope, including local and global variables, along with key operators like arithmetic, comparison, boolean, and bitwise operators. Additionally, it introduces compound operators and illustrates their usage within the programming context.Infix postfixcoversion

Infix postfixcoversionPdr Patnaik

╠²

Infix notation writes operators between operands, like A + B. Postfix writes operators after operands, like AB+. Prefix writes operators before operands, like +AB. To convert infix to postfix:

1. Scan the infix expression left to right for tokens

2. Append operands to the postfix string

3. Push operators and parentheses to the stack according to precedence rules

4. Pop operators from the stack and append to postfix when encountering closing parentheses

5. Pop all remaining operators from the stack and append to postfix when finished.Control Statements, Array, Pointer, Structures

Control Statements, Array, Pointer, Structuresindra Kishor

╠²

The document covers fundamental concepts of computer programming in C, focusing on control statements such as 'if', 'switch', and loops ('for', 'while', 'do-while'). It discusses the syntax, execution flow, and practical examples of these constructs, emphasizing their importance in controlling the flow of program execution. Additionally, the document introduces arrays as a data structure for storing collections of elements of the same type.Prefix, Infix and Post-fix Notations

Prefix, Infix and Post-fix NotationsAfaq Mansoor Khan

╠²

The document provides a comprehensive overview of stack data structures and their related notations, including infix, prefix, and postfix notations. It discusses the characteristics, conversion algorithms, and evaluation techniques for these notations. The document concludes with references for further reading on the topic.LAS16-501: Introduction to LLVM - Projects, Components, Integration, Internals

LAS16-501: Introduction to LLVM - Projects, Components, Integration, InternalsLinaro

╠²

The document provides an in-depth overview of the LLVM project, detailing its various components including front-ends (like Clang), middle-end optimizations, back-end targets, and associated libraries and tools. It discusses the architectural differences with GNU tools, the intricacies of intermediate representation (IR), optimization passes, and the LLVM linker (lld) functionalities. Specific implementation details, such as ABI differences, IR transformations, and the sanitizers for memory debugging, are also outlined.07 140430-ipp-languages used in llvm during compilation

07 140430-ipp-languages used in llvm during compilationAdam Hus├Īr

╠²

The document describes the languages and representations used at each stage of compilation in LLVM. It discusses how the C/C++ frontend transforms source code into an AST then LLVM IR. The optimizer performs optimizations on the LLVM IR. The backend lowers the LLVM IR into a selection DAG with machine instructions and finally emits assembly code. The compilation process translates from the original high-level language into target-specific assembly.Part II: LLVM Intermediate Representation

Part II: LLVM Intermediate RepresentationWei-Ren Chen

╠²

This document discusses the LLVM intermediate representation (IR) and the lowering process from LLVM IR to machine code. It covers:

1) The characteristics of LLVM IR including SSA form, infinite virtual registers, and phi nodes.

2) How the LLVM IRBuilder class is used to conveniently generate LLVM instructions.

3) The lowering flow from LLVM IR to selection DAGs to machine DAGs to machine instructions and finally machine code.

4) How assembler relaxation can optimize and correct instructions during assembly.COMPILER_DESIGN_CLASS 2.ppt

COMPILER_DESIGN_CLASS 2.pptssuserebb9821

╠²

The document discusses code generation in compilers. It covers topics like instruction selection, register allocation, basic blocks, peephole optimizations, and global register allocation. The final phase of a compiler is code generation, which takes an intermediate representation and symbol table and produces target code. Key tasks include instruction selection, register allocation and assignment, and instruction ordering.COMPILER_DESIGN_CLASS 1.pptx

COMPILER_DESIGN_CLASS 1.pptxssuserebb9821

╠²

The document discusses code generation in compilers. It covers topics like instruction selection, register allocation, basic blocks, peephole optimizations, and global register allocation. The final phase of a compiler is code generation, which takes an intermediate representation and symbol table and produces target code. Key tasks include instruction selection, register allocation and assignment, and instruction ordering.05 instruction set design and architecture

05 instruction set design and architectureWaqar Jamil

╠²

This document summarizes key aspects of instruction set architecture (ISA) design. It discusses different classifications of ISAs such as accumulator, stack-based, memory-memory, register-memory, and load-store architectures. It also covers operand locations, types of addressing modes, operations, and evolution of instruction sets. The document concludes by previewing that the next topic will cover the MIPS instruction set as a case study.More Related Content

What's hot (16)

20BCE1734.pdf

20BCE1734.pdfMridul Jadon

╠²

This document describes two programs that implement synchronization between two threads accessing a critical section. The first program uses Peterson's solution with a global count variable that is incremented by one thread and decremented by the other. The second program uses semaphores for synchronization, with one thread incrementing and the other decrementing a shared variable. Both aim to safely update the variable value through the critical section five times each.Mycasestudy

MycasestudyEmmanuel college

╠²

The document discusses infix, postfix, and prefix notations for mathematical expressions. It provides examples to illustrate the differences between the notations. The key points are:

- Infix notation writes operators between operands, like "X + Y". Postfix writes operators after operands, like "XY+". Prefix writes operators before operands, like "+ XY".

- Expressions can be converted between the notations algorithmically by fully parenthesizing the expression and moving operators to the position of matching parentheses.

- Converting an expression to postfix moves operators to the position of the right parenthesis, while prefix moves operators to the left parenthesis position.Chap 3 c++

Chap 3 c++Widad Jamaluddin

╠²

This document provides an overview of input and output operations, preprocessor directives, and debugging syntax errors in C++. It discusses including the iostream and string libraries for input/output and string processing. It covers input and output statements using cin and cout, constants, and increment/decrement operators. The document also reviews preprocessor directives like #include and #define, and manipulators for formatting output. It concludes with debugging syntax errors and understanding semantics.Infix-Postfix expression conversion

Infix-Postfix expression conversionRashmiranja625

╠²

The document discusses converting infix expressions to postfix expressions using a stack. It defines infix and postfix expressions, provides examples of each, and presents an algorithm that uses a stack to scan an infix expression from left to right and output an equivalent postfix expression. Key steps include pushing operators to the stack based on precedence and popping operators to the output when encountering operands and parentheses.Infix to Postfix Conversion Using Stack

Infix to Postfix Conversion Using StackSoumen Santra

╠²

The document describes the algorithm for converting infix expressions to postfix notation using a stack. It outlines the steps for handling operands, operators, and parentheses while traversing the infix expression. The implementation is presented in C programming language with a sample code demonstrating the conversion process.Looping in c language

Looping in c languageInfinity Tech Solutions

╠²

The document discusses control statements and looping in C programming, focusing on loop types such as 'for', 'while', and 'do-while'. It explains the basic structure and differences between entry-controlled and exit-controlled loops, along with syntax examples for each type of loop. Additionally, it provides potential exam questions related to loop control statements.Conversion of Infix To Postfix Expressions

Conversion of Infix To Postfix Expressions Kulachi Hansraj Model School Ashok Vihar

╠²

Stacks have several application areas including:

1) When functions are called to save return addresses and local variables.

2) To convert infix expressions to postfix form by acting as a placeholder.

3) To evaluate postfix expressions by holding operands and intermediate results.Booth algorithm

Booth algorithmSaif Al-Kalbani

╠²

This document presents two algorithms for multiplication: multiplication of unsigned numbers and Booth's algorithm. It includes outlines, requirements, design choices, flowcharts and code demonstrations for each algorithm. The requirements are to write a program that takes decimal inputs, displays step-by-step traces, and does not crash on invalid inputs. The algorithms are implemented in C++ sequentially according to flowcharts. Booth's algorithm handles signed numbers using 2's complement representation.Assignment8

Assignment8Sunita Milind Dol

╠²

This document discusses implementing a top-down predictive parser using predictive parsing techniques. It explains the theory behind predictive parsing, including how to construct a transition diagram from a grammar to write a predictive parsing program. An example grammar and input string are provided to demonstrate how the predictive parser would parse the string step-by-step using the transition diagrams. The document concludes by mentioning an example predictive parsing program that was implemented.Arrays c4 c5

Arrays c4 c5Omar Al-Sabek

╠²

The document discusses arrays and matrices in Pascal programming. It defines arrays as collections of related data elements that all have the same data type. Matrices are two-dimensional arrays that have rows and columns. The document shows how to declare, initialize, and fill arrays and matrices using loops. It also demonstrates accessing individual elements and printing the contents.Technical questions

Technical questionsKirthan S Holla

╠²

This document contains 25 multiple choice questions about data types, operators, functions, structures, and control flow statements in C programming. For each question there are 4 possible answers with one being identified as the correct answer. The questions cover a range of fundamental C programming concepts and test understanding of how different language constructs work.Programming in Arduino (Part 2)

Programming in Arduino (Part 2)Niket Chandrawanshi

╠²

The document discusses various control structures and functions used in Arduino programming including decision making structures like if, else if, else statements and switch case statements. It also covers different types of loops like while, do-while and for loops that allow repeating blocks of code. Functions are described as reusable blocks of code that perform tasks and help organize a program. Strings can be implemented as character arrays or using the String class, and various string functions are provided to manipulate and work with strings.Programming in Arduino (Part 1)

Programming in Arduino (Part 1)Niket Chandrawanshi

╠²

The document provides a comprehensive overview of data types in Arduino programming using C, detailing various data types such as int, char, float, and their respective memory usage and examples. It also explains the concept of variable scope, including local and global variables, along with key operators like arithmetic, comparison, boolean, and bitwise operators. Additionally, it introduces compound operators and illustrates their usage within the programming context.Infix postfixcoversion

Infix postfixcoversionPdr Patnaik

╠²

Infix notation writes operators between operands, like A + B. Postfix writes operators after operands, like AB+. Prefix writes operators before operands, like +AB. To convert infix to postfix:

1. Scan the infix expression left to right for tokens

2. Append operands to the postfix string

3. Push operators and parentheses to the stack according to precedence rules

4. Pop operators from the stack and append to postfix when encountering closing parentheses

5. Pop all remaining operators from the stack and append to postfix when finished.Control Statements, Array, Pointer, Structures

Control Statements, Array, Pointer, Structuresindra Kishor

╠²

The document covers fundamental concepts of computer programming in C, focusing on control statements such as 'if', 'switch', and loops ('for', 'while', 'do-while'). It discusses the syntax, execution flow, and practical examples of these constructs, emphasizing their importance in controlling the flow of program execution. Additionally, the document introduces arrays as a data structure for storing collections of elements of the same type.Prefix, Infix and Post-fix Notations

Prefix, Infix and Post-fix NotationsAfaq Mansoor Khan

╠²

The document provides a comprehensive overview of stack data structures and their related notations, including infix, prefix, and postfix notations. It discusses the characteristics, conversion algorithms, and evaluation techniques for these notations. The document concludes with references for further reading on the topic.Similar to LLVM Overview (20)

LAS16-501: Introduction to LLVM - Projects, Components, Integration, Internals

LAS16-501: Introduction to LLVM - Projects, Components, Integration, InternalsLinaro

╠²

The document provides an in-depth overview of the LLVM project, detailing its various components including front-ends (like Clang), middle-end optimizations, back-end targets, and associated libraries and tools. It discusses the architectural differences with GNU tools, the intricacies of intermediate representation (IR), optimization passes, and the LLVM linker (lld) functionalities. Specific implementation details, such as ABI differences, IR transformations, and the sanitizers for memory debugging, are also outlined.07 140430-ipp-languages used in llvm during compilation

07 140430-ipp-languages used in llvm during compilationAdam Hus├Īr

╠²

The document describes the languages and representations used at each stage of compilation in LLVM. It discusses how the C/C++ frontend transforms source code into an AST then LLVM IR. The optimizer performs optimizations on the LLVM IR. The backend lowers the LLVM IR into a selection DAG with machine instructions and finally emits assembly code. The compilation process translates from the original high-level language into target-specific assembly.Part II: LLVM Intermediate Representation

Part II: LLVM Intermediate RepresentationWei-Ren Chen

╠²

This document discusses the LLVM intermediate representation (IR) and the lowering process from LLVM IR to machine code. It covers:

1) The characteristics of LLVM IR including SSA form, infinite virtual registers, and phi nodes.

2) How the LLVM IRBuilder class is used to conveniently generate LLVM instructions.

3) The lowering flow from LLVM IR to selection DAGs to machine DAGs to machine instructions and finally machine code.

4) How assembler relaxation can optimize and correct instructions during assembly.COMPILER_DESIGN_CLASS 2.ppt

COMPILER_DESIGN_CLASS 2.pptssuserebb9821

╠²

The document discusses code generation in compilers. It covers topics like instruction selection, register allocation, basic blocks, peephole optimizations, and global register allocation. The final phase of a compiler is code generation, which takes an intermediate representation and symbol table and produces target code. Key tasks include instruction selection, register allocation and assignment, and instruction ordering.COMPILER_DESIGN_CLASS 1.pptx

COMPILER_DESIGN_CLASS 1.pptxssuserebb9821

╠²

The document discusses code generation in compilers. It covers topics like instruction selection, register allocation, basic blocks, peephole optimizations, and global register allocation. The final phase of a compiler is code generation, which takes an intermediate representation and symbol table and produces target code. Key tasks include instruction selection, register allocation and assignment, and instruction ordering.05 instruction set design and architecture

05 instruction set design and architectureWaqar Jamil

╠²

This document summarizes key aspects of instruction set architecture (ISA) design. It discusses different classifications of ISAs such as accumulator, stack-based, memory-memory, register-memory, and load-store architectures. It also covers operand locations, types of addressing modes, operations, and evolution of instruction sets. The document concludes by previewing that the next topic will cover the MIPS instruction set as a case study.LLVM

LLVMguest3e5046

╠²

The document discusses the LLVM compiler framework and infrastructure. It provides reusable components for building compilers to reduce the time and cost of building new compilers. The LLVM compiler framework uses the LLVM infrastructure to build static compilers, JITs, and trace-based optimizers. It emits C code or native code for x86, Sparc, and PowerPC architectures. The three primary LLVM components are the virtual instruction set (the common language- and target-independent intermediate representation), a collection of well-integrated libraries, and a collection of tools built from the libraries.Introduction to Compiler Development

Introduction to Compiler DevelopmentLogan Chien

╠²

The document provides an introduction to compiler development by Logan Chien, covering compiler technologies, their significance in programming, and insights into industrial-strength compiler design. It outlines key components of compilers, such as lexers, parsers, and code generators, and discusses advanced topics like optimization, analysis, and different architectures. The presentation aims to bridge academia and industry by highlighting the essential skills and knowledge required for effective compiler development.MCES 21CS43 Module 3 microcontroller notes

MCES 21CS43 Module 3 microcontroller notesvinodthrupthi

╠²

The document discusses efficient structure arrangement, bit-fields, unaligned data, and endianness in ARM programming with C compilers. It emphasizes the importance of struct layout to improve memory usage, advises against using bit-fields due to inefficiency and lack of standardization, and recommends best practices for handling unaligned data and endian issues. Additionally, it points out that division operations are costly in terms of cycles and suggests methods to optimize division handling.ąÜą░ą║ čĆą░ą▒ąŠčéą░ąĄčé LLVM ą▒菹║ąĄąĮą┤ ą▓ C#. ąĢą│ąŠčĆ ąæąŠą│ą░č鹊ą▓ Ō×Ā CoreHard Autumn 2019

ąÜą░ą║ čĆą░ą▒ąŠčéą░ąĄčé LLVM ą▒菹║ąĄąĮą┤ ą▓ C#. ąĢą│ąŠčĆ ąæąŠą│ą░č鹊ą▓ Ō×Ā CoreHard Autumn 2019corehard_by

╠²

The document discusses the integration of LLVM with C# and the Mono runtime, detailing how C# intermediate language (CIL) can be transformed to LLVM IR for various optimizations and code generation. Key topics include the conversion of simple functions to LLVM, the use of profiling data for improved optimizations, and the importance of specific LLVM hints for effective code generation. Furthermore, it highlights how intrinsic math functions are optimized using LLVM, providing several examples of optimizations and transformations applied to C# code.TMPA-2017: Vellvm - Verifying the LLVM

TMPA-2017: Vellvm - Verifying the LLVMIosif Itkin

╠²

The document presents the Vellvm project, which focuses on verifying LLVM intermediate representation (IR) through formal methods and its implementation in Coq. It discusses various techniques for enhancing software reliability, safety, and correctness, highlighting the success of the CompCert C compiler in producing reliable optimizations that resist common bugs found in other compilers. The presentation details LLVMŌĆÖs operational semantics, the need for high assurance software, and the integration of verification into compiler infrastructure.Chapter_04_ARM_Assembly.pptx ARM ASSEMBLY CODE

Chapter_04_ARM_Assembly.pptx ARM ASSEMBLY CODENagarathnaRajur2

╠²

The document contains a PowerPoint presentation on ARM assembly language, outlining its basic and advanced instructions, branch instructions, and memory instructions, tailored for an educational setting. It includes explanations with semantic details of various ARM instructions, examples of programming tasks, and conditional logic. It is intended for use by authorized professors and educators in conjunction with a specific textbook and is prohibited from being reproduced or distributed without permission.Creating a Fibonacci Generator in Assembly - by Willem van Ketwich

Creating a Fibonacci Generator in Assembly - by Willem van KetwichWillem van Ketwich

╠²

The document outlines the creation of a Fibonacci generator in assembly language, detailing the algorithm, necessary assembly syntax, and tools. It includes steps for reading command line input, converting it to a number, generating Fibonacci numbers, and printing output. Additionally, it touches upon basic assembly concepts such as opcodes, registers, and memory management.iii-ii cd nCompiler design UNIT-V-1.pptx

iii-ii cd nCompiler design UNIT-V-1.pptxnandan543979

╠²

The document outlines the syllabus and course objectives for a compiler design course at DNR College of Engineering & Technology, covering various units such as language processing, lexical and syntax analysis, code generation, and optimization techniques. It emphasizes the practical application of compiler technology, including the use of tools like lex and yacc, as well as theoretical concepts such as static and dynamic scoping. Additionally, it includes references to key textbooks and specifies the learning outcomes for students in the course.5 - Advanced SVE.pdf

5 - Advanced SVE.pdfJunZhao68

╠²

The document discusses Arm C Language Extensions (ACLE) for supporting Arm features in C and C++. It provides an overview of ACLE intrinsics and data types for SVE, NEON, and FP16. It describes how to include headers to use different Arm features and provides examples of using SVE ACLE intrinsics to vectorize a scalar loop.UNIT IV Compiler.pptx RUNTIMEENVIRONMENT

UNIT IV Compiler.pptx RUNTIMEENVIRONMENTKavithaNagendran1

╠²

The document outlines the components and functionalities of run-time environments, including storage allocation strategies (static, stack, and heap), parameter passing, and symbol tables. It discusses the design of code generators, emphasizing aspects such as memory management, instruction selection, and register allocation, along with the identification and representation of basic blocks and flow graphs. Additionally, it details various code generation issues, approaches for optimal code generation, and the characteristics of basic blocks in programming constructs.Pragmatic Optimization in Modern Programming - Demystifying the Compiler

Pragmatic Optimization in Modern Programming - Demystifying the CompilerMarina Kolpakova

╠²

This document discusses compiler optimizations. It begins with an outline of topics including compilation trajectory, intermediate languages, optimization levels, and optimization techniques. It then provides more details on each phase of compilation, how compilers use intermediate representations to perform optimizations, and specific optimizations like common subexpression elimination, constant propagation, and instruction scheduling.Smalltalk JIT Compilation: LLVM Experimentation

Smalltalk JIT Compilation: LLVM ExperimentationESUG

╠²

The document discusses the features and benefits of Just-In-Time (JIT) compilation and LLVM, a toolset for building compilers. It explains how JIT improves performance by compiling methods dynamically at runtime and outlines the structure of LLVM's intermediate representation (IR) using Single Static Assignment (SSA). Additionally, it covers the process of generating textual LLVM IR and the various stages involved in emitting it, including flow analysis and example code snippets.microprocessors and ARM Assembly Language

microprocessors and ARM Assembly LanguageJoelAttati

╠²

ARM Assembly Language

Assemblers

Integrated development environment

basic microprocessor interfacing

ARM's Flow Control Instructions

Unconditional and Conditional Branch

Compare and Test

Branching and Loop Conditional execution

ąÜą░ą║ čĆą░ą▒ąŠčéą░ąĄčé LLVM ą▒菹║ąĄąĮą┤ ą▓ C#. ąĢą│ąŠčĆ ąæąŠą│ą░č鹊ą▓ Ō×Ā CoreHard Autumn 2019

ąÜą░ą║ čĆą░ą▒ąŠčéą░ąĄčé LLVM ą▒菹║ąĄąĮą┤ ą▓ C#. ąĢą│ąŠčĆ ąæąŠą│ą░č鹊ą▓ Ō×Ā CoreHard Autumn 2019corehard_by

╠²

Ad

Recently uploaded (20)

Heat Treatment Process Automation in India

Heat Treatment Process Automation in IndiaReckers Mechatronics

╠²

Automate your heat treatment processes for superior precision, consistency, and cost savings. Explore solutions for furnaces, quench systems. Heat treatment is a critical manufacturing process that alters the microstructure and properties of materials, typically metals, to achieve desired characteristics such as hardness, strength, ductility, and wear resistance. Shell Skill Tree - LabEx Certification (LabEx)

Shell Skill Tree - LabEx Certification (LabEx)VICTOR MAESTRE RAMIREZ

╠²

Shell Skill Tree - LabEx Certification (LabEx)Streamlining CI/CD with FME Flow: A Practical Guide

Streamlining CI/CD with FME Flow: A Practical GuideSafe Software

╠²

Join us as we explore how to deploy a fault-tolerant FME Flow installation using FME FlowŌĆÖs IaC templates alongside Terraform, AWS, and GitHub in a CI/CD workflow. This session will also cover how to leverage FMEŌĆÖs CI/CD capabilities for FME Flow upgrades and FME object migration between different environments, ensuring seamless automation and scalability.Modern Platform Engineering with Choreo - The AI-Native Internal Developer Pl...

Modern Platform Engineering with Choreo - The AI-Native Internal Developer Pl...WSO2

╠²

Building and operating internal platforms has become increasingly complex ŌĆö sprawling toolchains, rising costs, and fragmented developer experiences are slowing teams down. ItŌĆÖs time for a new approach.

This slide deck explores modern platform engineering with Choreo, WSO2ŌĆÖs AI-native Internal Developer Platform as a Service. Discover how you can streamline platform operations, empower your developers, and drive faster innovation ŌĆö all while reducing complexity and cost.

Learn more: https://wso2.com/choreo/platform-engineering/Women in Tech: Marketo Engage User Group - June 2025 - AJO with AWS

Women in Tech: Marketo Engage User Group - June 2025 - AJO with AWSBradBedford3

╠²

Creating meaningful, real-time engagement across channels is essential to building lasting business relationships. Discover how AWS, in collaboration with Deloitte, set up one of Adobe's first instances of Journey Optimizer B2B Edition to revolutionize customer journeys for B2B audiences.

This session will share the use cases the AWS team has the implemented leveraging Adobe's Journey Optimizer B2B alongside Marketo Engage and Real-Time CDP B2B to deliver unified, personalized experiences and drive impactful engagement.

They will discuss how they are positioning AJO B2B in their marketing strategy and how AWS is imagining AJO B2B and Marketo will continue to work together in the future.

Whether youŌĆÖre looking to enhance customer journeys or scale your B2B marketing efforts, youŌĆÖll leave with a clear view of what can be achieved to help transform your own approach.

Speakers:

Britney Young Senior Technical Product Manager, AWS

Erine de Leeuw Technical Product Manager, AWSNVIDIA GPU Technologies for AI and High-Performance Computing

NVIDIA GPU Technologies for AI and High-Performance ComputingSandeepKS52

╠²

The exploration of modern computing technologies reveals the significant role of advanced graphics processing units (GPUs) and their architectures, which enhance performance in various applications, from gaming to artificial intelligence. Understanding the interconnectivity provided by high-speed communication technologies, such as NVLink and NVSwitch, is crucial for optimizing data transfer and improving overall system efficiency. Additionally, the examination of DGX systems highlights how these powerful computing platforms are designed for scalability, allowing organizations to expand their computational capabilities seamlessly. Together, these topics provide a comprehensive overview of the innovations that drive high-performance computing and their implications for future technological advancements.

Foundations of Marketo Engage - Programs, Campaigns & Beyond - June 2025

Foundations of Marketo Engage - Programs, Campaigns & Beyond - June 2025BradBedford3

╠²

Join us for an exciting introductory session on, Foundations of Marketo Engage: Programs, Campaigns & Beyond. Ideal for new and early-stage users looking to build confidence and capability in Marketo Engage.

Our speakers for this session will be:

AJ Navarro

Marketing Operations Manager - Sprout Social

Bobby Coppola

Marketing Manager - Blue Yonder

This event will guide you through the essential steps to build strong, scalable Programs, Channels, Tags, Smart Campaigns, and Reporting Basics in Marketo Engage.

Attendees will gain practical knowledge on how to structure and launch marketing initiatives, leverage templates for efficiency, and implement best practices for campaign execution and measurement. You'll leave with actionable insights you can immediately apply to your own Marketo instance to improve organization, automation, and reporting. Marketo Engage.

Learn how to create impactful programs and understand the best practices for seamless campaign management and effective reporting.

DonŌĆÖt miss out on this opportunity to gain hands-on guidance from experienced practitioners and to connect with peers who are also new to the platform. Secure your spot today and start building your path to becoming a Marketo pro!

Please feel free to invite colleagues who you think would also benefit from this session.HYBRIDIZATION OF ALKANES AND ALKENES ...

HYBRIDIZATION OF ALKANES AND ALKENES ...karishmaduhijod1

╠²

Hybridization happens when atomic orbitals mix to form a new atomic orbital. Advance Doctor Appointment Booking App With Online Payment

Advance Doctor Appointment Booking App With Online PaymentAxisTechnolabs

╠²

/slideshow/advance-doctor-appointment-booking-app-with-online-payment/280654375IObit Driver Booster Pro 12 Crack Latest Version Download

IObit Driver Booster Pro 12 Crack Latest Version Downloadpcprocore

╠²

¤æēØŚĪØŚ╝ØśüØŚ▓:ØŚ¢ØŚ╝ØŚĮØśå ØŚ╣ØŚČØŚ╗ØŚĖ & ØŚĮØŚ«ØśĆØśüØŚ▓ ØŚČØŚ╗ØśüØŚ╝ ØŚÜØŚ╝ØŚ╝ØŚ┤ØŚ╣ØŚ▓ ØŚ╗ØŚ▓Øśä ØśüØŚ«ØŚ»¤ö┤Ō¢Č https://pcprocore.com/ ŌŚĆŌ£ģ

IObit Driver Booster Pro is the solution. It automatically downloads and updates drivers with just one click, avoiding hardware failures, system instability, and security vulnerabilities.MOVIE RECOMMENDATION SYSTEM, UDUMULA GOPI REDDY, Y24MC13085.pptx

MOVIE RECOMMENDATION SYSTEM, UDUMULA GOPI REDDY, Y24MC13085.pptxMaharshi Mallela

╠²

Movie recommendation system is a software application or algorithm designed to suggest movies to users based on their preferences, viewing history, or other relevant factors. The primary goal of such a system is to enhance user experience by providing personalized and relevant movie suggestions.Who will create the languages of the future?

Who will create the languages of the future?Jordi Cabot

╠²

Will future languages be created by language engineers?

Can you "vibe" a DSL?

In this talk, we will explore the changing landscape of language engineering and discuss how Artificial Intelligence and low-code/no-code techniques can play a role in this future by helping in the definition, use, execution, and testing of new languages. Even empowering non-tech users to create their own language infrastructure. Maybe without them even realizing. Milwaukee Marketo User Group June 2025 - Optimize and Enhance Efficiency - Sm...

Milwaukee Marketo User Group June 2025 - Optimize and Enhance Efficiency - Sm...BradBedford3

╠²

Inspired by the Adobe Summit hands-on lab, Optimize Your Marketo Instance Performance, review the recording from June 5th to learn best practices that can optimize your smart campaign and smart list processing time, inefficient practices to try to avoid, and tips and tricks for keeping your instance running smooth!

You will learn:

How smart campaign queueing works, how flow steps are prioritized, and configurations that slow down smart campaign processing.

Best practices for smart list and smart campaign configurations that yield greater reliability and processing efficiencies.

Generally recommended timelines for reviewing instance performance: walk away from this session with a guideline of what to review in Marketo and how often to review it.

This session will be helpful for any Marketo administrator looking for opportunities to improve and streamline their instance performance. Be sure to watch to learn best practices and connect with your local Marketo peers!Artificial Intelligence Workloads and Data Center Management

Artificial Intelligence Workloads and Data Center ManagementSandeepKS52

╠²

Data centers play a crucial role in the modern digital landscape, serving as the backbone for data storage, processing, and management. Understanding the structure and function of these facilities is essential, as they house the technology that supports various applications and services. The use of Kubernetes and container orchestration has transformed how software is deployed and managed, allowing for greater efficiency and scalability in handling applications. Additionally, the management of AI workloads presents unique challenges and opportunities, as organizations seek to optimize resources and performance for complex algorithms and data processing tasks. Together, these topics provide a comprehensive overview of the technologies and strategies that drive todayŌĆÖs information systems.

Making significant Software Architecture decisions

Making significant Software Architecture decisionsBert Jan Schrijver

╠²

Presented at the iSAQB Software Architecture Community NL meetup on 12-6-2025arctitecture application system design os dsa

arctitecture application system design os dsaza241967

╠²

wow amazing see and enjoy for this the best pdf slideshow you could see random shit is what i do best Smadav Pro 2025 Rev 15.4 Crack Full Version With Registration Key

Smadav Pro 2025 Rev 15.4 Crack Full Version With Registration Keyjoybepari360

╠²

Ō×Ī’ĖÅ ¤īŹ¤ō▒¤æēCOPY & PASTE LINK¤æē¤æē¤æē

https://crackpurely.site/smadav-pro-crack-full-version-registration-key/Best MLM Compensation Plans for Network Marketing Success in 2025

Best MLM Compensation Plans for Network Marketing Success in 2025LETSCMS Pvt. Ltd.

╠²

Discover the top MLM compensation plans including Unilevel, Binary, Matrix, Board, and Australian Plans. Learn how to choose the best plan for your business growth with expert insights from MLM Trees. Explore hybrid models, payout strategies, and earning potential.

Learn more: https://www.mlmtrees.com/mlm-plans/

Introduction to Agile Frameworks for Product Managers.pdf

Introduction to Agile Frameworks for Product Managers.pdfAli Vahed

╠²

As a Product Manager, having a solid understanding of Agile frameworks is essential, whether you are joining an established team or helping shape a new one.

Agile is not just a delivery method; it is a mind set that directly impacts how products are built, iterated, and brought to market. Knowing the strengths and trade-offs of each framework enables you to collaborate more effectively with teams, foster alignment, and drive meaningful outcomes.

Simply put, Agile fluency helps you lead with clarity in fast-paced, ever-changing environments.

The next few slides are simple ŌĆśSTUDY CARDSŌĆÖ to help you learn or refresh your understanding of a few popular Agile frameworks.Sysinfo OST to PST Converter Infographic

Sysinfo OST to PST Converter InfographicSysInfo Tools

╠²

The SysInfo OST to PST Converter is the most secure software to perform the OST to PST conversion. It converts OST files into various formats, including MBOX, EML, EMLX, HTML, and CSV, with 100% accuracy. Along with that, it imports OST files into different email clients like Office 365 and G Suite.

visit: https://www.sysinfotools.com/ost-to-pst-converter.phpAd

LLVM Overview

- 1. LLVM Overview Constantin Lungu, 2014

- 2. Agenda ŌĆó What is LLVM ŌĆó Why is it good ŌĆó How does it work ŌĆó IR, SSA, Phi nodes, data alignment

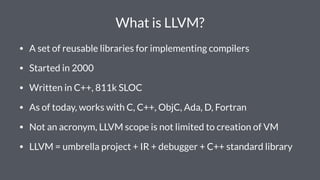

- 4. What is LLVM? ŌĆó A set of reusable libraries for implementing compilers ŌĆó Started in 2000 ŌĆó Written in C++, 811k SLOC ŌĆó As of today, works with C, C++, ObjC, Ada, D, Fortran ŌĆó Not an acronym, LLVM scope is not limited to creation of VM ŌĆó LLVM = umbrella project + IR + debugger + C++ standard library

- 5. Why is it good?

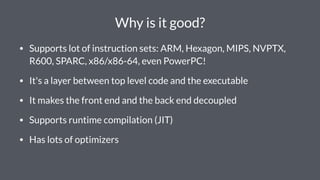

- 6. Why is it good? ŌĆó Supports lot of instruction sets: ARM, Hexagon, MIPS, NVPTX, R600, SPARC, x86/x86-64, even PowerPC! ŌĆó It's a layer between top level code and the executable ŌĆó It makes the front end and the back end decoupled ŌĆó Supports runtime compilation (JIT) ŌĆó Has lots of optimizers

- 7. How does it work?

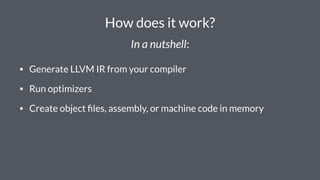

- 8. How does it work? In a nutshell: ŌĆó Generate LLVM IR from your compiler ŌĆó Run optimizers ŌĆó Create object ’¼üles, assembly, or machine code in memory

- 9. How does it work? ŌĆó Tokenise the source code ŌĆó Parse the token stream ŌĆó Build the AST ŌĆó Optimize IR ŌĆó Assemble

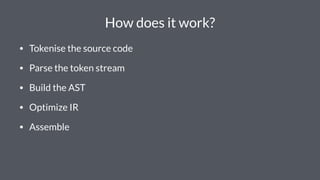

- 10. LLVM IR ŌĆó Unlimited SSA Register machine instruction set ŌĆó Representations: ŌĆó Human-readable LLVM assembly (.ll) ŌĆó Dense 'bitcode' binaries (.bc) ŌĆó C++ classes

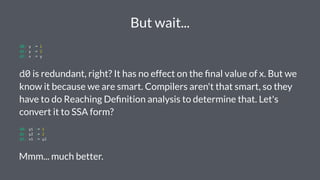

- 11. Static Single Assignment Let's consider the following code: int main(int argc, const char* argv[]) { int i = 1; i = i * 2; return 0; } Which yields us...

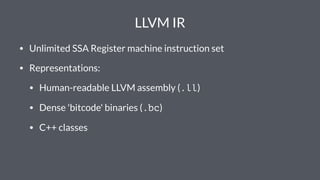

- 12. Static Single Assignment Note: LLVM registers are indexed. So %1 is the ’¼ürst allocated register, %2 is the second, etc. define i32 @main(i32 %argc, i8** %argv) #0 { %1 = alloca i32, align 4 %2 = alloca i32, align 4 %3 = alloca i8**, align 8 %i = alloca i32, align 4 ; declare i store i32 0, i32* %1 store i32 %argc, i32* %2, align 4 store i8** %argv, i8*** %3, align 8 ; startup till here store i32 1, i32* %i, align 4 ; store 1 in i %4 = load i32* %i, align 4 ; store i in %4 %5 = mul nsw i32 %4, 2 ; multiply %4 by 2 and store in %5 store i32 %5, i32* %i, align 4 ; store %5 in i ret i32 0 }

- 13. But wait... d0: y := 1 d1: y := 2 d2: x := y d0 is redundant, right? It has no effect on the ’¼ünal value of x. But we know it because we are smart. Compilers aren't that smart, so they have to do Reaching De’¼ünition analysis to determine that. Let's convert it to SSA form? d0: y1 := 1 d1: y2 := 2 d2: x1 := y2 Mmm... much better.

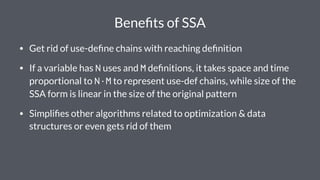

- 14. Bene’¼üts of SSA ŌĆó Get rid of use-de’¼üne chains with reaching de’¼ünition ŌĆó If a variable has N uses and M de’¼ünitions, it takes space and time proportional to N┬ĘM to represent use-def chains, while size of the SSA form is linear in the size of the original pattern ŌĆó Simpli’¼ües other algorithms related to optimization & data structures or even gets rid of them

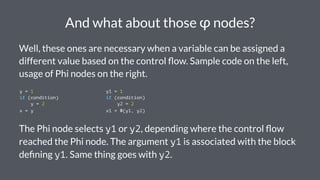

- 15. And what about those Žå nodes? Well, these ones are necessary when a variable can be assigned a different value based on the control ’¼éow. Sample code on the left, usage of Phi nodes on the right. y = 1 y1 = 1 if (condition) if (condition) y = 2 y2 = 2 x = y x1 = ╬”(y1, y2) The Phi node selects y1 or y2, depending where the control ’¼éow reached the Phi node. The argument y1 is associated with the block de’¼üning y1. Same thing goes with y2.

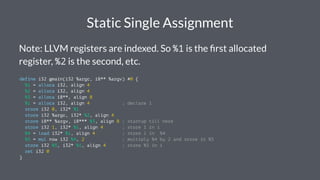

- 16. A better example of Žå nodes void func(bool first, bool second) { bool third = first || second; } Which yields us...

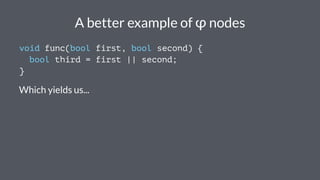

- 17. define void @func(i1 zeroext %first, i1 zeroext %second) #0 { %1 = alloca i8, align 1 %2 = alloca i8, align 1 %third = alloca i8, align 1 %3 = zext i1 %first to i8 store i8 %3, i8* %1, align 1 %4 = zext i1 %second to i8 store i8 %4, i8* %2, align 1 %5 = load i8* %1, align 1 ; Decide what's first || second %6 = trunc i8 %5 to i1 ; and store it in %6 br i1 %6, label %10, label %7 ; The actually interesting part, labeled %0 ; <label>:7 %8 = load i8* %2, align 1 %9 = trunc i8 %8 to i1 br label %10 ; labeled %7 ; <label>:10 ; preds = %7, %0 %11 = phi i1 [ true, %0 ], [ %9, %7 ] ; ... yield true if came from %0, otherwise yield %9 %12 = zext i1 %11 to i8 store i8 %12, i8* %third, align 1 ret void }

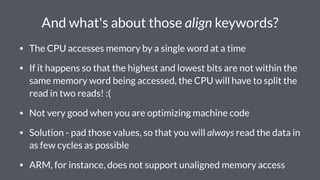

- 18. And what's about those align keywords? ŌĆó The CPU accesses memory by a single word at a time ŌĆó If it happens so that the highest and lowest bits are not within the same memory word being accessed, the CPU will have to split the read in two reads! :( ŌĆó Not very good when you are optimizing machine code ŌĆó Solution - pad those values, so that you will always read the data in as few cycles as possible ŌĆó ARM, for instance, does not support unaligned memory access

- 20. Thanks!