NISHANT_PATHAK_RESUME

- 1. NISHANT M. PATHAK CONTACT NO. : +91-9687559002/ 9427653489 E-MAIL ID : nishant.pathak2805@gmail.com CAREER OBJECTIVE To learn current trends of VLSI design and commit myself for dedicated hard work to develop skills and acquire knowledge to lead the organization towards new horizons of success, while holding a responsible position in semiconductor industry. WORK EXPERIENCE Organization : STMicroelectronics Private Ltd. Experience : June, 2015 to May, 2016 (Technical Intern). Title : Power and Signal Integrity of ASIC Design. PROJECT DESCRIPTION: ï· Pre estimation of functional failure and reliability of IPs due to excessive power loss and IR drop at different technology nodes as 28nm, 45nm and 90nm for CMOS and 130nm for BCD devices. ï· Reduction of the overall design cycle time addressing static and dynamic power integrity. ï· Static IR drop determining the IR-drop based on the average value of power distribution. ï· Full-chip vectorless and vectored Dynamic power and IR analysis, including the effects of decoupling capacitances and optimization. ï· Reduction of the crosstalk effects of IPs under process. ï· Verify the results with the help of Signoff Kit and smart power kit. TOOLS USED: RedHawk, Primetime, PrimeRail, StarRCXT. TECHNICAL SKILLS ï· Hardware Descriptive Language : Verilog. ï· Programming Language : C, C++, Assembly language for 8051 and 8086. ï· Scripting Language : PERL and TCL. ï· Operating Systems : Windows, LINUX. ï· Tools : Quartus II, Xilinx ISE Design Suite, Microwind, MATLAB, HSPICE, Express PCB, Keil, RedHawk PrimeTime, StarRCXT, Pyxis Layout, NCSim. Academic Projects ï· M.Tech. ï§ Design and Implementation of 4-Bit Magnitude Comparator using Xilinx ISE. ï RTL coding using Verilog HDL and implementation using Xilinx Spartan - 6 FPGA kit with complete layout using Microwind. ï§ FPGA Implementation of FIR Filter using Xilinx ISE and MATLAB. ï RTL coding using Verilog HDL and implementation using Xilinx Spartan- 6 FPGA kit. ï§ Hybrid Ge-Si based MOSFET with different gate oxides using Visual TCAD. ï Drew the structure using Visual TCAD and compared the obtained I-V and transfer characteristics for different gate contact material. ï§ EDA Tool for Fault Equivalence and Fault collapse ratio for a given ISCAS Netlist using Perl.

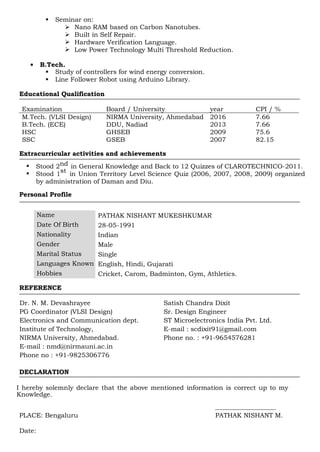

- 2. ï§ Seminar on: ï Nano RAM based on Carbon Nanotubes. ï Built in Self Repair. ï Hardware Verification Language. ï Low Power Technology Multi Threshold Reduction. ï· B.Tech. ï§ Study of controllers for wind energy conversion. ï§ Line Follower Robot using Arduino Library. Educational Qualification Examination Board / University year CPI / % M.Tech. (VLSI Design) NIRMA University, Ahmedabad 2016 7.66 B.Tech. (ECE) DDU, Nadiad 2013 7.66 HSC GHSEB 2009 75.6 SSC GSEB 2007 82.15 Extracurricular activities and achievements ï§ Stood 2nd in General Knowledge and Back to 12 Quizzes of CLAROTECHNICO-2011. ï§ Stood 1 st in Union Territory Level Science Quiz (2006, 2007, 2008, 2009) organized by administration of Daman and Diu. Personal Profile Name PATHAK NISHANT MUKESHKUMAR Date Of Birth 28-05-1991 Nationality Indian Gender Male Marital Status Single Languages Known English, Hindi, Gujarati Hobbies Cricket, Carom, Badminton, Gym, Athletics. REFERENCE Dr. N. M. Devashrayee Satish Chandra Dixit PG Coordinator (VLSI Design) Sr. Design Engineer Electronics and Communication dept. ST Microelectronics India Pvt. Ltd. Institute of Technology, E-mail : scdixit91@gmail.com NIRMA University, Ahmedabad. Phone no. : +91-9654576281 E-mail : nmd@nirmauni.ac.in Phone no : +91-9825306776 DECLARATION I hereby solemnly declare that the above mentioned information is correct up to my Knowledge. PLACE: Bengaluru PATHAK NISHANT M. Date: