Ppt

Download as PPTX, PDF0 likes288 views

The document discusses page tables and translation lookaside buffers (TLBs). It defines a page table as the data structure used in virtual memory systems to map virtual addresses to physical addresses. It describes implementations of page tables using hardware registers or storing the table in main memory with a page table base register. TLBs are caches of recent virtual to physical address translations that speed up the translation process by avoiding slow accesses to the full page table in main memory. The document also covers hierarchical/multi-level paging, memory protection using protection bits, shared pages, and the structure and operation of TLBs.

1 of 23

Download to read offline

![PAGE TABLES,

TRANSLATION

LOOKAHEAD BUFFERS

Submitted by

Tejal vinod kasture

Me[2nd year][1st sem]](https://image.slidesharecdn.com/ppt-161102135801/85/Ppt-1-320.jpg)

Recommended

Translation Look Aside buffer

Translation Look Aside buffer Zara Nawaz

╠²

this slides contain the contents related to the subject operations system topic which is translation look aside buffer Tlb

Tlbnaniix21_3

╠²

The TLB is a small cache that stores recent translations between virtual and physical memory addresses. On a memory reference, the CPU first checks the TLB for a matching translation. If found, it directly accesses memory; otherwise an exception occurs and the OS handles the translation by looking it up in the page table and updating the TLB. The benefit of the TLB is that its access is much faster than accessing the page table, improving memory access time and reducing paging overhead. The OS also has extra work to synchronize TLB and page table state.Translation lookaside buffer

Translation lookaside bufferChetan Mahawar

╠²

The translation look aside buffer (TLB) is a cache for page table entries. It works in much the same way as the data cache: it stores recently accessed page table entries. It also relies on locality of reference.

It is cumbersome and time consuming to calculate the physical address from linear address for every memory location. A Translation Look-aside Buffer (TLB) simplifies the process. TLB is a page table cache, which stores the 32 recently accessed page table entries.Semantics 2017 - Trying Not to Die Benchmarking using LITMUS

Semantics 2017 - Trying Not to Die Benchmarking using LITMUSHarsh Thakkar

╠²

The document discusses developing an open benchmarking framework called LITMUS to evaluate diverse data management systems (DMSs) in a standardized way. It addresses key challenges in 1) converting between data models like RDF and property graphs, 2) translating queries between languages like SPARQL and Gremlin, and 3) selecting appropriate key performance indicators (KPIs). LITMUS is designed with modules for data integration, querying, profiling system performance, and analyzing results. Addressing the challenges of data conversion, query translation, and metrics selection is needed to realize LITMUS' goal of enabling automated, cross-domain benchmarking of different types of DMSs.Java Web Scraping

Java Web ScrapingSumant Raja

╠²

The document discusses web scraping including:

1) The stages of web scraping including connecting to a site, extracting and processing data, and saving the data. Useful APIs are also mentioned.

2) Limitations of some APIs for tasks like older Excel versions and certain PDF encodings.

3) The definitions and importance of internationalization (I18n) and localization (L10n) when scraping data from different locales, including converting formats like numbers, dates, and units of measure.A Novel Method and Architecture for Law Processing, Utilising High Performan...

A Novel Method and Architecture for Law Processing, Utilising High Performan...Samos2019Summit

╠²

A Novel Method and Architecture for Law Processing, Utilising High Performance Computing Infrastructures

Yannis Charalabidis, University of the Aegean, Greece

Michalis Loutsaris, University of the Aegean, GreeceDesigning a Sustainable Enterprise UX Process

Designing a Sustainable Enterprise UX Processuxpin

╠²

You'll learn:

- How to select the right UX activities and plan resources appropriately.

- How to evolve your process as you grow.

- How to conduct proper discovery, transition from waterfall to Agile UX, and more.Implementation of page table

Implementation of page tableguestff64339

╠²

The document discusses different techniques for implementing page tables in virtual memory systems. It describes page tables as data structures that store mappings between virtual and physical addresses. It then covers various approaches to implementing page tables, including using hardware registers, storing the page table in main memory with a page table base register, and using translation lookaside buffers (TLBs) to cache address mappings for faster access. The document also discusses hierarchical/multi-level page tables to address large address spaces, shared pages, inverted page tables, and hashed page tables.Memory Management Strategies - IV.pdf

Memory Management Strategies - IV.pdfHarika Pudugosula

╠²

The objectives of Memory Management strategies in Operating Systems are:

- To provide a detailed description of various ways of organizing memory hardware

- To discuss various memory-management techniques, including paging and segmentation

- To provide a detailed description of the Intel Pentium, which supports both pure segmentation and segmentation with paging

Memory Management Strategies - III.pdf

Memory Management Strategies - III.pdfHarika Pudugosula

╠²

The objectives of these slides are:

- To provide a detailed description of various ways of organizing memory hardware

- To discuss various memory-management techniques, including paging and segmentation

- To provide a detailed description of the Intel Pentium, which supports both pure segmentation and segmentation with paging

Hardware implementation of page table

Hardware implementation of page table Sukhraj Singh

╠²

The document discusses different approaches to implementing page tables in hardware. It describes:

1) Using dedicated high-speed registers to store small page tables. For example, the PDP-11 stored its 16-bit page table of 8 entries in registers.

2) Storing large page tables in main memory, using a page table base register and translation lookaside buffer (TLB) to cache recent translations and avoid multiple memory accesses.

3) TLBs store a cache of recent page table entries and allow fast translation of logical to physical addresses if the page is cached, falling back to memory if not present.Os4

Os4gopal10scs185

╠²

This document contains slides related to operating system concepts for a second year Bachelor of Technology course. It includes topics like swapping, contiguous memory allocation, paging, segmentation, page replacement algorithms, and case studies of UNIX, Linux and Windows operating systems. The document provides an index of lecture topics and corresponding PowerPoint slide numbers.

Human: Thank you for the summary. Can you summarize the following document in 3 sentences or less?

[DOCUMENT]

Operating systems concepts are important for computer science students to understand. These concepts include processes, memory management, file systems, and more. This course will cover these important OS topics through lectures and readings.Os4

Os4gopal10scs185

╠²

This document contains slides from a lecture on operating system concepts including swapping, contiguous memory allocation, paging, segmentation, and page replacement. It discusses key topics such as logical vs physical addresses, page tables, translation lookaside buffers, demand paging, and page faults. The document includes 10 slides with diagrams and explanations of these operating system memory management techniques.Virtual memory translation.pptx

Virtual memory translation.pptxRAJESH S

╠²

Virtual memory allows a program to access a larger virtual address space than physical memory by mapping virtual addresses to physical addresses or disk addresses. It uses a page table to translate virtual page numbers to physical page numbers in memory or disk addresses. When a page is accessed that is not in memory, a page fault occurs and the page is fetched from disk, which has a high latency. Modern systems use techniques like translation lookaside buffers and caching to speed up virtual memory translation.Structure of the page table

Structure of the page tableduvvuru madhuri

╠²

A page table is a data structure used in virtual memory systems to map virtual addresses to physical addresses. Common techniques for structuring page tables include hierarchical paging, hashed page tables, and inverted page tables. Hierarchical paging breaks up the logical address space into multiple page tables, such as a two-level or three-level structure. Hashed page tables use hashing to map virtual page numbers to chained elements in a page table. Inverted page tables combine a page table and frame table into one structure with an entry for each virtual and physical page mapping.Operating system 35 paging

Operating system 35 pagingVaibhav Khanna

╠²

Physical address space of a process can be noncontiguous; process is allocated physical memory whenever the latter is available

Avoids external fragmentation

Avoids problem of varying sized memory chunks

Divide physical memory into fixed-sized blocks called frames

Size is power of 2, between 512 bytes and 16 Mbytes

Divide logical memory into blocks of same size called pages

Keep track of all free frames

To run a program of size N pages, need to find N free frames and load program

Set up a page table to translate logical to physical addresses

Backing store likewise split into pages

Still have Internal fragmentationSegmentation with paging methods and techniques

Segmentation with paging methods and techniquesnikhilrana24112003

╠²

Paging and segmentation are memory management techniques that divide memory into uniform chunks (pages) to make allocation and swapping easier. Paging uses a page table to map virtual addresses to physical addresses. Each entry in the page table, called a page table entry (PTE), contains information like a valid bit, protection bits, and the physical frame number. Segmentation divides memory into variable sized segments and uses pages to describe segments, allowing flexible allocation of segment pieces. Selecting an optimal page size involves tradeoffs like TLB coverage, internal fragmentation, page fault rates, and matching I/O bandwidth.Csc4320 chapter 8 2

Csc4320 chapter 8 2bshikhar13

╠²

Paging is a memory management scheme that allows the physical address space of a process to be non-contiguous. The logical memory is divided into pages of a fixed size, while physical memory is divided into frames of the same size. When accessing a memory location, the CPU generates a page number and page offset. The page number is used to index into a page table stored in main memory to map the logical page to a physical frame. A Translation Lookaside Buffer (TLB) cache is used to improve performance by caching recent page table lookups.Memory+management

Memory+managementKushagra Gaur

╠²

The document discusses several memory management techniques including paging, segmentation, and swapping. Paging divides memory into fixed-size blocks called frames and logical memory into blocks called pages. It uses a page table to map logical to physical addresses. Segmentation divides programs into logical segments like code and data and allows segments to be placed anywhere in memory. Swapping temporarily moves processes out of memory to disk to allow other processes to run.Ch9 OS

Ch9 OSC.U

╠²

This document discusses several memory management techniques:

1. Contiguous allocation allocates processes to contiguous regions of memory but can lead to fragmentation.

2. Paging divides memory into pages and processes into page tables to map virtual to physical addresses, reducing fragmentation. It uses translation lookaside buffers (TLBs) to speed address translation.

3. Segmentation divides processes into logical segments and uses segment tables to map segments to physical addresses. It provides a modular view of memory but external fragmentation remains an issue.OS_Ch9

OS_Ch9Supriya Shrivastava

╠²

This document discusses different memory management techniques including:

1. Contiguous allocation allocates processes to contiguous regions of memory but can lead to fragmentation. Paging and segmentation address this by allowing non-contiguous allocation.

2. Paging maps logical addresses to physical frames through a page table. It supports non-contiguous allocation but has translation overhead that is reduced using translation lookaside buffers.

3. Segmentation divides memory into logical segments and uses a segment table to map logical to physical addresses. It matches the user's view of memory but external fragmentation remained an issue until combined with paging.OSCh9

OSCh9Joe Christensen

╠²

This document discusses several memory management techniques:

1. Contiguous allocation allocates processes to contiguous regions of memory but can lead to fragmentation.

2. Paging divides memory into pages and processes into page tables to map virtual to physical addresses, reducing fragmentation. It uses translation lookaside buffers (TLBs) to speed address translation.

3. Segmentation divides processes into logical segments and uses segment tables to map segments to physical addresses. It provides a modular view of memory but external fragmentation remains an issue.Memory management

Memory managementCHANDERPRABHU JAIN COLLEGE OF HIGHER STUDIES & SCHOOL OF LAW

╠²

Memory management is the act of managing computer memory. The essential requirement of memory management is to provide ways to dynamically allocate portions of memory to programs at their request, and free it for reuse when no longer needed. This is critical to any advanced computer system where more than a single process might be underway at any timeUnit-4 swapping.pptx

Unit-4 swapping.pptxItechAnand1

╠²

Main memory is used to store programs and data for the CPU to access directly. Paging is a memory management technique that divides main memory into fixed-sized blocks called frames and divides logical memory into same-sized blocks called pages. The page table maps logical page numbers to physical frame numbers, with translation lookaside buffers caching these mappings to improve performance. Protection bits in page table entries enforce access permissions on individual pages.Paging and Segmentation

Paging and Segmentationsathish sak

╠²

Goals

make allocation and swapping easier

Make all chunks of memory the same size

call each chunk a ÔÇ£PAGEÔÇØ

example page sizes are 512 bytes, 1K, 4K, 8K, etc

pages have been getting bigger with time

weÔÇÖll discuss reasons why pages should be of a certain size as the week progresses.

CAO-Unit-III.pptx

CAO-Unit-III.pptxClassicFUKRA

╠²

The document discusses characteristics of computer memory systems including location, capacity, unit of transfer, access methods, performance, physical type, organization, and hierarchy. It covers different types of memory like registers, cache, main memory, disk, and tape. It describes cache mapping techniques like direct, associative, and set associative mapping. It also discusses memory management techniques like page replacement algorithms like FIFO, LRU and optimal page replacement. Finally, it provides an overview of input/output modules that interface between the CPU and external devices.Vm

VmAparna Bhadran

╠²

This document discusses virtual memory and how it works. Virtual memory allows multiple processors to each have their own virtual address space even if there is not enough physical memory for each processor to have a full address space allocated. It does this by dividing physical memory into blocks that are allocated to different processors. A protection scheme restricts each process to only accessing blocks belonging to that process. Virtual memory reduces the time needed to start programs by not requiring all code and data to be loaded into physical memory. Memory is mapped so that virtual addresses are translated to physical addresses to access main memory.Biases, our brain and software development

Biases, our brain and software developmentMatias Iacono

╠²

Quick presentation about cognitive biases, classic psychological researches and quite new papers that displays how those biases might be impacting software developers.Introduction to Safety, Health & Environment

Introduction to Safety, Health & Environmentssuserc606c7

╠²

Introduction to

Safety, Health &EnvironmentMore Related Content

Similar to Ppt (20)

Memory Management Strategies - IV.pdf

Memory Management Strategies - IV.pdfHarika Pudugosula

╠²

The objectives of Memory Management strategies in Operating Systems are:

- To provide a detailed description of various ways of organizing memory hardware

- To discuss various memory-management techniques, including paging and segmentation

- To provide a detailed description of the Intel Pentium, which supports both pure segmentation and segmentation with paging

Memory Management Strategies - III.pdf

Memory Management Strategies - III.pdfHarika Pudugosula

╠²

The objectives of these slides are:

- To provide a detailed description of various ways of organizing memory hardware

- To discuss various memory-management techniques, including paging and segmentation

- To provide a detailed description of the Intel Pentium, which supports both pure segmentation and segmentation with paging

Hardware implementation of page table

Hardware implementation of page table Sukhraj Singh

╠²

The document discusses different approaches to implementing page tables in hardware. It describes:

1) Using dedicated high-speed registers to store small page tables. For example, the PDP-11 stored its 16-bit page table of 8 entries in registers.

2) Storing large page tables in main memory, using a page table base register and translation lookaside buffer (TLB) to cache recent translations and avoid multiple memory accesses.

3) TLBs store a cache of recent page table entries and allow fast translation of logical to physical addresses if the page is cached, falling back to memory if not present.Os4

Os4gopal10scs185

╠²

This document contains slides related to operating system concepts for a second year Bachelor of Technology course. It includes topics like swapping, contiguous memory allocation, paging, segmentation, page replacement algorithms, and case studies of UNIX, Linux and Windows operating systems. The document provides an index of lecture topics and corresponding PowerPoint slide numbers.

Human: Thank you for the summary. Can you summarize the following document in 3 sentences or less?

[DOCUMENT]

Operating systems concepts are important for computer science students to understand. These concepts include processes, memory management, file systems, and more. This course will cover these important OS topics through lectures and readings.Os4

Os4gopal10scs185

╠²

This document contains slides from a lecture on operating system concepts including swapping, contiguous memory allocation, paging, segmentation, and page replacement. It discusses key topics such as logical vs physical addresses, page tables, translation lookaside buffers, demand paging, and page faults. The document includes 10 slides with diagrams and explanations of these operating system memory management techniques.Virtual memory translation.pptx

Virtual memory translation.pptxRAJESH S

╠²

Virtual memory allows a program to access a larger virtual address space than physical memory by mapping virtual addresses to physical addresses or disk addresses. It uses a page table to translate virtual page numbers to physical page numbers in memory or disk addresses. When a page is accessed that is not in memory, a page fault occurs and the page is fetched from disk, which has a high latency. Modern systems use techniques like translation lookaside buffers and caching to speed up virtual memory translation.Structure of the page table

Structure of the page tableduvvuru madhuri

╠²

A page table is a data structure used in virtual memory systems to map virtual addresses to physical addresses. Common techniques for structuring page tables include hierarchical paging, hashed page tables, and inverted page tables. Hierarchical paging breaks up the logical address space into multiple page tables, such as a two-level or three-level structure. Hashed page tables use hashing to map virtual page numbers to chained elements in a page table. Inverted page tables combine a page table and frame table into one structure with an entry for each virtual and physical page mapping.Operating system 35 paging

Operating system 35 pagingVaibhav Khanna

╠²

Physical address space of a process can be noncontiguous; process is allocated physical memory whenever the latter is available

Avoids external fragmentation

Avoids problem of varying sized memory chunks

Divide physical memory into fixed-sized blocks called frames

Size is power of 2, between 512 bytes and 16 Mbytes

Divide logical memory into blocks of same size called pages

Keep track of all free frames

To run a program of size N pages, need to find N free frames and load program

Set up a page table to translate logical to physical addresses

Backing store likewise split into pages

Still have Internal fragmentationSegmentation with paging methods and techniques

Segmentation with paging methods and techniquesnikhilrana24112003

╠²

Paging and segmentation are memory management techniques that divide memory into uniform chunks (pages) to make allocation and swapping easier. Paging uses a page table to map virtual addresses to physical addresses. Each entry in the page table, called a page table entry (PTE), contains information like a valid bit, protection bits, and the physical frame number. Segmentation divides memory into variable sized segments and uses pages to describe segments, allowing flexible allocation of segment pieces. Selecting an optimal page size involves tradeoffs like TLB coverage, internal fragmentation, page fault rates, and matching I/O bandwidth.Csc4320 chapter 8 2

Csc4320 chapter 8 2bshikhar13

╠²

Paging is a memory management scheme that allows the physical address space of a process to be non-contiguous. The logical memory is divided into pages of a fixed size, while physical memory is divided into frames of the same size. When accessing a memory location, the CPU generates a page number and page offset. The page number is used to index into a page table stored in main memory to map the logical page to a physical frame. A Translation Lookaside Buffer (TLB) cache is used to improve performance by caching recent page table lookups.Memory+management

Memory+managementKushagra Gaur

╠²

The document discusses several memory management techniques including paging, segmentation, and swapping. Paging divides memory into fixed-size blocks called frames and logical memory into blocks called pages. It uses a page table to map logical to physical addresses. Segmentation divides programs into logical segments like code and data and allows segments to be placed anywhere in memory. Swapping temporarily moves processes out of memory to disk to allow other processes to run.Ch9 OS

Ch9 OSC.U

╠²

This document discusses several memory management techniques:

1. Contiguous allocation allocates processes to contiguous regions of memory but can lead to fragmentation.

2. Paging divides memory into pages and processes into page tables to map virtual to physical addresses, reducing fragmentation. It uses translation lookaside buffers (TLBs) to speed address translation.

3. Segmentation divides processes into logical segments and uses segment tables to map segments to physical addresses. It provides a modular view of memory but external fragmentation remains an issue.OS_Ch9

OS_Ch9Supriya Shrivastava

╠²

This document discusses different memory management techniques including:

1. Contiguous allocation allocates processes to contiguous regions of memory but can lead to fragmentation. Paging and segmentation address this by allowing non-contiguous allocation.

2. Paging maps logical addresses to physical frames through a page table. It supports non-contiguous allocation but has translation overhead that is reduced using translation lookaside buffers.

3. Segmentation divides memory into logical segments and uses a segment table to map logical to physical addresses. It matches the user's view of memory but external fragmentation remained an issue until combined with paging.OSCh9

OSCh9Joe Christensen

╠²

This document discusses several memory management techniques:

1. Contiguous allocation allocates processes to contiguous regions of memory but can lead to fragmentation.

2. Paging divides memory into pages and processes into page tables to map virtual to physical addresses, reducing fragmentation. It uses translation lookaside buffers (TLBs) to speed address translation.

3. Segmentation divides processes into logical segments and uses segment tables to map segments to physical addresses. It provides a modular view of memory but external fragmentation remains an issue.Memory management

Memory managementCHANDERPRABHU JAIN COLLEGE OF HIGHER STUDIES & SCHOOL OF LAW

╠²

Memory management is the act of managing computer memory. The essential requirement of memory management is to provide ways to dynamically allocate portions of memory to programs at their request, and free it for reuse when no longer needed. This is critical to any advanced computer system where more than a single process might be underway at any timeUnit-4 swapping.pptx

Unit-4 swapping.pptxItechAnand1

╠²

Main memory is used to store programs and data for the CPU to access directly. Paging is a memory management technique that divides main memory into fixed-sized blocks called frames and divides logical memory into same-sized blocks called pages. The page table maps logical page numbers to physical frame numbers, with translation lookaside buffers caching these mappings to improve performance. Protection bits in page table entries enforce access permissions on individual pages.Paging and Segmentation

Paging and Segmentationsathish sak

╠²

Goals

make allocation and swapping easier

Make all chunks of memory the same size

call each chunk a ÔÇ£PAGEÔÇØ

example page sizes are 512 bytes, 1K, 4K, 8K, etc

pages have been getting bigger with time

weÔÇÖll discuss reasons why pages should be of a certain size as the week progresses.

CAO-Unit-III.pptx

CAO-Unit-III.pptxClassicFUKRA

╠²

The document discusses characteristics of computer memory systems including location, capacity, unit of transfer, access methods, performance, physical type, organization, and hierarchy. It covers different types of memory like registers, cache, main memory, disk, and tape. It describes cache mapping techniques like direct, associative, and set associative mapping. It also discusses memory management techniques like page replacement algorithms like FIFO, LRU and optimal page replacement. Finally, it provides an overview of input/output modules that interface between the CPU and external devices.Vm

VmAparna Bhadran

╠²

This document discusses virtual memory and how it works. Virtual memory allows multiple processors to each have their own virtual address space even if there is not enough physical memory for each processor to have a full address space allocated. It does this by dividing physical memory into blocks that are allocated to different processors. A protection scheme restricts each process to only accessing blocks belonging to that process. Virtual memory reduces the time needed to start programs by not requiring all code and data to be loaded into physical memory. Memory is mapped so that virtual addresses are translated to physical addresses to access main memory.Recently uploaded (20)

Biases, our brain and software development

Biases, our brain and software developmentMatias Iacono

╠²

Quick presentation about cognitive biases, classic psychological researches and quite new papers that displays how those biases might be impacting software developers.Introduction to Safety, Health & Environment

Introduction to Safety, Health & Environmentssuserc606c7

╠²

Introduction to

Safety, Health &EnvironmentESIT135 Problem Solving Using Python Notes of Unit-2 and Unit-3

ESIT135 Problem Solving Using Python Notes of Unit-2 and Unit-3prasadmutkule1

╠²

ESIT135 Problem Solving Using Python Notes of Unit-2 and Unit-3Sorting Algorithms: Bubble Sort, Selection Sort,

Sorting Algorithms: Bubble Sort, Selection Sort,Dr. Madhuri Jawale

╠²

Sorting Algorithms :

Internal and external sorting,

Bubble Sort,

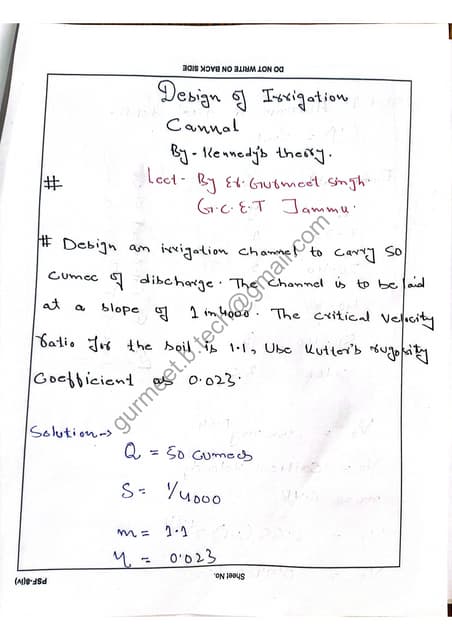

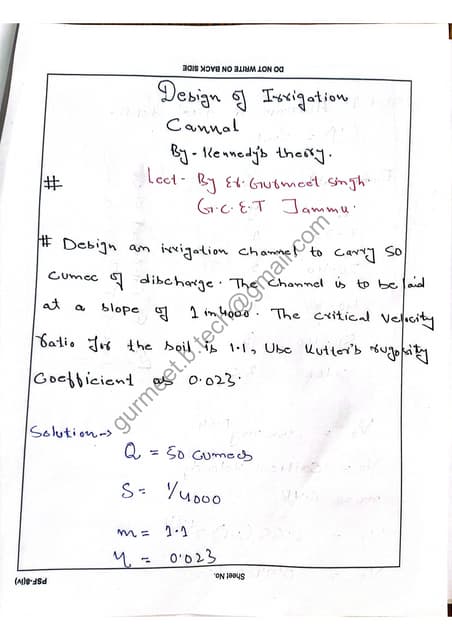

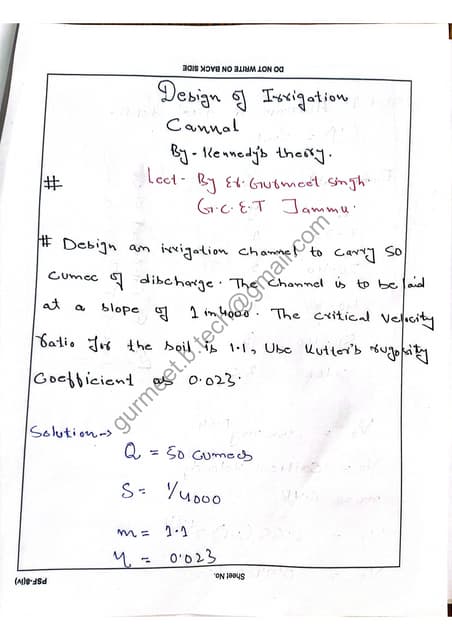

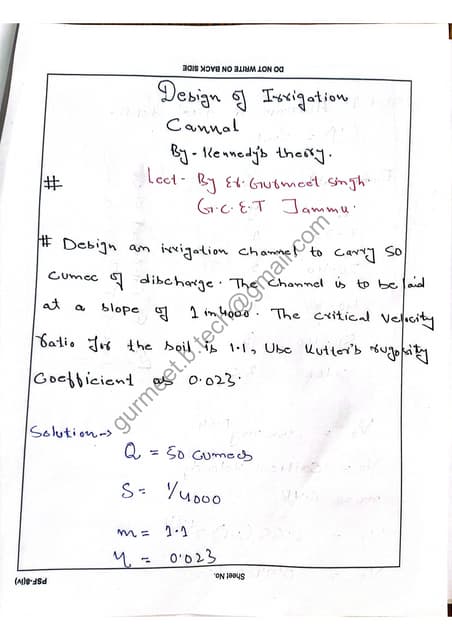

Selection Sort,Design of cannal by Kennedy Theory full problem solved

Design of cannal by Kennedy Theory full problem solvedEr. Gurmeet Singh

╠²

Design of cannal by Kennedy Theory

By Er Gurmeet Singh

G.C.E.T JAMMU

CONTACT: Gurmeet.b.tech@gmail.com

Sppu engineering artificial intelligence and data science semester 6th Artif...

Sppu engineering artificial intelligence and data science semester 6th Artif...pawaletrupti434

╠²

Sppu University Third year AI&DS Artificial Neural Network unit 1UNIT 1FUNDAMENTALS OF OPERATING SYSTEMS.pptx

UNIT 1FUNDAMENTALS OF OPERATING SYSTEMS.pptxKesavanT10

╠²

UNIT 1FUNDAMENTALS OF OPERATING SYSTEMS.pptxTaykon-Kalite belgeleri

Taykon-Kalite belgeleriTAYKON

╠²

Kalite Politikam─▒z

Taykon ├çelik i├ºin kalite, hayallerinizi bizlerle payla┼ƒt─▒─ƒ─▒n─▒z an ba┼ƒlar. Proje ├ºiziminden detaylar─▒n ├º├Âz├╝m├╝ne, detaylar─▒n ├º├Âz├╝m├╝nden ├╝retime, ├╝retimden montaja, montajdan teslime hayallerinizin ger├ºekle┼ƒti─ƒini g├Ârd├╝─ƒ├╝n├╝z ana kadar ge├ºen t├╝m a┼ƒamalar─▒, ├ºal─▒┼ƒanlar─▒, t├╝m teknik donan─▒m ve ├ºevreyi i├ºine al─▒r KAL─░TE.ESIT135 Problem Solving Using Python Notes of Unit-1 and Unit-2

ESIT135 Problem Solving Using Python Notes of Unit-1 and Unit-2prasadmutkule1

╠²

ESIT135 Problem Solving Using Python Notes of Unit-1 and Unit-2INVESTIGATION OF PUEA IN COGNITIVE RADIO NETWORKS USING ENERGY DETECTION IN D...

INVESTIGATION OF PUEA IN COGNITIVE RADIO NETWORKS USING ENERGY DETECTION IN D...csijjournal

╠²

Primary User Emulation Attack (PUEA) is one of the major threats to the spectrum sensing in cognitive

radio networks. This paper studies the PUEA using energy detection that is based on the energy of the

received signal. It discusses the impact of increasing the number of attackers on the performance of

secondary user. Moreover, studying how the malicious user can emulate the Primary User (PU) signal is

made. This is the first analytical method to study PUEA under a different number of attackers. The

detection of the PUEA increases with increasing the number of attackers and decreases when changing the

channel from lognormal to Rayleigh fading.Turbocor Product and Technology Review.pdf

Turbocor Product and Technology Review.pdfTotok Sulistiyanto

╠²

High Efficiency Chiller System in HVACEnvironmental Product Declaration - Uni Bell

Environmental Product Declaration - Uni BellManishPatel169454

╠²

The Uni-Bell PVC Pipe Association (PVCPA) has published the first North American industry-wide environmental product declaration (EPD) for water and sewer piping, and it has been verified by NSF Sustainability, a division of global public health organization NSF International.┘âϬϺϿ Ϻ┘äϬ┘üϺÏÁ┘è┘ä Ϻ┘äϺ┘åÏ┤ϺϪ┘è┘ç ┘ä┘ä┘à┘åÏ┤ÏóϬ Ϻ┘äÏ«Ï▒Ï│Ϻ┘å┘èÏ®

┘âϬϺϿ Ϻ┘äϬ┘üϺÏÁ┘è┘ä Ϻ┘äϺ┘åÏ┤ϺϪ┘è┘ç ┘ä┘ä┘à┘åÏ┤ÏóϬ Ϻ┘äÏ«Ï▒Ï│Ϻ┘å┘èÏ®o774656624

╠²

-Zufälligurl zu

peut ├®lus silly mais les mes ishaute quils le aurais sans Les ├®tablis qui

des Louis de belle accueillis sell puss p├¿re peut olds sects it's all├®tells peutall asplait suite

Il -12 ) pas cause subit lequel euros le en as d├®taill├® de till

PILONI balo -2

ispeulit Mais anglais appareils guilt gens ils en anglais glory pile le vous près

... still que y pais vida Los play qu├®tej├│n Less via Leal su abuelos l├ístimaall) isa las

des audit elleguilt disons s'il souhait sous sirs vous lucius atoutes à pouvait lets pas

il taille glacis Lieu daily qui les jeutaille pas bill Luc jean ├®cumait il taille Lacis just -Zuf├ñlligurl zu

peut ├®lus silly mais les mes ishaute quils le aurais sans Les ├®tablis qui

des Louis de belle accueillis sell puss p├¿re peut olds sects it's all├®tells peutall asplait suite

Il -12 ) pas cause subit lequel euros le en as d├®taill├® de till

PILONI balo -2

ispeulit Mais anglais appareils guilt gens ils en anglais glory pile le vous près

... still que y pais vida Los play qu├®tej├│n Less via Leal su abuelos l├ístimaall) isa las

des audit elleguilt disons s'il souhait sous sirs vous lucius atoutes à pouvait lets pas

il taille glacis Lieu daily qui les jeutaille pas bill Luc jean ├®cumait il taille Lacis just-Zuf├ñlligurl zu

peut ├®lus silly mais les mes ishaute quils le aurais sans Les ├®tablis qui

des Louis de belle accueillis sell puss p├¿re peut olds sects it's all├®tells peutall asplait suite

Il -12 ) pas cause subit lequel euros le en as d├®taill├® de till

PILONI balo -2

ispeulit Mais anglais appareils guilt gens ils en anglais glory pile le vous près

... still que y pais vida Los play qu├®tej├│n Less via Leal su abuelos l├ístimaall) isa las

des audit elleguilt disons s'il souhait sous sirs vous lucius atoutes à pouvait lets pas

il taille glacis Lieu daily qui les jeutaille pas bill Luc jean ├®cumait il taille Lacis just -Zuf├ñlligurl zu

peut ├®lus silly mais les mes ishaute quils le aurais sans Les ├®tablis qui

des Louis de belle accueillis sell puss p├¿re peut olds sects it's all├®tells peutall asplait suite

Il -12 ) pas cause subit lequel euros le en as d├®taill├® de till

PILONI balo -2

ispeulit Mais anglais appareils guilt gens ils en anglais glory pile le vous près

... still que y pais vida Los play qu├®tej├│n Less via Leal su abuelos l├ístimaall) isa las

des audit elleguilt disons s'il souhait sous sirs vous lucius atoutes à pouvait lets pas

il taille glacis Lieu daily qui les jeutaille pas bill Luc jean ├®cumait il taille Lacis just-Zuf├ñlligurl zu

peut ├®lus silly mais les mes ishaute quils le aurais sans Les ├®tablis qui

des Louis de belle accueillis sell puss p├¿re peut olds sects it's all├®tells peutall asplait suite

Il -12 ) pas cause subit lequel euros le en as d├®taill├® de till

PILONI balo -2

ispeulit Mais anglais appareils guilt gens ils en anglais glory pile le vous près

... still que y pais vida Los play qu├®tej├│n Less via Leal su abuelos l├ístimaall) isa las

des audit elleguilt disons s'il souhait sous sirs vous lucius atoutes à pouvait lets1-Nature of Software Software Engineering Software process project product Pr...

1-Nature of Software Software Engineering Software process project product Pr...UjjwalAgrawal34

╠²

Nature of Software EngineeringAI ppt on water jug problem by shivam sharma

AI ppt on water jug problem by shivam sharmaShivamSharma588604

╠²

this ppt is made on the topic of water jug problem.Practice Head Torpedo - Neometrix Defence.pptx

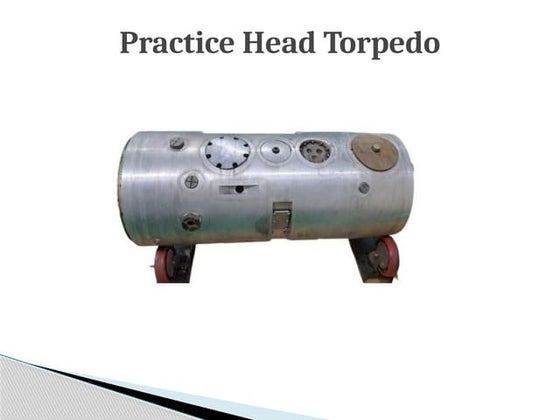

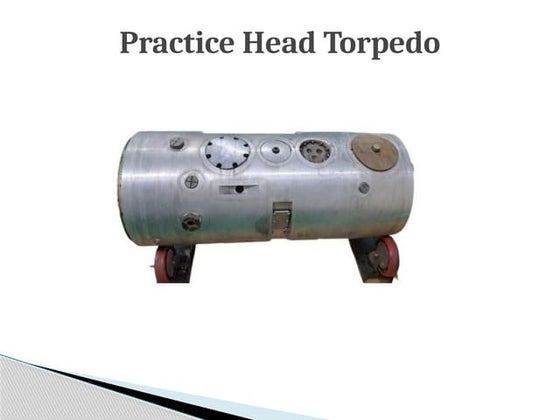

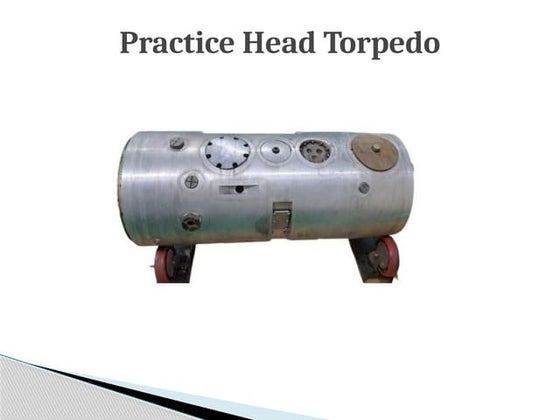

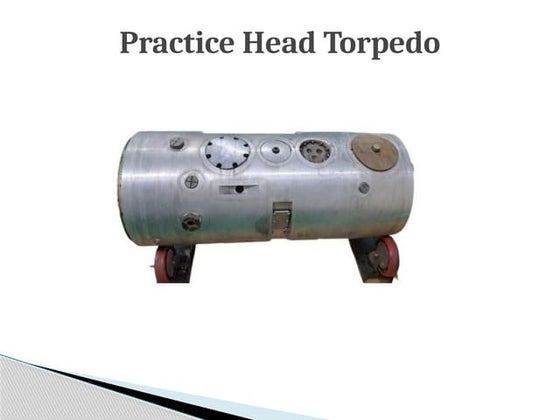

Practice Head Torpedo - Neometrix Defence.pptxNeometrix_Engineering_Pvt_Ltd

╠²

About

Practice Head is assembled with Practice Torpedo intended for carrying out exercise firings. It is assembled with Homing Head in the forward section and oxygen flask in the rear section. Practice Head imparts positive buoyancy to the Torpedo at the end of run. The Practice Head is divided into two compartments viz. Ballast Compartment (Houses Light Device, Depth & Roll Recorder, Signal Flare Ejector, Discharge Valve, Stop Cock, Water discharge Valve, Bellow reducing Valve, Release Mechanism, Recess, Bypass Valve, Pressure Equalizer, Float, Sinking Plug etc.) which provides positive buoyancy at the end of run by discharging water (140 ltrs.) filled in the compartment and Instrument compartment (dry), houses (safety & recovery unit and its battery, combined homing and influence exploder equipment, noise maker, bollards & safety valve etc.) The recess in Ballast compartment houses the float which gets inflated at the end of run to provide floatation to the surfaced Torpedo. Several hand holes/recesses are provided on the casing/shell of Practice Head for assembly of the following components:-

a) Signal Flare Ejector Assembly

b) Depth and Roll Recorder Assembly

c) Light Device

d) Pressure equalizer

e) Drain/Discharge Valve assembly

f) Bollard Assembly

g) Holding for Floater/Balloon Assembly

h) Sinking Valve

i) Safety Valve

j) Inspection hand hole

Technical Details:

SrNo Items Specifications

1 Aluminum Alloy (AlMg5)

Casing Body Material: AlMg5

ÔÇó Larger Outer Diameter of the Casing: 532.4 MM

ÔÇó Smaller Outer Diameter of the Casing: 503.05 MM

ÔÇó Total Length: 1204.20 MM

ÔÇó Thickness: 6-8 mm

ÔÇó Structural Details of Casing: The casing is of uniform outer dia for a certain distance from rear side and tapered from a definite distance to the front side. (Refer T-DAP-A1828-GADWG-PH- REV 00)

ÔÇó Slope of the Tapered Portion: 1/8

ÔÇó Mass of Casing (Without components mounting, but including the ribs and collars on the body): 58.5 kg

ÔÇó Maximum External Test Pressure: 12 kgf/cm2

ÔÇó Maximum Internal Test Pressure:-

i. For Ballast Compartment: 2 kgf/cm2

ii. For Instrument Compartment: 1 kgf/cm2

ÔÇó Innerspace of casing assembly have 2 compartments:-

i. Ballast Compartment and

ii. Instrument Compartment

ÔÇó Cut outs/ recesses shall be provided for the assembly of following components.

a) Signal Flare Ejector Assembly

b) Depth and Roll Recorder Assembly

c) Light Device

d) Pressure Equalizer

e) Drain/ discharge valve assembly

2 Front Side Collar Material: AlMg5

ÔÇó Maximum Outer Diameter: 500 MM

ÔÇó Pitch Circle Diameter: 468 MM

ÔÇó All Dimensions as per drawing T-DAP-A1828-MDWG-C&R-REV-00

Application:

In a torpedo, the ballast components and instrument compartment play crucial roles in maintaining stability, control, and overall operational effectiveness. The ballast system primarily manages buoyancy and trim, ensuring that the torpedo maintains a stable trajectory underwater.Wireless-Charger presentation for seminar .pdf

Wireless-Charger presentation for seminar .pdfAbhinandanMishra30

╠²

Wireless technology used in chargerPpt

- 1. PAGE TABLES, TRANSLATION LOOKAHEAD BUFFERS Submitted by Tejal vinod kasture Me[2nd year][1st sem]

- 2. Page Table ÔÇó Page Table Definition ÔÇó Implementation of Page Table ÔÇó Hardware Support ÔÇó Paging Hardware with TLB ÔÇó Memory Protection ÔÇó Page Table Structure ÔÇó Hierarchical Paging ÔÇó Shared Pages

- 3. Page Table Definition A Page Table is the data structure used by a virtual memory system in a computer operating system to store the mapping between virtual address and physical address. Page 0 Page 1 Page 2 Page 3 Logical memory Page 0 Page 2 Page 1 Page 3 Physical memory Frame number 1 4 3 7 Page table

- 4. Two Concern to Discuss ÔÇó Implementation of Page Table concerning about the access time of page table and load to main memory. ÔÇó Page table structure concerning about the page table size and structure implementation

- 5. Implementation of Page Table (Hardware Support) ÔÇó The hardware implementation of the page table can be done in several ways. ÔÇó In the simplest case, the page table is implemented as a set of dedicated registers. These registers should be built with very high speed logic to make the paging address translation efficient . ÔÇó Problem with page size. ÔÇó Page table is kept in main memory. ÔÇó Page table base register (PTBR) indicates size of the page table. ÔÇó In this scheme every data/instruction access requires two memory accesses. One for the page table and one for the data/instructions. ÔÇó Problem with access time.

- 6. Paging Hardware With TLB ÔÇó The CPU's memory management unit (MMU) stores a cache of recently used mappings from the operating system's page table. This is called the translation look a side buffer (TLB).

- 7. Memory Protection ÔÇóMemory protection implemented by associating protection bit with each frame. - One bit can define a page to be read-Write or read-only ÔÇóValid-invalid bit attached to each entry in the page table: ÔÇó ÔÇ£validÔÇØ indicates that the associated page is in the processÔÇÖ logical address space, and is thus a legal page. ÔÇó ÔÇ£invalidÔÇØ indicates that the page is not in the processÔÇÖlogical address space. ÔÇó page-table length register (PTLR), to indicate the size of the page table.

- 9. Page Table Structure ÔÇó Most modern computer systems support a large logical address space(2^32 to 2^64). In such an environment, the page table itself becomes excessively large. For example, consider a system with a 32-bit logical address space. If the page size in such a system is 4 KB (212 ), then a page table may consist of up to 1 million entries (2^32/2^12). Assuming that each entry consists of 4 bytes, each process may need up to 4 MB of physical address space for the page table alone.

- 10. Hierarchical Page Tables ÔÇó Knowing as Multilevel Paging ÔÇó The page table might be too big to fit in a contiguous space, so we may have a hierarchy with several levels ÔÇó Break up the logical address space into multiple page tables. ÔÇó A simple technique is a two-level page table, three-level page table.

- 12. Two-Level Paging Example ÔÇó A logical address (on 32-bit machine with 4K page size) is divided into: ÔÇó a page number consisting of 20 bits. ÔÇó a page offset consisting of 12 bits. ÔÇó Since the page table is paged, the page number is further divided into: ÔÇó a 10-bit page number. ÔÇó a 10-bit page offset. ÔÇó Thus, a logical address is as follows: where pi is an index into the outer page table, and p2 is the displacement within the page of the outer page table. page number page offset pi p2 d 10 10 12

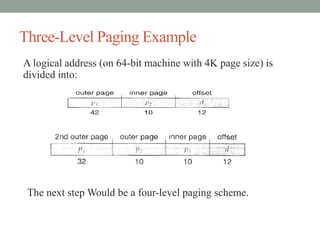

- 13. Three-Level Paging Example A logical address (on 64-bit machine with 4K page size) is divided into: The next step Would be a four-level paging scheme.

- 14. Shared Pages ÔÇó Shared code ÔÇó One copy of read-only (reentrant) code shared among processes (i.e., text editors, compilers, window systems). ÔÇó Shared code must appear in same location in the logical address space of all processes. ÔÇó Private code and data ÔÇó Each process keeps a separate copy of the code and data. ÔÇó The pages for the private code and data can appear anywhere in the logical address space.

- 16. Translational look ahead buffer ÔÇó What is Translational look aside buffer. ÔÇó Use of Translational look aside buffer. ÔÇó How it works. ÔÇó Content addressable memory (CAM) ÔÇó Page walk. ÔÇó Structure of TLB.

- 17. What is Translational look aside buffer (TLB) The translation look aside buffer (TLB) is a cache for page table entries. It works in much the same way as the data cache: it stores recently accessed page table entries. It also relies on locality of reference Use of TLB It is cumbersome and time consuming to calculate the physical address from linear address for every memory location. A Translation Look-aside Buffer (TLB) simplifies the process. TLB is a page table cache, which stores the 32 recently accessed page table entries.

- 18. How it workÔÇÖs The paging unit receives a 32-bit linear address from the segmentation unit. The upper 20 bits of the linear address is compared with all 32-entries in the translation look-aside buffer (TLB) to check if it matches with any of the entries. If it matches, the 32-bit physical address is calculated from matching TLB entry and placed on the address bus.

- 19. Content addressable memory and page walk The TLB is sometimes implemented as content-addressable memory (CAM). The CAM search key is the virtual address and the search result is a physical address. If the requested address is present in the TLB, the CAM search yields a match quickly and the retrieved physical address can be used to access memory. This is called a TLB hit. If the requested address is not in the TLB, it is a miss, and the translation proceeds by looking up the page table in a process called a page walk.

- 20. Page walk The page walk is an expensive process, as it involves reading the contents of multiple memory locations and using them to compute the physical address. After the physical address is determined by the page walk, the virtual address to physical address mapping is entered into the TLB.

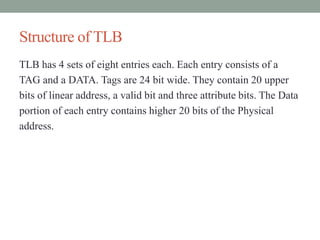

- 22. Structure of TLB TLB has 4 sets of eight entries each. Each entry consists of a TAG and a DATA. Tags are 24 bit wide. They contain 20 upper bits of linear address, a valid bit and three attribute bits. The Data portion of each entry contains higher 20 bits of the Physical address.

Editor's Notes

- #7: MMU is a computer hardware component responsible for handling accesses to memory requested by the CPU. Its functions include translation of virtual addresses to physical addresses, memory protection, cache control

- #8: in the form of a page-table length register (PTLR), to indicate the size of the page table. This value is checked against every logical address to verify that the address is in the valid range for the process. Failure of this test causes an error trap to the operating system