Son ?? ?? 1?

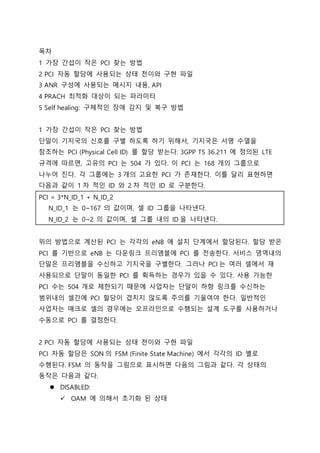

- 1. ?? 1 ?? ??? ?? PCI ?? ?? 2 PCI ?? ??? ???? ?? ??? ?? ?? 3 ANR ??? ???? ??? ??, API 4 PRACH ??? ??? ?? ???? 5 Self healing: ???? ?? ?? ? ?? ?? 1 ?? ??? ?? PCI ?? ?? ??? ???? ??? ?? ??? ?? ???, ???? ?? ??? ???? PCI (Physical Cell ID) ? ?? ???. 3GPP TS 36.211 ? ??? LTE ??? ???, ??? PCI ? 504 ? ??. ? PCI ? 168 ?? ???? ??? ??. ? ???? 3 ?? ??? PCI ? ????. ?? ?? ???? ??? ?? 1 ? ?? ID ? 2 ? ?? ID ? ????. PCI = 3*N_ID_1 + N_ID_2 N_ID_1 ? 0~167 ? ???, ? ID ??? ????. N_ID_2 ? 0~2 ? ???, ? ?? ?? ID ? ????. ?? ???? ??? PCI ? ??? eNB ? ?? ???? ????. ?? ?? PCI ? ???? eNB ? ???? ????? PCI ? ????. ??? ???? ??? ????? ???? ???? ????. ??? PCI ? ?? ??? ? ????? ??? ??? PCI ? ???? ??? ?? ? ??. ?? ??? PCI ?? 504 ?? ???? ??? ???? ??? ?? ??? ???? ???? ??? PCI ??? ??? ??? ??? ???? ??. ???? ???? ??? ?? ???? ?????? ???? ?? ??? ????? ???? PCI ? ????. 2 PCI ?? ??? ???? ?? ??? ?? ?? PCI ?? ??? SON ? FSM (Finite State Machine) ?? ??? ID ?? ????. FSM ? ??? ???? ???? ??? ??? ??. ? ??? ??? ??? ??. ? DISABLED: ? OAM ? ??? ??? ? ??

- 2. ? OAM ?? ?? ENBALE_DISABLE_REQ ? ??? ENABLE ? ??? ENABLE_IN_PROGRESS ??? ????. ? ENABLE_IN_PROGRESS: ? OAM ? ???? PCI ?? ??? ??? ?? ? NMM (Network Monitor Module) ? PCI ??? ???? ??? ????. ? PCI ?? ??? ??? REG ???? ?? PCI ? ?? ??? ???? ??? ???? DISABLE_IN_PROGRESS ??? ????. ? PCI ?? ??? ??? DEREG ???? ?? PCI ? ?? ??? ?? ?? ?? ??? ???? ENABLED ??? ????. ? ENABLED: ? ?? ??? PCI ? ???? ?? ? OAM ?? ?? RESELCTION_REQ ? ??? SEL_RESEL_IN_PROGRESS ??? ????. ? SEL_RESEL_IN_PROGRESS: ? PCI ? ? ???? ?? ? ??? ???? PCI ? ??? NMM ?? ?? ????. ? ??? ?? ??? ?? ?? DISABLE_IN_PROGRESS ??? ??. ? ??? ?? ??? ?? ?? ENABLED ??? ??.

- 3. ??? ??? ??? ??? ??? ?? ?? ??? ??? C ??? ?? ??? ?? ??? ??? ??. |-- Makefile : ?? ?? ?? ??? ?? ???? |-- include : C ???? ???? ??? ??? ?? ??? ?? ?? ?? | |-- son_apps_acf.h : NMM ??? ??? ?? ?? ?? | |-- son_apps_common_intf.h : ?? (NMM ? RRM) ? ?? ?????? ?? ?? ?? | |-- son_apps_fsm.h : FSM ? ?? ?? ?? | |-- son_apps_intf.h : ?? OAM ?????? ?? ?? ?? | `-- son_apps_pci.h : PCI ?? ?? ? ?? ??? ?? ?? ?? `-- src |-- son_apps_acf.c : NMM ??? ??? ?? C ?? ?? |-- son_apps_common_intf.c : ?? (NMM ? RRM) ? ?? ?????? ?? C ?? ?? |-- son_apps_fsm.c : FSM ? ?? C ?? ??

- 4. |-- son_apps_msg_handler.c : ?????? ???? ???? ??? ?? C ?? ?? `-- son_apps_pci.c : PCI ?? ?? ? ?? ??? ?? C ?? ?? 3 ANR ??? ???? ??? ??, API SONANR_ENABLE_REQ : OAM ? SON ?? ANR ? ??? ??? ?? ??? SONANR_DISABLE_REQ : OAM ? SON ?? ANR ? ? ??? ??? ?? ??? SONANR_NR_ADD_REQ : OAM ? SON ?? ?? ? ??? ????? ?? ??? SONANR_NR_DELETE_REQ : OAM ? SON ?? ?? ? ??? ????? ?? ??? SONANR_NR_UPDATE_REQ : OAM ? SON ?? ?? ? ?? ????? ?? ??? SONANR_NR_RETRIEVE_REQ : OAM ? SON ?? ?? ? ?? ???? ?? ??? SONANR_SON_MEAS_CONFIG_REQ : SON ? RRM ?? ANR ? ?? ??? ?? ??? ?? ??? SONANR_MODIFY_UE_COUNT_REQ : SON ? RRM ?? ANR ? ?? ??? ??? ?? ???? ?? ??? SONANR_MODIFY_MEAS_REPORTING_INTERVAL_REQ : SON ? RRM ?? ??? ?? ?? ??? ???? ?? ??? SONANR_NR_DELETE_FROM_REMOVE_LIST_REQ : ?? ?? ????? NR ?? ????? ???? ?? ??? SON_ANR_RRM_MEAS_CONFIG_OBJ_REMOVE_REQ : SON ? RRM ?? ?? ?? ??? ???? ?? ??? RRM_SON_CELL_STATE_CHANGE_IND : RRM ? SON ?? ? ??? ????? ??? ??? RRM_SON_MEAS_CONFIG_RESP : RRM ? SON ?? SONANR_SON_MEAS_CONFIG_REQ ? ?? ???

- 5. RRM_SON_MEAS_RESULTS_IND : RRM ? SON ?? SONANR_SON_MEAS_CONFIG_REQ ? ???? ?? ??? RRM_SON_HO_REPORT : RRM ? SON ?? ???? ??? ?? ??? ??? ???? ??? RRM_SON_HO_ATTEMPT : RRM ? SON ?? ????? ??? ?? ?? ???? ???? ??? RRM_SON_HO_FAILURE_REPORT : RRM ? SON ?? ????? ????? ???? ??? RRM_SON_MEAS_CONFIG_OBJ_REMOVE_RESP : RRM ? SON ?? SON_ANR_RRM_MEAS_CONFIG_OBJ_REMOVE_REQ ?? ??? ANR ??? ??? ??? ?? ?? ??? ??? C ??? ?? ??? ?? ??? ??? ??. |-- Makefile : ?? ?? ?? ??? ?? ???? |-- include : C ???? ???? ??? ??? ?? ??? ?? ?? ?? | |-- son_anr_ctxt_mgr.h : ANR ??? ??? ?? ?? ?? | |-- son_anr_fsm.h : FSM ? ?? ?? ?? | |-- son_anr_intf.h : ?? ?????? ?? ?? ?? | |-- son_anr_table.h : ANR hash table ? ?? ???? ?? ?? ?? | `-- son_anr_utils.h : ANR ????? ?? ?? ?? `-- src |-- son_anr_ctxt_mgr.c : ANR ??? ??? ?? C ?? ?? |-- son_anr_fsm.c : FSM ? ?? C ?? ?? |-- son_anr_msg_handler.c : ?????? ???? ???? ??? ?? C ?? ?? |-- son_anr_table.c : ANR hash table ? ?? ???? ?? C ?? ?? `-- son_anr_utils.c : ANR ????? ?? C ?? ?? ??: ANR ??? ?? ???? NMM (Network Monitor Mode) ? ??? ?? ??? ???? ??. |-- Makefile : ?? ?? ?? ??? ?? ????

- 6. |-- include : C ???? ???? ??? ??? ?? ??? ?? ?? ?? | |-- son_nmm.h : NMM ? ???? ??? ??? ?? | |-- son_nmm_fsm.h : NMM ? FSM ? ??? ?? ?? | |-- son_nmm_phy_api.h : NMM ? PHY ? API ?? ?? `-- src |-- son_nmm.c : NMM ??? ?? ??? ???? C ?? ?? |-- son_nmm_fsm.c : NMM ? FSM ??? ??? C ?? ?? |-- son_nmm_phy_api.c : NMM ? PHY ? ??? ???? C ?? ?? NMM ??? ?? ? ??? ?? PHY ? ?? ???? ??? ??? ???. ??? ??? ???? API ? ??? ??. - ??: son_phy_send_son_phy_rssi_meas_req ( ) - ????: son_phy_rssi_meas_req_t *p_son_phy_rssi_meas_req - ??: This function sends the rssi measurement request to phy. - ??: son_phy_send_son_phy_cell_search_req ( ) - ????: son_phy_cell_search_req_t *p_son_phy_cell_search_req - ??: This function sends the cell search request to phy. - ??: son_phy_send_son_phy_pbch_config_req ( ) - ????: son_phy_pbch_config_req_t *p_son_phy_pbch_config_req - ??: This function sends the pbch configuration request to phy. - ??: son_phy_send_son_phy_sib1_config_req ( ) - ????: son_phy_sib1_config_req_t *p_son_phy_sib1_config_req - ??: This function sends the sib1 configuration request to phy. - ??: son_phy_send_son_phy_bcch_config_req - ????: son_phy_bcch_config_req_t *p_son_phy_bcch_config_req - ??: This function sends the bcch configuration request to phy. - ??: son_phy_send_son_phy_stop_rssi_meas_req

- 7. - ????: son_phy_stop_rssi_meas_req_t *p_son_phy_stop_rssi_meas_req - ??: This function sends the stop rssi measurement request to phy. - ??: son_phy_send_son_phy_stop_cell_search_req - ????: son_phy_stop_cell_search_req_t *p_son_phy_stop_cell_search_req - ??: This function sends the stop cell search request to phy. - ??: son_phy_send_son_phy_stop_pbch_req - ????: son_phy_stop_pbch_req_t *p_son_phy_stop_pbch_req - ??: This function sends the stop pbch request to phy. - ??: son_phy_send_son_phy_stop_bcch_req - ????: son_phy_stop_bcch_req_t *p_son_phy_stop_bcch_req - ??: This function sends the stop bcch request to phy. ??: 4 Air sync ? Sniff ?? ANR ? ???? ??? ?????? ?? ??? ???? ??? HeNB ? Sniff ??? ???? ??? ??. ??? ?? ??? ???? ??? ???? ?? ?? ?? ? ??? ??? ? ?? ??? ???, ? ?? ??? ?? ??? ???? ??? ANR ? ??? ? ??. HeNB ? Sniff ??? ??? ??? Sniff ?? ? ?? ???? ???? ??? ???, ??? ? ?? ??? ?? ??? ???? ??? ANR ? ??? ? ??. ?? ??? PCI ?? ??? HeNB ? Sniff ? ??? ANR ??? ???? ???? ?????? ??? ?? ???? ?? ???? ??? ?? ??? ???? ??. ?? ???? ??? ???? ??? ?? ??? ??? ??? ??. 1. AIC_RX_FRAMER write received samples internal dual port SRAM buffer

- 8. 2. AIC_RX_DMA controller waits to accumulated received samples

- 9. 3. AIC_RX_DMA controller copies received samples to system memory

- 11. 3. CPU SW correlates received samples with expected PSS to get slot timing 4. CPU SW correlates received samples with expected SSS to get 10 ms frame timing

- 12. 5. CPU SW decodes MIB using convert_mib() in sib_decoder.c MIB ? ??? ??? ?? 40 ms ?? ????. 6. CPU SW get SFN, BW, cell ID info from MIB

- 13. MIB ? ??? ?? ??? ????. 7. CPU SW get SIB scheduling info from SIB 1 SIB 1 ? ??? ?? ?? SIB ? ???? ??? ??? ??. 8. CPU SW get RACH info from SIB 2 SIB 2 ? ??? ?? UL RACH ?? ??? ????. i) Access Barring Information - Access Probability factor, Access Class Baring List, Access Class Baring Time ii) Semi static Common Channel Configuration - Random Access Parameter, PRACH Configuration iii) UL frequency Information - UL EARFCN, UL Bandwidth, additional emmission iv) MBSFN Configuration

- 14. 7. CPU SW decides 1 s timing from SFN 8. CPU SW assert interrupt to 1PPS via GPIO to adjust timing for next operation 5 PRACH ??? ??? ?? ???? 3GPP 36.902 4.7 ? ??? RACH ??? ??? ?? ????? ??? ??. PRACH Configuration Index ??? PRACH ? ?? sub-frame ?? ?????? ???? ????? ??? ??? ??? ??. - access probability - access delay probability - PUSCH load PRACH Transmission Power Control Parameters ??? ?? ??? ?? ???? PRACH ? ?? ???? ???? ????? ??? ??? ??? ??. UL ??? ??? ?? ??? ?? ??? ????. - access probability

- 15. - access delay probability - uplink inter-cell interference RACH Backoff Parameter ??? RACH ?? ?? ? ?? ?? ? ??? ? ???? ???? ??? ??? ??? ??. - access probability - momentary RACH load RACH Preamble Split ??? ?? ???? ??? ???? ?? RACH ??? ????? ????. ? ?? ??? ??? ??? ??. - Handover failure at target cell - Handover failure timer T304 ? ?? ????? ??. Root Sequence Index RACH ???? ???? ?? ?????. ?? ??? ?? ?? ???? ?? ?? ???? ??. eNB ? X2 ?????? ??? ?? ?? ?? ??? ???? ??? ??. ? ?? ??? ??? ??? ???. - access probability - access delay probability RACH ??? ??? ??? ??? ?? ?? ??? ??? C ??? ?? ??? ?? ??? ??? ??. |-- Makefile : ?? ?? ?? ??? ?? ???? |-- include : C ???? ???? ??? ??? ?? ??? ?? ?? ?? | |-- son_rach_opt_ctxt_mgr.h : RACH ??? ??? ??? ?? ?? ?? | |-- son_rach_opt_fsm.h : FSM ? ?? ?? ?? | `-- son_rach_opt_intf.h : ?? ?????? ?? ?? ?? `-- src |-- son_rach_opt_ctxt_mgr.c : RACH ??? ??? ??? ?? C ?? ?? |-- son_rach_opt_fsm.c : FSM ? ?? C ?? ?? `-- son_rach_opt_msg_handler.c : ?????? ???? ???? ??? ?? C ?? ??

- 16. 6 Self healing: ???? ?? ?? ? ?? ?? ? ?? ??? ?? ? ?? ????? ???? ??? ???? ?? ?? ??? ??? ???? ????. eNB ? ??? ???? ???? ??? ?? ?? ???? eNB ????? ???? ???? ??? ?? ? ???. ?? ??? ??? ??? ?? ?? ??? ????? ??? ?? ??? ??. ?? ?? ?? ?? ??? ? ??? ?, ?, ?? ??? ???? ????. ? ??? ??? ??? ??? ??? ????. ???? ?? ???? ??? ??? ???? ???? ??? ??? ??. ? ??? ?? ?? (Cell Outage Detection), ?? ?? (Fault Management), ?? ?? (Cell Outage Compensation) ? ??? ???? ??. ?? ??? ??? ??. - ?? ??? ??? ?? - ???? ?? ?? ?? - ?? ?? ?? - ?? ???? ????? ???? ??? ? ??? ?? ?? ???? ??? ?? ??? ?? ???? ????. ?? ??? ???? ???? ??? ?? ?? ???? ?? ?? ??? ?? ??? ??? ??, ??? ???? ??? ??? ????. ?? ??? ??? ??. 1. ??? ???? ????. 2. ?? ??? ????. 3. ?? ?? ??? ????. 4. ?? ??? ??? ???? ????. 5. ? ??? ??? ??. 6. ? ??? ?? (Good -> Bad) ???? ????. 7. ?? ???? ??? ????. 8. ?? ???? ?? ???? ??? ? ??? ??. 9. ?? ?? ??? ???? ?? ?? ??. 10. ?? ?? ?? ??? ??? ??. 11. ?? ??? ?? (Bad -> Good) ???? ????.

- 17. 12. ?? ???? ??? ????. 13. ???? ??? ??? ?? 14. ?? ?? ??? ??? ???? ????. 15. ?? ??? ???? ????.