Subprograms in VHDL, Procedures in VHDL

- 1. ąÜčāą╗ą░ąĮąŠą▓ ąÆ.ąÉ. [v.kulanov@csn.khai.edu] ą¤ąŠą┤ą┐čĆąŠą│čĆą░ą╝ą╝čŗ. ą¤čĆąŠčåąĄą┤čāčĆčŗ ą▓ čÅąĘčŗą║ąĄ VHDL ┬½ąóąĄčģąĮąŠą╗ąŠą│ąĖąĖ ą┐čĆąŠąĄą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ ą║ąŠą╝ą┐čīčÄč鹥čĆąĮčŗčģ čüąĖčüč鹥ą╝┬╗

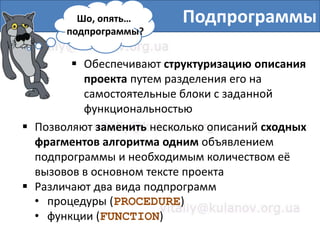

- 2. ą¤ąŠą┤ą┐čĆąŠą│čĆą░ą╝ą╝čŗą©ąŠ, ąŠą┐čÅčéčīŌĆ” ą┐ąŠą┤ą┐čĆąŠą│čĆą░ą╝ą╝čŗ? ’é¦ ą×ą▒ąĄčüą┐ąĄčćąĖą▓ą░čÄčé čüčéčĆčāą║čéčāčĆąĖąĘą░čåąĖčÄ ąŠą┐ąĖčüą░ąĮąĖčÅ ą┐čĆąŠąĄą║čéą░ ą┐čāč鹥ą╝ čĆą░ąĘą┤ąĄą╗ąĄąĮąĖčÅ ąĄą│ąŠ ąĮą░ čüą░ą╝ąŠčüč鹊čÅč鹥ą╗čīąĮčŗąĄ ą▒ą╗ąŠą║ąĖ čü ąĘą░ą┤ą░ąĮąĮąŠą╣ čäčāąĮą║čåąĖąŠąĮą░ą╗čīąĮąŠčüčéčīčÄ ’é¦ ą¤ąŠąĘą▓ąŠą╗čÅčÄčé ąĘą░ą╝ąĄąĮąĖčéčī ąĮąĄčüą║ąŠą╗čīą║ąŠ ąŠą┐ąĖčüą░ąĮąĖą╣ čüčģąŠą┤ąĮčŗčģ čäčĆą░ą│ą╝ąĄąĮč鹊ą▓ ą░ą╗ą│ąŠčĆąĖčéą╝ą░ ąŠą┤ąĮąĖą╝ ąŠą▒čŖčÅą▓ą╗ąĄąĮąĖąĄą╝ ą┐ąŠą┤ą┐čĆąŠą│čĆą░ą╝ą╝čŗ ąĖ ąĮąĄąŠą▒čģąŠą┤ąĖą╝čŗą╝ ą║ąŠą╗ąĖč湥čüčéą▓ąŠą╝ ąĄčæ ą▓čŗąĘąŠą▓ąŠą▓ ą▓ ąŠčüąĮąŠą▓ąĮąŠą╝ č鹥ą║čüč鹥 ą┐čĆąŠąĄą║čéą░ ’é¦ ąĀą░ąĘą╗ąĖčćą░čÄčé ą┤ą▓ą░ ą▓ąĖą┤ą░ ą┐ąŠą┤ą┐čĆąŠą│čĆą░ą╝ą╝ ŌĆó ą┐čĆąŠčåąĄą┤čāčĆčŗ (PROCEDURE) ŌĆó čäčāąĮą║čåąĖąĖ (FUNCTION)

- 3. ą¤čĆąŠčåąĄą┤čāčĆčŗ ą▓ VHDL PROCEDURE name[(parameter_interface_list)] IS {subprogram_declarative_item} BEGIN {sequential_statement} END [PROCEDURE] [name]; SIGNAL, TYPE, FILE, SUBTYPE, PROCEDURE, FUNCTION, VARIABLE, COMPONENT, CONSTANT ...-- ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗąĄ ąŠą┐ąĄčĆą░č鹊čĆčŗ a := 5 FOR ŌĆ” LOOP ŌĆ” END LOOP; ... IF ŌĆ” THEN ŌĆ” ELSE ŌĆ” END IF; ąśą╝čÅ ą┐čĆąŠčåąĄą┤čāčĆčŗ ąĪą┐ąĖčüąŠą║ č乊čĆą╝ą░ą╗čīąĮčŗčģ ą┐ą░čĆą░ą╝ąĄčéčĆąŠą▓ (ą╝ąŠąČąĄčé ąŠčéčüčāčéčüčéą▓ąŠą▓ą░čéčī)

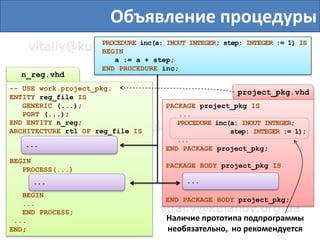

- 4. project_pkg.vhd n_reg.vhd ą×ą▒čŖčÅą▓ą╗ąĄąĮąĖąĄ ą┐čĆąŠčåąĄą┤čāčĆčŗ -- USE work.project_pkg; ENTITY reg_file IS GENERIC (...); PORT (...); END ENTITY n_reg; ARCHITECTURE rtl OF reg_file IS BEGIN PROCESS(...) BEGIN ... END PROCESS; ... END; PROCEDURE inc(a: INOUT INTEGER; step: INTEGER := 1) IS BEGIN a := a + step; END PROCEDURE inc; ... PACKAGE project_pkg IS ... PROCEDURE inc(a: INOUT INTEGER; step: INTEGER := 1); ... END PACKAGE project_pkg; PACKAGE BODY project_pkg IS END PACKAGE BODY project_pkg; ... ... ąØą░ą╗ąĖčćąĖąĄ ą┐čĆąŠč鹊čéąĖą┐ą░ ą┐ąŠą┤ą┐čĆąŠą│čĆą░ą╝ą╝čŗ ąĮąĄąŠą▒čÅąĘą░č鹥ą╗čīąĮąŠ, ąĮąŠ čĆąĄą║ąŠą╝ąĄąĮą┤čāąĄčéčüčÅ

- 5. ąĪą┐ąĖčüąŠą║ ą┐ą░čĆą░ą╝ąĄčéčĆąŠą▓ ą┐čĆąŠčåąĄą┤čāčĆčŗ PROCEDURE name[(parameter_interface_list)] IS ... ([CONSTANT|VARIABLE|SIGNAL] identifier {,ŌĆ”}: [IN|OUT|INOUT] type_indication [:= expression] {;ŌĆ”}) ąśą╝čÅ/ąśą┤ąĄąĮčéąĖčäąĖą║ą░č鹊čĆ ą┐ą░čĆą░ą╝ąĄčéčĆą░ ąÜą╗ą░čüčü ą┐ą░čĆą░ą╝ąĄčéčĆą░ (ą╝ąŠąČąĄčé ą▒čŗčéčī ąĄčēąĄ FILE) ąÆąĖą┤ ą┐ą░čĆą░ą╝ąĄčéčĆą░ ąóąĖą┐ ą┐ą░čĆą░ą╝ąĄčéčĆą░ ąŚąĮą░č湥ąĮąĖąĄ ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ. ą£ąŠąČąĄčé ą▒čŗčéčī ąĘą░ą┤ą░ąĮąŠ č鹊ą╗čīą║ąŠ ą┤ą╗čÅ ą┐ą░čĆą░ą╝ąĄčéčĆąŠą▓ ą║ą╗ą░čüčüą░ CONSTANT ąĖ VARIABLE PROCEDURE foo(val: INTEGER) -- val - CONSTANT PROCEDURE foo(val: IN INTEGER) -- val - CONSTANT PROCEDURE foo(val, bar: OUT INTEGER) -- val, bar - VARIABLE PROCEDURE foo(val: INOUT INTEGER) -- val ŌĆō VARIABLE

- 6. ąÆčŗąĘąŠą▓ ą┐čĆąŠčåąĄą┤čāčĆčŗ ą▓ VHDL ’é¦ ąÆčŗąĘąŠą▓ ą┐čĆąŠčåąĄą┤čāčĆčŗ ąĘą░ą┐ąĖčüčŗą▓ą░ąĄčéčüčÅ ą▓ ąĖčüčģąŠą┤ąĮąŠą╝ ą║ąŠą┤ąĄ ą║ą░ą║ ąŠčéą┤ąĄą╗čīąĮčŗą╣ ąŠą┐ąĄčĆą░č鹊čĆ, ą║ąŠč鹊čĆčŗą╣ ąĖą╝ąĄąĄčé čüą╗ąĄą┤čāčÄčēąĖą╣ čüąĖąĮčéą░ą║čüąĖčü: [label:] name [(parameter_list)]; ą£ąĄčéą║ą░ ąĪą┐ąĖčüąŠą║ čäą░ą║čéąĖč湥čüą║ąĖčģ ą┐ą░čĆą░ą╝ąĄčéčĆąŠą▓ ([parameter_name =>] expression|signal_name|variable_name|OPEN, {ŌĆ”}) ążąŠčĆą╝ą░ą╗čīąĮčŗą╣ ą┐ą░čĆą░ą╝ąĄčéčĆ ąöą▓ą░ čéąĖą┐ą░ čüąŠą┐ąŠčüčéą░ą▓ą╗ąĄąĮąĖčÅ: ’é¦ ąśą╝ąĄąĮąŠą▓ą░ąĮąĮąŠąĄ (=>) ’é¦ ą¤ąŠąĘąĖčåąĖąŠąĮąĮąŠąĄ ążą░ą║čéąĖč湥čüą║ąĖą╣ ą┐ą░čĆą░ą╝ąĄčéčĆ ’é¦ ąÆčŗčĆą░ąČąĄąĮąĖąĄ/ąÜąŠąĮčüčéą░ąĮčéąĮąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ ’é¦ ąĪąĖą│ąĮą░ą╗ ’é¦ ą¤ąĄčĆąĄą╝ąĄąĮąĮą░čÅ ’é¦ ąÜą╗čÄč湥ą▓ąŠąĄ čüą╗ąŠą▓ąŠ OPEN - ąĮąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ąĖą╗ąĖ ąĘąĮą░č湥ąĮąĖąĄ ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ

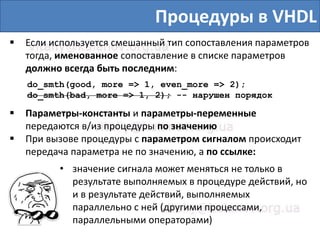

- 7. ą¤čĆąŠčåąĄą┤čāčĆčŗ ą▓ VHDL ’é¦ ąĢčüą╗ąĖ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ čüą╝ąĄčłą░ąĮąĮčŗą╣ čéąĖą┐ čüąŠą┐ąŠčüčéą░ą▓ą╗ąĄąĮąĖčÅ ą┐ą░čĆą░ą╝ąĄčéčĆąŠą▓ č鹊ą│ą┤ą░, ąĖą╝ąĄąĮąŠą▓ą░ąĮąĮąŠąĄ čüąŠą┐ąŠčüčéą░ą▓ą╗ąĄąĮąĖąĄ ą▓ čüą┐ąĖčüą║ąĄ ą┐ą░čĆą░ą╝ąĄčéčĆąŠą▓ ą┤ąŠą╗ąČąĮąŠ ą▓čüąĄą│ą┤ą░ ą▒čŗčéčī ą┐ąŠčüą╗ąĄą┤ąĮąĖą╝: do_smth(good, more => 1, even_more => 2); do_smth(bad, more => 1, 2); -- ąĮą░čĆčāčłąĄąĮ ą┐ąŠčĆčÅą┤ąŠą║ ’é¦ ą¤ą░čĆą░ą╝ąĄčéčĆčŗ-ą║ąŠąĮčüčéą░ąĮčéčŗ ąĖ ą┐ą░čĆą░ą╝ąĄčéčĆčŗ-ą┐ąĄčĆąĄą╝ąĄąĮąĮčŗąĄ ą┐ąĄčĆąĄą┤ą░čÄčéčüčÅ ą▓/ąĖąĘ ą┐čĆąŠčåąĄą┤čāčĆčŗ ą┐ąŠ ąĘąĮą░č湥ąĮąĖčÄ ’é¦ ą¤čĆąĖ ą▓čŗąĘąŠą▓ąĄ ą┐čĆąŠčåąĄą┤čāčĆčŗ čü ą┐ą░čĆą░ą╝ąĄčéčĆąŠą╝ čüąĖą│ąĮą░ą╗ąŠą╝ ą┐čĆąŠąĖčüčģąŠą┤ąĖčé ą┐ąĄčĆąĄą┤ą░čćą░ ą┐ą░čĆą░ą╝ąĄčéčĆą░ ąĮąĄ ą┐ąŠ ąĘąĮą░č湥ąĮąĖčÄ, ą░ ą┐ąŠ čüčüčŗą╗ą║ąĄ: ŌĆó ąĘąĮą░č湥ąĮąĖąĄ čüąĖą│ąĮą░ą╗ą░ ą╝ąŠąČąĄčé ą╝ąĄąĮčÅčéčīčüčÅ ąĮąĄ č鹊ą╗čīą║ąŠ ą▓ čĆąĄąĘčāą╗čīčéą░č鹥 ą▓čŗą┐ąŠą╗ąĮčÅąĄą╝čŗčģ ą▓ ą┐čĆąŠčåąĄą┤čāčĆąĄ ą┤ąĄą╣čüčéą▓ąĖą╣, ąĮąŠ ąĖ ą▓ čĆąĄąĘčāą╗čīčéą░č鹥 ą┤ąĄą╣čüčéą▓ąĖą╣, ą▓čŗą┐ąŠą╗ąĮčÅąĄą╝čŗčģ ą┐ą░čĆą░ą╗ą╗ąĄą╗čīąĮąŠ čü ąĮąĄą╣ (ą┤čĆčāą│ąĖą╝ąĖ ą┐čĆąŠčåąĄčüčüą░ą╝ąĖ, ą┐ą░čĆą░ą╗ą╗ąĄą╗čīąĮčŗą╝ąĖ ąŠą┐ąĄčĆą░č鹊čĆą░ą╝ąĖ)

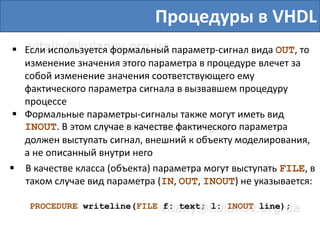

- 8. ą¤čĆąŠčåąĄą┤čāčĆčŗ ą▓ VHDL ’é¦ ąĢčüą╗ąĖ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ č乊čĆą╝ą░ą╗čīąĮčŗą╣ ą┐ą░čĆą░ą╝ąĄčéčĆ-čüąĖą│ąĮą░ą╗ ą▓ąĖą┤ą░ OUT, č鹊 ąĖąĘą╝ąĄąĮąĄąĮąĖąĄ ąĘąĮą░č湥ąĮąĖčÅ čŹč鹊ą│ąŠ ą┐ą░čĆą░ą╝ąĄčéčĆą░ ą▓ ą┐čĆąŠčåąĄą┤čāčĆąĄ ą▓ą╗ąĄč湥čé ąĘą░ čüąŠą▒ąŠą╣ ąĖąĘą╝ąĄąĮąĄąĮąĖąĄ ąĘąĮą░č湥ąĮąĖčÅ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĄą│ąŠ ąĄą╝čā čäą░ą║čéąĖč湥čüą║ąŠą│ąŠ ą┐ą░čĆą░ą╝ąĄčéčĆą░ čüąĖą│ąĮą░ą╗ą░ ą▓ ą▓čŗąĘą▓ą░ą▓čłąĄą╝ ą┐čĆąŠčåąĄą┤čāčĆčā ą┐čĆąŠčåąĄčüčüąĄ ’é¦ ążąŠčĆą╝ą░ą╗čīąĮčŗąĄ ą┐ą░čĆą░ą╝ąĄčéčĆčŗ-čüąĖą│ąĮą░ą╗čŗ čéą░ą║ąČąĄ ą╝ąŠą│čāčé ąĖą╝ąĄčéčī ą▓ąĖą┤ INOUT. ąÆ čŹč鹊ą╝ čüą╗čāčćą░ąĄ ą▓ ą║ą░č湥čüčéą▓ąĄ čäą░ą║čéąĖč湥čüą║ąŠą│ąŠ ą┐ą░čĆą░ą╝ąĄčéčĆą░ ą┤ąŠą╗ąČąĄąĮ ą▓čŗčüčéčāą┐ą░čéčī čüąĖą│ąĮą░ą╗, ą▓ąĮąĄčłąĮąĖą╣ ą║ ąŠą▒čŖąĄą║čéčā ą╝ąŠą┤ąĄą╗ąĖčĆąŠą▓ą░ąĮąĖčÅ, ą░ ąĮąĄ ąŠą┐ąĖčüą░ąĮąĮčŗą╣ ą▓ąĮčāčéčĆąĖ ąĮąĄą│ąŠ ’é¦ ąÆ ą║ą░č湥čüčéą▓ąĄ ą║ą╗ą░čüčüą░ (ąŠą▒čŖąĄą║čéą░) ą┐ą░čĆą░ą╝ąĄčéčĆą░ ą╝ąŠą│čāčé ą▓čŗčüčéčāą┐ą░čéčī FILE, ą▓ čéą░ą║ąŠą╝ čüą╗čāčćą░ąĄ ą▓ąĖą┤ ą┐ą░čĆą░ą╝ąĄčéčĆą░ (IN, OUT, INOUT) ąĮąĄ čāą║ą░ąĘčŗą▓ą░ąĄčéčüčÅ: PROCEDURE writeline(FILE f: text; l: INOUT line);

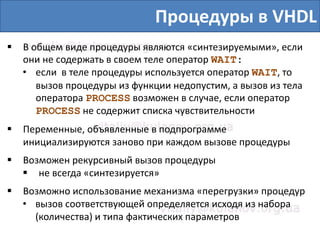

- 9. ą¤čĆąŠčåąĄą┤čāčĆčŗ ą▓ VHDL ’é¦ ąÆ ąŠą▒čēąĄą╝ ą▓ąĖą┤ąĄ ą┐čĆąŠčåąĄą┤čāčĆčŗ čÅą▓ą╗čÅčÄčéčüčÅ ┬½čüąĖąĮč鹥ąĘąĖčĆčāąĄą╝čŗą╝ąĖ┬╗, ąĄčüą╗ąĖ ąŠąĮąĖ ąĮąĄ čüąŠą┤ąĄčƹȹ░čéčī ą▓ čüą▓ąŠąĄą╝ č鹥ą╗ąĄ ąŠą┐ąĄčĆą░č鹊čĆ WAIT: ŌĆó ąĄčüą╗ąĖ ą▓ č鹥ą╗ąĄ ą┐čĆąŠčåąĄą┤čāčĆčŗ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ąŠą┐ąĄčĆą░č鹊čĆ WAIT, č鹊 ą▓čŗąĘąŠą▓ ą┐čĆąŠčåąĄą┤čāčĆčŗ ąĖąĘ čäčāąĮą║čåąĖąĖ ąĮąĄą┤ąŠą┐čāčüčéąĖą╝, ą░ ą▓čŗąĘąŠą▓ ąĖąĘ č鹥ą╗ą░ ąŠą┐ąĄčĆą░č鹊čĆą░ PROCESS ą▓ąŠąĘą╝ąŠąČąĄąĮ ą▓ čüą╗čāčćą░ąĄ, ąĄčüą╗ąĖ ąŠą┐ąĄčĆą░č鹊čĆ PROCESS ąĮąĄ čüąŠą┤ąĄčƹȹĖčé čüą┐ąĖčüą║ą░ čćčāą▓čüčéą▓ąĖč鹥ą╗čīąĮąŠčüčéąĖ ’é¦ ą¤ąĄčĆąĄą╝ąĄąĮąĮčŗąĄ, ąŠą▒čŖčÅą▓ą╗ąĄąĮąĮčŗąĄ ą▓ ą┐ąŠą┤ą┐čĆąŠą│čĆą░ą╝ą╝ąĄ ąĖąĮąĖčåąĖą░ą╗ąĖąĘąĖčĆčāčÄčéčüčÅ ąĘą░ąĮąŠą▓ąŠ ą┐čĆąĖ ą║ą░ąČą┤ąŠą╝ ą▓čŗąĘąŠą▓ąĄ ą┐čĆąŠčåąĄą┤čāčĆčŗ ’é¦ ąÆąŠąĘą╝ąŠąČąĄąĮ čĆąĄą║čāčĆčüąĖą▓ąĮčŗą╣ ą▓čŗąĘąŠą▓ ą┐čĆąŠčåąĄą┤čāčĆčŗ ’é¦ ąĮąĄ ą▓čüąĄą│ą┤ą░ ┬½čüąĖąĮč鹥ąĘąĖčĆčāąĄčéčüčÅ┬╗ ’é¦ ąÆąŠąĘą╝ąŠąČąĮąŠ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄ ą╝ąĄčģą░ąĮąĖąĘą╝ą░ ┬½ą┐ąĄčĆąĄą│čĆčāąĘą║ąĖ┬╗ ą┐čĆąŠčåąĄą┤čāčĆ ŌĆó ą▓čŗąĘąŠą▓ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĄą╣ ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčéčüčÅ ąĖčüčģąŠą┤čÅ ąĖąĘ ąĮą░ą▒ąŠčĆą░ (ą║ąŠą╗ąĖč湥čüčéą▓ą░) ąĖ čéąĖą┐ą░ čäą░ą║čéąĖč湥čüą║ąĖčģ ą┐ą░čĆą░ą╝ąĄčéčĆąŠą▓

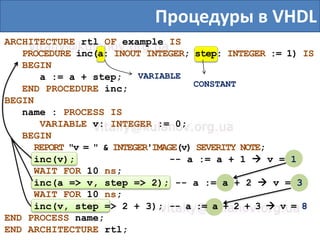

- 10. ą¤čĆąŠčåąĄą┤čāčĆčŗ ą▓ VHDL CONSTANT VARIABLE ARCHITECTURE rtl OF example IS PROCEDURE inc(a: INOUT INTEGER; step: INTEGER := 1) IS BEGIN a := a + step; END PROCEDURE inc; BEGIN name : PROCESS IS VARIABLE v: INTEGER := 0; BEGIN REPORT "v = " & INTEGER'IMAGE(v) SEVERITY NOTE; inc(v); -- a := a + 1 ’āĀ v = 1 WAIT FOR 10 ns; inc(a => v, step => 2); -- a := a + 2 ’āĀ v = 3 WAIT FOR 10 ns; inc(v, step => 2 + 3); -- a := a + 2 + 3 ’āĀ v = 8 END PROCESS name; END ARCHITECTURE rtl;

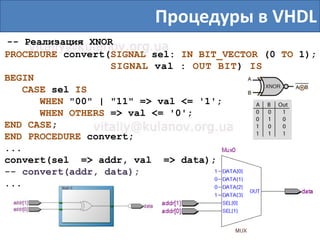

- 11. ą¤čĆąŠčåąĄą┤čāčĆčŗ ą▓ VHDL PROCEDURE convert(SIGNAL sel: IN BIT_VECTOR (0 TO 1); SIGNAL val : OUT BIT) IS BEGIN CASE sel IS WHEN "00" | "11" => val <= '1'; WHEN OTHERS => val <= '0'; END CASE; END PROCEDURE convert; ... convert(sel => addr, val => data); -- convert(addr, data); ... -- ąĀąĄą░ą╗ąĖąĘą░čåąĖčÅ XNOR

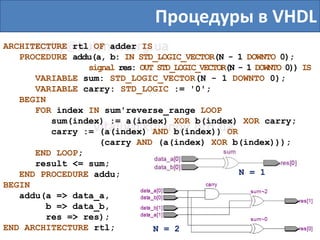

- 12. ą¤čĆąŠčåąĄą┤čāčĆčŗ ą▓ VHDL ARCHITECTURE rtl OF adder IS PROCEDURE addu(a, b: IN STD_LOGIC_VECTOR(N - 1 DOWNTO 0); signal res: OUT STD_LOGIC_VECTOR(N - 1 DOWNTO 0)) IS VARIABLE sum: STD_LOGIC_VECTOR(N - 1 DOWNTO 0); VARIABLE carry: STD_LOGIC := '0'; BEGIN FOR index IN sum'reverse_range LOOP sum(index) := a(index) XOR b(index) XOR carry; carry := (a(index) AND b(index)) OR (carry AND (a(index) XOR b(index))); END LOOP; result <= sum; END PROCEDURE addu; BEGIN addu(a => data_a, b => data_b, res => res); END ARCHITECTURE rtl; N = 1 N = 2

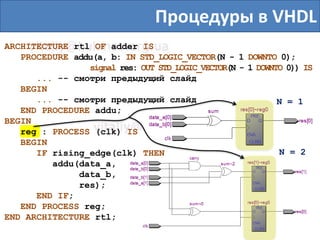

- 13. ą¤čĆąŠčåąĄą┤čāčĆčŗ ą▓ VHDL ARCHITECTURE rtl OF adder IS PROCEDURE addu(a, b: IN STD_LOGIC_VECTOR(N - 1 DOWNTO 0); signal res: OUT STD_LOGIC_VECTOR(N - 1 DOWNTO 0)) IS ... -- čüą╝ąŠčéčĆąĖ ą┐čĆąĄą┤čŗą┤čāčēąĖą╣ čüą╗ą░ą╣ą┤ BEGIN ... -- čüą╝ąŠčéčĆąĖ ą┐čĆąĄą┤čŗą┤čāčēąĖą╣ čüą╗ą░ą╣ą┤ END PROCEDURE addu; BEGIN reg : PROCESS (clk) IS BEGIN IF rising_edge(clk) THEN addu(data_a, data_b, res); END IF; END PROCESS reg; END ARCHITECTURE rtl; N = 1 N = 2

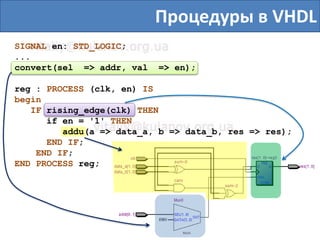

- 14. ą¤čĆąŠčåąĄą┤čāčĆčŗ ą▓ VHDL SIGNAL en: STD_LOGIC; ... convert(sel => addr, val => en); reg : PROCESS (clk, en) IS begin IF rising_edge(clk) THEN if en = '1' THEN addu(a => data_a, b => data_b, res => res); END IF; END IF; END PROCESS reg;

- 15. ą¤čĆąŠčåąĄą┤čāčĆčŗ ą▓ VHDL ’é¦ ąÆ č鹥ą╗ąĄ ą┐čĆąŠčåąĄą┤čāčĆčŗ ą╝ąŠąČąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ąŠą┐ąĄčĆą░č鹊čĆ RETURN, ąĮą░ąĘąĮą░č湥ąĮąĖąĄ ą║ąŠč鹊čĆąŠą│ąŠ ŌĆō ąĘą░ą▓ąĄčĆčłąĄąĮąĖąĄ ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖčÅ ą┐čĆąŠčåąĄą┤čāčĆčŗ: [label:] RETURN; PROCEDURE sort2(VARIABLE x1,x2: INOUT INTEGER) IS VARIABLE t: INTEGER; BEGIN IF x1 > x2 THEN RETURN; ELSE t := x1; x1 := x2; x2 := t; END IF; END PROCEDURE; ąÜą░ą║ čŹč鹊 čüą┤ąĄą╗ą░čéčī ą▒ąĄąĘ ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮąŠą╣ ą┐ąĄčĆąĄą╝ąĄąĮąĮąŠą╣ "t"?

- 16. ą¤ąĄčĆąĄą│čĆčāąĘą║ą░ ą┐čĆąŠčåąĄą┤čāčĆ -- ą┐čĆąŠč鹊čéąĖą┐čŗ ą┐čĆąŠčåąĄą┤čāčĆ inc PROCEDURE inc (a: INOUT word32; by: IN word32 := X"000_0001"); PROCEDURE inc (a: INOUT STD_LOGIC_VECTOR; by: IN STD_LOGIC_VECTOR := X"000_0001"); -- č乊čĆą╝ą░ą╗čīąĮčŗą╝ąĖ ą┐ą░čĆą░ą╝ąĄčéčĆą░ą╝ąĖ ą╝ąŠą│čāčé ą▓čŗčüčéčāą┐ą░čéčī ą╝ą░čüčüąĖą▓čŗ -- ąĮąĄąŠą│čĆą░ąĮąĖč湥ąĮąĮąŠą╣ ą┤ą╗ąĖąĮčŗ, ąĮąŠ ą┐čĆąĖ ą▓čŗąĘąŠą▓ąĄ ą┐čĆąŠčåąĄą┤čāčĆčŗ ą┤ą╗čÅ ąĮąĖčģ -- ą┤ąŠą╗ąČąĮčŗ ą▒čŗčéčī ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮčŗ čäą░ą║čéąĖč湥čüą║ąĖąĄ ąĘąĮą░č湥ąĮąĖąĄ ą▓ čüčéčĆąŠą│ąŠ -- ąŠą│čĆą░ąĮąĖč湥ąĮąĮąŠą╝ ą┤ąĖą░ą┐ą░ąĘąŠąĮąĄ PROCEDURE inc (a, b: IN STD_LOGIC_VECTOR; by: IN STD_LOGIC_VECTOR := X"000_0001"); PROCEDURE inc (a: INOUT INTEGER; by: IN INTEGER := 1); -- ą┐ąŠąĘąĖčåąĖąŠąĮąĮąŠąĄ čüąŠą┐ąŠčüčéą░ą▓ą╗ąĄąĮąĖąĄ, ą▓ ąĘą░ą▓ąĖčüąĖą╝ąŠčüčéąĖ ąŠčé čéąĖą┐ą░ -- ą┤ą░ąĮąĮčŗčģ count ą▒čāą┤ąĄčé ą▓čŗąĘą▓ą░ąĮą░ čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēą░čÅ ą┐čĆąŠčåąĄą┤čāčĆą░ inc(count); -- ąĖą╝ąĄąĮąŠą▓ą░ąĮąĮąŠąĄ čüąŠą┐ąŠčüčéą░ą▓ą╗ąĄąĮąĖąĄ inc(a => count, by => open) inc(a => count)

![ąÜčāą╗ą░ąĮąŠą▓ ąÆ.ąÉ.

[v.kulanov@csn.khai.edu]

ą¤ąŠą┤ą┐čĆąŠą│čĆą░ą╝ą╝čŗ.

ą¤čĆąŠčåąĄą┤čāčĆčŗ ą▓ čÅąĘčŗą║ąĄ VHDL

┬½ąóąĄčģąĮąŠą╗ąŠą│ąĖąĖ ą┐čĆąŠąĄą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ

ą║ąŠą╝ą┐čīčÄč鹥čĆąĮčŗčģ čüąĖčüč鹥ą╝┬╗](https://image.slidesharecdn.com/lecturevhdlprocedures-170514200111/85/Subprograms-in-VHDL-Procedures-in-VHDL-1-320.jpg)

![ą¤čĆąŠčåąĄą┤čāčĆčŗ ą▓ VHDL

PROCEDURE name[(parameter_interface_list)] IS

{subprogram_declarative_item}

BEGIN

{sequential_statement}

END [PROCEDURE] [name];

SIGNAL, TYPE, FILE,

SUBTYPE, PROCEDURE,

FUNCTION, VARIABLE,

COMPONENT, CONSTANT

...-- ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗąĄ ąŠą┐ąĄčĆą░č鹊čĆčŗ

a := 5

FOR ŌĆ” LOOP ŌĆ” END LOOP;

...

IF ŌĆ” THEN ŌĆ” ELSE ŌĆ” END IF;

ąśą╝čÅ ą┐čĆąŠčåąĄą┤čāčĆčŗ

ąĪą┐ąĖčüąŠą║ č乊čĆą╝ą░ą╗čīąĮčŗčģ ą┐ą░čĆą░ą╝ąĄčéčĆąŠą▓

(ą╝ąŠąČąĄčé ąŠčéčüčāčéčüčéą▓ąŠą▓ą░čéčī)](https://image.slidesharecdn.com/lecturevhdlprocedures-170514200111/85/Subprograms-in-VHDL-Procedures-in-VHDL-3-320.jpg)

![ąĪą┐ąĖčüąŠą║ ą┐ą░čĆą░ą╝ąĄčéčĆąŠą▓ ą┐čĆąŠčåąĄą┤čāčĆčŗ

PROCEDURE name[(parameter_interface_list)] IS

...

([CONSTANT|VARIABLE|SIGNAL] identifier {,ŌĆ”}:

[IN|OUT|INOUT] type_indication [:= expression] {;ŌĆ”})

ąśą╝čÅ/ąśą┤ąĄąĮčéąĖčäąĖą║ą░č鹊čĆ

ą┐ą░čĆą░ą╝ąĄčéčĆą░

ąÜą╗ą░čüčü ą┐ą░čĆą░ą╝ąĄčéčĆą░

(ą╝ąŠąČąĄčé ą▒čŗčéčī ąĄčēąĄ FILE)

ąÆąĖą┤

ą┐ą░čĆą░ą╝ąĄčéčĆą░

ąóąĖą┐

ą┐ą░čĆą░ą╝ąĄčéčĆą░

ąŚąĮą░č湥ąĮąĖąĄ ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ.

ą£ąŠąČąĄčé ą▒čŗčéčī ąĘą░ą┤ą░ąĮąŠ č鹊ą╗čīą║ąŠ

ą┤ą╗čÅ ą┐ą░čĆą░ą╝ąĄčéčĆąŠą▓ ą║ą╗ą░čüčüą░

CONSTANT ąĖ VARIABLE

PROCEDURE foo(val: INTEGER) -- val - CONSTANT

PROCEDURE foo(val: IN INTEGER) -- val - CONSTANT

PROCEDURE foo(val, bar: OUT INTEGER) -- val, bar - VARIABLE

PROCEDURE foo(val: INOUT INTEGER) -- val ŌĆō VARIABLE](https://image.slidesharecdn.com/lecturevhdlprocedures-170514200111/85/Subprograms-in-VHDL-Procedures-in-VHDL-5-320.jpg)

![ąÆčŗąĘąŠą▓ ą┐čĆąŠčåąĄą┤čāčĆčŗ ą▓ VHDL

’é¦ ąÆčŗąĘąŠą▓ ą┐čĆąŠčåąĄą┤čāčĆčŗ ąĘą░ą┐ąĖčüčŗą▓ą░ąĄčéčüčÅ ą▓ ąĖčüčģąŠą┤ąĮąŠą╝ ą║ąŠą┤ąĄ ą║ą░ą║

ąŠčéą┤ąĄą╗čīąĮčŗą╣ ąŠą┐ąĄčĆą░č鹊čĆ, ą║ąŠč鹊čĆčŗą╣ ąĖą╝ąĄąĄčé čüą╗ąĄą┤čāčÄčēąĖą╣ čüąĖąĮčéą░ą║čüąĖčü:

[label:] name [(parameter_list)];

ą£ąĄčéą║ą░ ąĪą┐ąĖčüąŠą║ čäą░ą║čéąĖč湥čüą║ąĖčģ ą┐ą░čĆą░ą╝ąĄčéčĆąŠą▓

([parameter_name =>]

expression|signal_name|variable_name|OPEN, {ŌĆ”})

ążąŠčĆą╝ą░ą╗čīąĮčŗą╣ ą┐ą░čĆą░ą╝ąĄčéčĆ

ąöą▓ą░ čéąĖą┐ą░ čüąŠą┐ąŠčüčéą░ą▓ą╗ąĄąĮąĖčÅ:

’é¦ ąśą╝ąĄąĮąŠą▓ą░ąĮąĮąŠąĄ (=>)

’é¦ ą¤ąŠąĘąĖčåąĖąŠąĮąĮąŠąĄ

ążą░ą║čéąĖč湥čüą║ąĖą╣ ą┐ą░čĆą░ą╝ąĄčéčĆ

’é¦ ąÆčŗčĆą░ąČąĄąĮąĖąĄ/ąÜąŠąĮčüčéą░ąĮčéąĮąŠąĄ ąĘąĮą░č湥ąĮąĖąĄ

’é¦ ąĪąĖą│ąĮą░ą╗

’é¦ ą¤ąĄčĆąĄą╝ąĄąĮąĮą░čÅ

’é¦ ąÜą╗čÄč湥ą▓ąŠąĄ čüą╗ąŠą▓ąŠ OPEN - ąĮąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ąĖą╗ąĖ ąĘąĮą░č湥ąĮąĖąĄ ą┐ąŠ čāą╝ąŠą╗čćą░ąĮąĖčÄ](https://image.slidesharecdn.com/lecturevhdlprocedures-170514200111/85/Subprograms-in-VHDL-Procedures-in-VHDL-6-320.jpg)

![ą¤čĆąŠčåąĄą┤čāčĆčŗ ą▓ VHDL

’é¦ ąÆ č鹥ą╗ąĄ ą┐čĆąŠčåąĄą┤čāčĆčŗ ą╝ąŠąČąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčīčüčÅ ąŠą┐ąĄčĆą░č鹊čĆ

RETURN, ąĮą░ąĘąĮą░č湥ąĮąĖąĄ ą║ąŠč鹊čĆąŠą│ąŠ ŌĆō ąĘą░ą▓ąĄčĆčłąĄąĮąĖąĄ ą▓čŗą┐ąŠą╗ąĮąĄąĮąĖčÅ

ą┐čĆąŠčåąĄą┤čāčĆčŗ:

[label:] RETURN;

PROCEDURE sort2(VARIABLE x1,x2: INOUT INTEGER) IS

VARIABLE t: INTEGER;

BEGIN

IF x1 > x2 THEN

RETURN;

ELSE

t := x1;

x1 := x2;

x2 := t;

END IF;

END PROCEDURE;

ąÜą░ą║ čŹč鹊 čüą┤ąĄą╗ą░čéčī ą▒ąĄąĘ

ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮąŠą╣

ą┐ąĄčĆąĄą╝ąĄąĮąĮąŠą╣ "t"?](https://image.slidesharecdn.com/lecturevhdlprocedures-170514200111/85/Subprograms-in-VHDL-Procedures-in-VHDL-15-320.jpg)