The Big Question

Download as pptx, pdf0 likes644 views

The document discusses the importance of curiosity in learning, referencing Sylvia Earle's perspective on the attributes of great scientists. It addresses common questions about learning SPICE and provides an overview of clock buffer delay calculations using delay models. The author emphasizes the connection between theoretical understanding and practical application in circuit design, inviting readers to join related courses on VLSI design and SPICE simulations.

1 of 16

Downloaded 20 times

Ad

Recommended

Common clock path pessimism removal

Common clock path pessimism removalkunal ghosh (vlsisystemdesign.com)

Ěý

The document discusses common clock path pessimism removal (CPPR) in timing path analysis, emphasizing the importance of reducing pessimism to achieve accurate timing reports. It explains how on-chip variation (OCV) can create additional pessimism, affecting slack calculations, and introduces a method to alleviate this issue by either adjusting data required time or data arrival time. The author highlights the significance of strong foundational knowledge in achieving efficient solutions without extensive changes to existing calculations.Signal Integrity (SI glitch)

Signal Integrity (SI glitch)kunal ghosh (vlsisystemdesign.com)

Ěý

The document discusses the concept of signal integrity (SI) in circuit design, highlighting the challenges posed by signal glitches caused by interference between closely packed wires in silicon circuits. It explains the role of aggressor and victim wires, the significance of drive strength, and strategies to minimize glitches through careful optimization of inverter sizes. Ultimately, the author emphasizes the importance of understanding and managing signal integrity to avoid potential issues that can arise in high-speed applications.On-Chip Variation

On-Chip Variationkunal ghosh (vlsisystemdesign.com)

Ěý

The document discusses on-chip variation (OCV) in static timing analysis, focusing on how variations during the etching and oxide thickness processes impact the performance of inverters in a clock path. It highlights the importance of modeling these variations in OCV calculations to assess how they affect drain current and propagation delay, which is crucial for ensuring proper timing in VLSI design. The author also shares personal experiences and resources related to circuit design and physical design flows.Regular buffer v/s Clock buffer

Regular buffer v/s Clock bufferkunal ghosh (vlsisystemdesign.com)

Ěý

The document discusses the differences between regular buffers and clock buffers in physical design and static timing analysis. It explains how the asymmetrical waveform at clock endpoints, caused by the varying resistances of NMOS and PMOS transistors, leads to unequal rise and fall times, impacting performance. The solution involves designing specialized clock buffers with increased PMOS width to match NMOS resistance, improving timing accuracy but at the cost of larger chip area and increased leakage.Cracking for beginners - copy (2)

Cracking for beginners - copy (2)BAHADUR SINGH THAKUR

Ěý

This tutorial provides an introduction to assembly language (ASM) and the debugger WinICE to help beginners start cracking programs. It discusses basic ASM concepts like registers, operations like MOV, CMP, jumps. It explains how to use WinICE - setting breakpoints, using commands like 'r' to modify registers, and tips to avoid analyzing unnecessary DLL code. The goal is to start from the basics of ASM and debugging to understand cracking at an introductory level.Threads and Java Memory Model Explained

Threads and Java Memory Model ExplainedLuiz Fernando Teston

Ěý

The document explains the intricacies of threads and the Java memory model, particularly focusing on race conditions and deadlocks. It emphasizes the importance of proper synchronization, using mechanisms such as locks and concurrent classes, to avoid performance issues and invalid states. Additionally, it suggests minimizing data sharing and considering high-level APIs and frameworks to handle threading more effectively.Physical design

Physical design Mantra VLSI

Ěý

The document outlines the comprehensive processes and components involved in VLSI physical design, including various types of integrations, design flows, physical design transformations, and data preparation steps. Key concepts like floor planning, placement, timing analysis, and verification methods are discussed, indicating their essential roles in chip manufacturing. Additionally, the document provides detailed terminology, design checks, and considerations for ensuring successful physical design outcomes.Write your own generic SPICE Power Supplies controller models

Write your own generic SPICE Power Supplies controller modelsTsuyoshi Horigome

Ěý

This document discusses writing generic SPICE models for power supply controllers. It begins by explaining that exact SPICE models may not exist or be compatible with the user's simulator. The solution is to write a generic model and adapt it to the specific controller. It then provides examples of using behavioral (B) elements to model nonlinear functions like comparators and logic gates in different simulators like ISspice, PSpice, and AWB. Guidelines are given for writing models step-by-step, including using subcircuits and descriptive names. Finally, it discusses modeling a constant frequency current mode PWM controller as an example application.Advd lecture 7 logical effort

Advd lecture 7 logical effortHardik Gupta

Ěý

The document discusses delay modeling in digital VLSI circuits. It notes that circuit delay depends on many factors like charge, discharge, parasitics, transistor width-to-length ratio, fan-in, fan-out and topology. Existing delay models do not clearly indicate the contribution of each factor. This wastes circuit designers' time in simulation and tweaking. The document then presents a delay model based on logical effort that estimates delay based on the topology of the gate and relative sizes of its transistors. It shows how to compute logical effort values and parasitic delays for different gates. Applying this model helps optimize circuit design parameters like transistor sizes, number of stages in a path and topology for minimum delay.Digital Wave vs. Nodal Analysis for Circuit Simulation: an experimental compa...

Digital Wave vs. Nodal Analysis for Circuit Simulation: an experimental compa...Piero Belforte

Ěý

This document compares Digital Wave Simulation (DWS) with various SPICE versions for circuit simulation in terms of accuracy and execution speed using different time steps. It highlights the advantages of DWS in handling complex circuit simulations more efficiently than traditional nodal analysis. The analysis encompasses various circuit types and emphasizes the compatibility and discrepancies in syntax between DWS and SPICE models, particularly for transmission line circuits.Library Characterization Flow

Library Characterization FlowSatish Grandhi

Ěý

This document discusses library characterization, which involves characterizing standard cell libraries used in semiconductor design. It begins with an overview of why library characterization is an interesting career and then discusses fundamental terminology. It provides examples of characterizing an inverter and D flip-flop, covering timing analysis, power characterization, and more. Advanced topics discussed include state dependent delays, load capacitance characterization, and measuring tri-state delays. References are provided for further reading.SPICE LEVEL I/LEVEL II/LEVEL III AND BSIM MODELS

SPICE LEVEL I/LEVEL II/LEVEL III AND BSIM MODELSPraveen Kumar

Ěý

SPICE (Simulation Program with Integrated Circuit Emphasis) is an open-source analog circuit simulator used in integrated circuit design to predict behavior and check integrity before manufacturing. The document details the history and evolution of SPICE models, specifically Level 1, Level 2, and Level 3, each offering improvements in accuracy and complexity for modeling semiconductor devices. Additionally, it discusses the Berkeley Short-channel IGFET Model (BSIM) as an empirical approach to accurately simulate small geometry effects in modern transistors.Dependent Current Sources

Dependent Current Sources Tsuyoshi Horigome

Ěý

The document describes the syntax and parameters for different types of dependent current and voltage sources (G elements) in SPICE, including:

- Voltage controlled current sources (VCCS)

- Voltage controlled resistors (VCR)

- Voltage controlled capacitors (VCCAP)

It provides examples of how to model switches, MOSFETs, diodes, and triodes using these elements. Parameters like MAX, MIN, SCALE, and TC1/TC2 adjust current, resistance, and capacitance values, while PWL defines piecewise linear functions. DELAY adds a propagation delay.VLSI Static Timing Analysis Intro Part 1

VLSI Static Timing Analysis Intro Part 1Amr Adel

Ěý

The document provides an overview of static timing analysis in digital VLSI chip design, highlighting that timing is the primary focus to ensure functionality post-fabrication. It details key timing checks necessary for validation, such as setup and hold timing, and discusses the propagation delay in RC circuits, emphasizing the factors influencing delay, including resistance, capacitance, and transistor sizing. The document also explains how designers use timing tables and calculations to determine timing paths and optimize chip performance.Device Modeling of Delay using PSpice

Device Modeling of Delay using PSpiceTsuyoshi Horigome

Ěý

This document describes an equivalent circuit model for delay in PSpice. The circuit uses gates, resistors, capacitors and voltage-controlled voltage sources to model the behavior of a delay circuit. It provides the component values and equations used in the simulation. The parameters and expected output waveforms are also defined for testing the delay.PSpice Tutorial

PSpice Tutorialankitgdoshi

Ěý

This document provides an overview of PSPICE and how to use it to simulate analog circuits. It describes the different types of input files for PSPICE, how to define circuit components and models, and the various analysis statements like .OP, .DC, .AC, and .TRAN to set up DC operating point, DC sweep, AC, and transient analyses respectively. It also covers topics like subcircuits, semiconductor device models, and scale factors for numbers in PSPICE.Using p-Spice in VLSI design and Testing

Using p-Spice in VLSI design and TestingManjunath852579

Ěý

The document outlines the use of SPICE simulation in CMOS VLSI design, focusing on topics like DC and transient analysis, optimization, and power measurement. It provides details on writing SPICE decks, conducting simulations, and analyzing results, including logical effort characterization. Various examples are included to illustrate the simulation process and optimization techniques for circuit design.Jy3517271730

Jy3517271730IJERA Editor

Ěý

The article presents an analytical model to calculate delay for global interconnects in very deep sub-micron (VDSM) technology, highlighting the negative impact of secondary effects like crosstalk noise on circuit performance. The proposed model incorporates wire resistances, capacitances, and inductances and derives an expression for delay, which is validated against simulated results, demonstrating a minimal error. Future work aims to simplify the derived equations for broader applications in high-speed circuit designs.4 ee600 lab2_grp

4 ee600 lab2_grpLoren Schwappach

Ěý

This document describes a lab report on modeling in SPICE. It includes:

1) Testing the validity of an NMOS transistor model by comparing hand calculations of drain currents to SPICE simulation results.

2) Finding accurate MOSFET model parameters by matching measured data to equations and simulations.

3) Evaluating a CMOS inverter model in SPICE by analyzing its digital characteristics.

4) Comparing CMOS and BJT TTL inverter models in SPICE to determine modeling usefulness.Pcb carolina scg_2010

Pcb carolina scg_2010tcoyle72

Ěý

This document discusses the importance of signal integrity simulations for PCB design. It emphasizes that simulations provide solutions to improve performance and reduce costs when done with the right metrics and quality models. Case studies demonstrate how simulations can show that expensive clock termination is not needed for a design or that stripline routing has too much crosstalk compared to microstrip. Good simulations rely on metrics like noise margin and timing margin to analyze waveforms as well as accurate transmission line and I/O buffer models.Pcb carolina scg_2010

Pcb carolina scg_2010tcoyle72

Ěý

This document discusses the importance of signal integrity simulations for PCB design. It emphasizes that simulations provide solutions to improve performance and reduce costs when done with the right metrics and models. Case studies show how simulations can determine if certain design choices like termination resistors or microstrip vs stripline routing are needed. Good metrics for analysis include noise margin, timing margin, and waveform characteristics. Accurate models of transmission lines, I/O buffers, and packages are also key to get reliable simulation results.100 MHz High Speed SPI Master: Design, Implementation and Study on Limitation...

100 MHz High Speed SPI Master: Design, Implementation and Study on Limitation...rahulmonikasharma

Ěý

This document presents the design and implementation of a 100 MHz high-speed SPI master core on an FPGA, utilizing a state machine approach for its RTL design. It discusses the challenges and limitations in implementing high-speed SPI communications, particularly regarding signal integrity and interconnect constraints. The design achieved successful synthesis and timing verification, demonstrating its operational effectiveness while highlighting critical aspects that affect speed and distance in digital systems.07_Digital timing_&_Pipelining.ppt

07_Digital timing_&_Pipelining.pptBUCHUPALLIVIMALAREDD2

Ěý

This document discusses timing analysis of logic circuits. It defines propagation delay time (tp) as the time required for an output signal to change due to a change in the input signal. A timing diagram is used to graphically represent tp. The document discusses how real circuits have intrinsic resistance and capacitance that cause delay. It provides an example of calculating delay through a simple RC circuit. Combinational logic delay is represented using a cloud model. The document also discusses setup time, hold time, and register delay time for D flip-flops and how to calculate maximum switching frequency, including using pipelining to increase maximum frequency.1240381638.fafafaafafaafafafafaffffffffffpptx

1240381638.fafafaafafaafafafafaffffffffffpptxrajukolluri

Ěý

The document discusses electrical characteristics of layers in semiconductor technology, focusing on sheet resistance, unit capacitance, and delay associated with inverters and circuitry. It explains various calculations for resistance and capacitance, particularly in CMOS inverters, as well as the impact of load capacitance on delay in cascaded inverters. Additionally, it outlines factors affecting rise time and fall time, emphasizing the importance of optimizing transistor sizing to achieve symmetrical operation.Coupling Aware Explicit Delay Metric for On- Chip RLC Interconnect for Ramp i...

Coupling Aware Explicit Delay Metric for On- Chip RLC Interconnect for Ramp i...IDES Editor

Ěý

This document presents a novel analytical delay model for RLC interconnects under ramp input conditions, addressing limitations of existing methods which often rely on the Elmore delay approximation. The proposed model shows improved accuracy, estimating delays within 4% of SPICE-computed results, and significantly outperforms traditional simulation methods, providing faster calculations essential for VLSI design. The study highlights the impact of ramp input on delay estimation and suggests possible applications for arbitrary interconnect trees.Device Modeling of Delay using PSpice

Device Modeling of Delay using PSpiceTsuyoshi Horigome

Ěý

This document describes using PSpice to model delay in a circuit. The circuit contains resistors, capacitors, voltage sources, and behavioral voltage-controlled switches to model the delay between an input and output signal. The simulation will examine the delay time as the output signal rises after the input signal exceeds a threshold level controlled by an oscillator.Cadastral Maps

Cadastral MapsGoogle

Ěý

Preparation of cadastral maps based by Engineer Dungo Tizazu from Dire Dawa University More Related Content

Similar to The Big Question (20)

Advd lecture 7 logical effort

Advd lecture 7 logical effortHardik Gupta

Ěý

The document discusses delay modeling in digital VLSI circuits. It notes that circuit delay depends on many factors like charge, discharge, parasitics, transistor width-to-length ratio, fan-in, fan-out and topology. Existing delay models do not clearly indicate the contribution of each factor. This wastes circuit designers' time in simulation and tweaking. The document then presents a delay model based on logical effort that estimates delay based on the topology of the gate and relative sizes of its transistors. It shows how to compute logical effort values and parasitic delays for different gates. Applying this model helps optimize circuit design parameters like transistor sizes, number of stages in a path and topology for minimum delay.Digital Wave vs. Nodal Analysis for Circuit Simulation: an experimental compa...

Digital Wave vs. Nodal Analysis for Circuit Simulation: an experimental compa...Piero Belforte

Ěý

This document compares Digital Wave Simulation (DWS) with various SPICE versions for circuit simulation in terms of accuracy and execution speed using different time steps. It highlights the advantages of DWS in handling complex circuit simulations more efficiently than traditional nodal analysis. The analysis encompasses various circuit types and emphasizes the compatibility and discrepancies in syntax between DWS and SPICE models, particularly for transmission line circuits.Library Characterization Flow

Library Characterization FlowSatish Grandhi

Ěý

This document discusses library characterization, which involves characterizing standard cell libraries used in semiconductor design. It begins with an overview of why library characterization is an interesting career and then discusses fundamental terminology. It provides examples of characterizing an inverter and D flip-flop, covering timing analysis, power characterization, and more. Advanced topics discussed include state dependent delays, load capacitance characterization, and measuring tri-state delays. References are provided for further reading.SPICE LEVEL I/LEVEL II/LEVEL III AND BSIM MODELS

SPICE LEVEL I/LEVEL II/LEVEL III AND BSIM MODELSPraveen Kumar

Ěý

SPICE (Simulation Program with Integrated Circuit Emphasis) is an open-source analog circuit simulator used in integrated circuit design to predict behavior and check integrity before manufacturing. The document details the history and evolution of SPICE models, specifically Level 1, Level 2, and Level 3, each offering improvements in accuracy and complexity for modeling semiconductor devices. Additionally, it discusses the Berkeley Short-channel IGFET Model (BSIM) as an empirical approach to accurately simulate small geometry effects in modern transistors.Dependent Current Sources

Dependent Current Sources Tsuyoshi Horigome

Ěý

The document describes the syntax and parameters for different types of dependent current and voltage sources (G elements) in SPICE, including:

- Voltage controlled current sources (VCCS)

- Voltage controlled resistors (VCR)

- Voltage controlled capacitors (VCCAP)

It provides examples of how to model switches, MOSFETs, diodes, and triodes using these elements. Parameters like MAX, MIN, SCALE, and TC1/TC2 adjust current, resistance, and capacitance values, while PWL defines piecewise linear functions. DELAY adds a propagation delay.VLSI Static Timing Analysis Intro Part 1

VLSI Static Timing Analysis Intro Part 1Amr Adel

Ěý

The document provides an overview of static timing analysis in digital VLSI chip design, highlighting that timing is the primary focus to ensure functionality post-fabrication. It details key timing checks necessary for validation, such as setup and hold timing, and discusses the propagation delay in RC circuits, emphasizing the factors influencing delay, including resistance, capacitance, and transistor sizing. The document also explains how designers use timing tables and calculations to determine timing paths and optimize chip performance.Device Modeling of Delay using PSpice

Device Modeling of Delay using PSpiceTsuyoshi Horigome

Ěý

This document describes an equivalent circuit model for delay in PSpice. The circuit uses gates, resistors, capacitors and voltage-controlled voltage sources to model the behavior of a delay circuit. It provides the component values and equations used in the simulation. The parameters and expected output waveforms are also defined for testing the delay.PSpice Tutorial

PSpice Tutorialankitgdoshi

Ěý

This document provides an overview of PSPICE and how to use it to simulate analog circuits. It describes the different types of input files for PSPICE, how to define circuit components and models, and the various analysis statements like .OP, .DC, .AC, and .TRAN to set up DC operating point, DC sweep, AC, and transient analyses respectively. It also covers topics like subcircuits, semiconductor device models, and scale factors for numbers in PSPICE.Using p-Spice in VLSI design and Testing

Using p-Spice in VLSI design and TestingManjunath852579

Ěý

The document outlines the use of SPICE simulation in CMOS VLSI design, focusing on topics like DC and transient analysis, optimization, and power measurement. It provides details on writing SPICE decks, conducting simulations, and analyzing results, including logical effort characterization. Various examples are included to illustrate the simulation process and optimization techniques for circuit design.Jy3517271730

Jy3517271730IJERA Editor

Ěý

The article presents an analytical model to calculate delay for global interconnects in very deep sub-micron (VDSM) technology, highlighting the negative impact of secondary effects like crosstalk noise on circuit performance. The proposed model incorporates wire resistances, capacitances, and inductances and derives an expression for delay, which is validated against simulated results, demonstrating a minimal error. Future work aims to simplify the derived equations for broader applications in high-speed circuit designs.4 ee600 lab2_grp

4 ee600 lab2_grpLoren Schwappach

Ěý

This document describes a lab report on modeling in SPICE. It includes:

1) Testing the validity of an NMOS transistor model by comparing hand calculations of drain currents to SPICE simulation results.

2) Finding accurate MOSFET model parameters by matching measured data to equations and simulations.

3) Evaluating a CMOS inverter model in SPICE by analyzing its digital characteristics.

4) Comparing CMOS and BJT TTL inverter models in SPICE to determine modeling usefulness.Pcb carolina scg_2010

Pcb carolina scg_2010tcoyle72

Ěý

This document discusses the importance of signal integrity simulations for PCB design. It emphasizes that simulations provide solutions to improve performance and reduce costs when done with the right metrics and quality models. Case studies demonstrate how simulations can show that expensive clock termination is not needed for a design or that stripline routing has too much crosstalk compared to microstrip. Good simulations rely on metrics like noise margin and timing margin to analyze waveforms as well as accurate transmission line and I/O buffer models.Pcb carolina scg_2010

Pcb carolina scg_2010tcoyle72

Ěý

This document discusses the importance of signal integrity simulations for PCB design. It emphasizes that simulations provide solutions to improve performance and reduce costs when done with the right metrics and models. Case studies show how simulations can determine if certain design choices like termination resistors or microstrip vs stripline routing are needed. Good metrics for analysis include noise margin, timing margin, and waveform characteristics. Accurate models of transmission lines, I/O buffers, and packages are also key to get reliable simulation results.100 MHz High Speed SPI Master: Design, Implementation and Study on Limitation...

100 MHz High Speed SPI Master: Design, Implementation and Study on Limitation...rahulmonikasharma

Ěý

This document presents the design and implementation of a 100 MHz high-speed SPI master core on an FPGA, utilizing a state machine approach for its RTL design. It discusses the challenges and limitations in implementing high-speed SPI communications, particularly regarding signal integrity and interconnect constraints. The design achieved successful synthesis and timing verification, demonstrating its operational effectiveness while highlighting critical aspects that affect speed and distance in digital systems.07_Digital timing_&_Pipelining.ppt

07_Digital timing_&_Pipelining.pptBUCHUPALLIVIMALAREDD2

Ěý

This document discusses timing analysis of logic circuits. It defines propagation delay time (tp) as the time required for an output signal to change due to a change in the input signal. A timing diagram is used to graphically represent tp. The document discusses how real circuits have intrinsic resistance and capacitance that cause delay. It provides an example of calculating delay through a simple RC circuit. Combinational logic delay is represented using a cloud model. The document also discusses setup time, hold time, and register delay time for D flip-flops and how to calculate maximum switching frequency, including using pipelining to increase maximum frequency.1240381638.fafafaafafaafafafafaffffffffffpptx

1240381638.fafafaafafaafafafafaffffffffffpptxrajukolluri

Ěý

The document discusses electrical characteristics of layers in semiconductor technology, focusing on sheet resistance, unit capacitance, and delay associated with inverters and circuitry. It explains various calculations for resistance and capacitance, particularly in CMOS inverters, as well as the impact of load capacitance on delay in cascaded inverters. Additionally, it outlines factors affecting rise time and fall time, emphasizing the importance of optimizing transistor sizing to achieve symmetrical operation.Coupling Aware Explicit Delay Metric for On- Chip RLC Interconnect for Ramp i...

Coupling Aware Explicit Delay Metric for On- Chip RLC Interconnect for Ramp i...IDES Editor

Ěý

This document presents a novel analytical delay model for RLC interconnects under ramp input conditions, addressing limitations of existing methods which often rely on the Elmore delay approximation. The proposed model shows improved accuracy, estimating delays within 4% of SPICE-computed results, and significantly outperforms traditional simulation methods, providing faster calculations essential for VLSI design. The study highlights the impact of ramp input on delay estimation and suggests possible applications for arbitrary interconnect trees.Device Modeling of Delay using PSpice

Device Modeling of Delay using PSpiceTsuyoshi Horigome

Ěý

This document describes using PSpice to model delay in a circuit. The circuit contains resistors, capacitors, voltage sources, and behavioral voltage-controlled switches to model the delay between an input and output signal. The simulation will examine the delay time as the output signal rises after the input signal exceeds a threshold level controlled by an oscillator.Recently uploaded (20)

Cadastral Maps

Cadastral MapsGoogle

Ěý

Preparation of cadastral maps based by Engineer Dungo Tizazu from Dire Dawa University Rapid Prototyping for XR: Lecture 6 - AI for Prototyping and Research Directi...

Rapid Prototyping for XR: Lecture 6 - AI for Prototyping and Research Directi...Mark Billinghurst

Ěý

This is lecture 6 in the course on Rapid Prototyping for XR, taught on June 13th, 2025 by Mark Billinghurst. This lecture was about using AI for Prototyping and Research Directions. Deep Learning for Natural Language Processing_FDP on 16 June 2025 MITS.pptx

Deep Learning for Natural Language Processing_FDP on 16 June 2025 MITS.pptxresming1

Ěý

This gives an introduction to how NLP has evolved from the time of World War II till this date through the advances in approaches, architectures and word representations. From rule based approaches, it advanced to statistical approaches. from traditional machine learning algorithms it advanced to deep neural network architectures. Deep neural architectures include recurrent neural networks, long short term memory, gated recurrent units, seq2seq models, encoder decoder models, transformer architecture, upto large language models and vision language models which are multimodal in nature.Fundamentals of Digital Design_Class_21st May - Copy.pptx

Fundamentals of Digital Design_Class_21st May - Copy.pptxdrdebarshi1993

Ěý

Basics of Number Systems and Logic GatesFundamentals of Digital Design_Class_12th April.pptx

Fundamentals of Digital Design_Class_12th April.pptxdrdebarshi1993

Ěý

Boolean Algebra and Combinational Logic CircuitDeep Learning for Image Processing on 16 June 2025 MITS.pptx

Deep Learning for Image Processing on 16 June 2025 MITS.pptxresming1

Ěý

This covers how image processing or the field of computer vision has advanced with the advent of neural network architectures ranging from LeNet to Vision transformers. It covers how deep neural network architectures have developed step-by-step from the popular CNNs to ViTs. CNNs and its variants along with their features are described. Vision transformers are introduced and compared with CNNs. It also shows how an image is processed to be given as input to the vision transformer. It give the applications of computer vision.Machine Learning - Classification Algorithms

Machine Learning - Classification Algorithmsresming1

Ěý

This covers traditional machine learning algorithms for classification. It includes Support vector machines, decision trees, Naive Bayes classifier , neural networks, etc.

It also discusses about model evaluation and selection. It discusses ID3 and C4.5 algorithms. It also describes k-nearest neighbor classifer.Stay Safe Women Security Android App Project Report.pdf

Stay Safe Women Security Android App Project Report.pdfKamal Acharya

Ěý

Women’s security is a critical issue in today’s world and it’s very much needed for every individual

to be acting over such an issue. This document describes a GPS based “Women Security System''

that provides the combination of GPS devices as well as provide alerts and messages with an

emergency button trigger whenever somebody is in trouble They might not have so much time, all

that they have to do is generate a distress emergency signal by shaking up their phone. Our system

provides a realizable, cost effective solution to problem detection. Nowdays due to recently

happened cases such as rape by drivers or colleagues, burglary etc., women security, especially

women security has become the foremost priority of the world. System uses the Global Positioning

System (GPS) technology to find out the location of women. The information of women's position

provided by the device can be viewed on Google maps using Internet or specialized software. The

companies are looking for-ward to the security problem and require a system that will efficiently

evaluate the problem of women security working in night shifts, traveling alone. We focus on the

proposed model that can be used to deal with the security issue of women using GPS based tracking

systems.(Continuous Integration and Continuous Deployment/Delivery) is a fundamental ...

(Continuous Integration and Continuous Deployment/Delivery) is a fundamental ...ketan09101

Ěý

(Continuous Integration and Continuous Deployment/Delivery) is a fundamental practice in DevOps that streamlines software development and deployment.Tesla-Stock-Analysis-and-Forecast.pptx (1).pptx

Tesla-Stock-Analysis-and-Forecast.pptx (1).pptxmoonsony54

Ěý

this is data science ppt for tesla stock (linear regression)Introduction to Python Programming Language

Introduction to Python Programming Languagemerlinjohnsy

Ěý

This PPT covers features, applications, variable, data types and statements in PythonAd

The Big Question

- 2. "The best scientists and explorers have the attributes of kids! They ask question and have a sense of wonder. They have curiosity. 'Who, what, where, why, when and how'! They never stop asking questions, and I never stop asking questions, just like a five year old" - Sylvia Earle

- 3. I was overwhelmed by the very common question being asked to me after my previous post, and these were from all levels of people (even people from verification and embedded background). "Why do we need to learn SPICE?" And, that was exactly what I was expecting. "For the things we have to learn before we can do them, we learn by doing them". Though, this will be discussed in detail in my upcoming course of SPICE, let me try to give a glimpse of it here itself Below is a snippet from my existing course on Clock Tree Synthesis

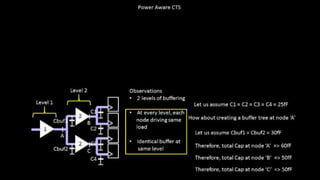

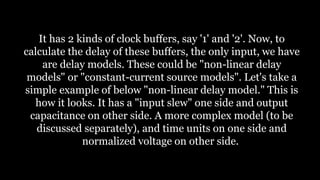

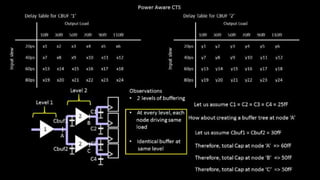

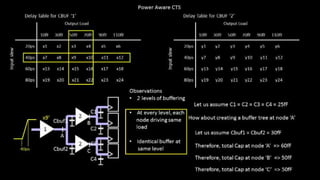

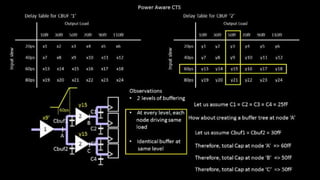

- 5. It has 2 kinds of clock buffers, say '1' and '2'. Now, to calculate the delay of these buffers, the only input, we have are delay models. These could be "non-linear delay models" or "constant-current source models". Let's take a simple example of below "non-linear delay model." This is how it looks. It has a "input slew" one side and output capacitance on other side. A more complex model (to be discussed separately), and time units on one side and normalized voltage on other side.

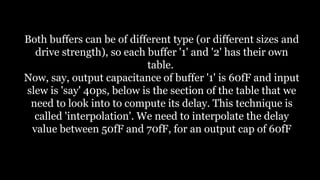

- 7. Both buffers can be of different type (or different sizes and drive strength), so each buffer '1' and '2' has their own table. Now, say, output capacitance of buffer '1' is 60fF and input slew is 'say' 40ps, below is the section of the table that we need to look into to compute its delay. This technique is called 'interpolation'. We need to interpolate the delay value between 50fF and 70fF, for an output cap of 60fF

- 9. Similarly, for an input slew of 'say' 60ps and output load of '50fF', the delay value of buffer '2' will be about 'y15', as per below table

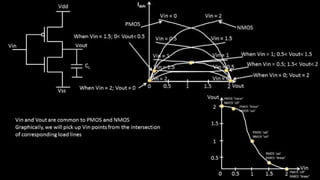

- 11. I haven't yet answered your question. Why do we need to learn SPICE? I will answer it now. Where, do you think, the delay values in the table come from? Let's say we have this below inverter (simple buffer is 2 inverters connected back to back), with the below IO characteristics.

- 13. Now, observe very carefully to all above waveforms (specially the last one present in bottom right). Do they remind you of look-alike waveforms, for which we just calculated the delay? Does the waveform at the top- middle, remind you of the waveforms we derived in last post using a SPICE simulator? Do they look like Id-Vds curves for NMOS? Do you relate how delay of cells are actually derived from NMOS-PMOS-CMOS transfer characteristics?

- 14. I think I gave enough hints over here. I will see you in class of "VLSI Academy - Circuit design and SPICE simulations" on Udemy "You can swim all day in the Sea of Knowledge and still come out completely dry. Most people do." Norman Juster If so, you are on the right path. Stay with me @ vlsisystemdesign.com and I will notify you more about this course

- 15. For more, please refer to below courses Circuit design & SPICE simulations https://www.udemy.com/vlsi-academy-circuit-design/?couponCode=forşÝşÝߣshare Physical design flow https://www.udemy.com/vlsi-academy-physical-design-flow/?couponCode=forşÝşÝߣshare Clock tree synthesis https://www.udemy.com/vlsi-academy-clock-tree-synthesis/?couponCode=forşÝşÝߣshare Signal integrity https://www.udemy.com/vlsi-academy-crosstalk/?couponCode=forşÝşÝߣshare VLSI – Essential concepts and detailed interview guide https://www.udemy.com/vlsi-academy/?couponCode=forşÝşÝߣshare

- 16. THANK YOU