Verilog full adder in dataflow & gate level modelling style.

3 likes49,732 views

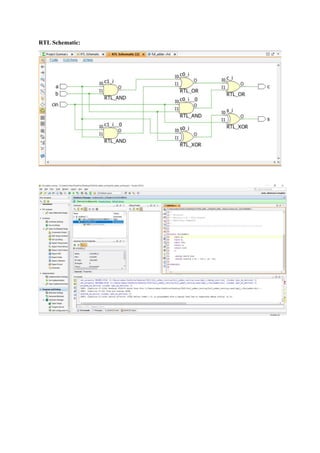

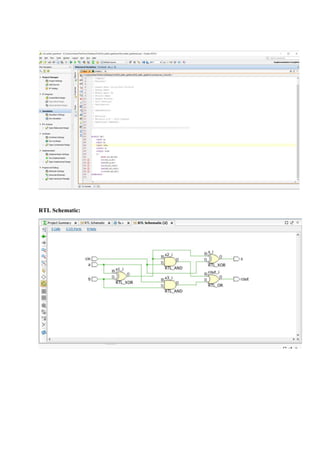

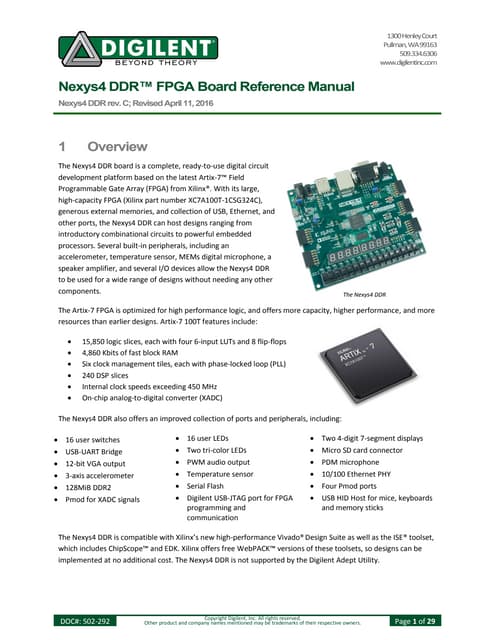

This document describes two different models for a full adder circuit - a dataflow model and a gate level model. The dataflow model uses assign statements to directly define the sum (s) and carry out (cout) outputs in terms of the inputs (a, b, cin). The gate level model builds the full adder using lower level logic gates like xor, and, or connected via internal wires to compute the sum and carry outputs.

1 of 6

Downloaded 21 times

Recommended

Verilog hdl

Verilog hdlMuhammad Uzair Rasheed

Ěý

Hardware description languages (HDLs) allow designers to describe digital systems at different levels of abstraction in a textual format. The two most commonly used HDLs are Verilog and VHDL. Verilog is commonly used in the US, while VHDL is more popular in Europe. HDLs enable simulation of designs before fabrication to verify functionality. Digital designs can be modeled at the gate level, data flow level, or behavioral level in Verilog. Verilog code consists of a design module and test bench module to stimulate inputs and observe outputs.Verilog

VerilogMohamed Rayan

Ěý

Those slides describe digital design using Verilog HDL,

starting with Design methodologies for any digital circuit then difference between s/w (C/C++) and H/w (Verilog) and the most important constructs that let us start hardware design using Verilog HDL.Fundamentals of Logic Design 6th Charles H.Roth.pdf

Fundamentals of Logic Design 6th Charles H.Roth.pdfMohsinNaushad1

Ěý

This document is the table of contents for the textbook "Fundamentals of Logic Design" by Charles H. Roth Jr. and Larry L. Kinney. It lists 20 units that cover topics such as number systems, Boolean algebra, logic gates, sequential circuits, VHDL, and digital design. The preface provides information about the authors and publisher. Brief descriptions of the chapters and sections are given to outline the scope and organization of the material presented in the book.Shannon-Fano algorithm

Shannon-Fano algorithmMANISH T I

Ěý

Shannon-Fano algorithm is a compression algorithms uses variable length coding in data compression methods.Verilog Tutorial - Verilog HDL Tutorial with Examples

Verilog Tutorial - Verilog HDL Tutorial with ExamplesE2MATRIX

Ěý

E2MATRIX Research Lab

Opp Phagwara Bus Stand, Backside Axis Bank,

Parmar Complex, Phagwara Punjab (India).

Contact : +91 9041262727

web: www.e2matrix.com -- email: support@e2matrix.com

Simulation tools typically accept full set of Verilog language constructs

Some language constructs and their use in a Verilog description make simulation efficient and are ignored by synthesis tools

Synthesis tools typically accept only a subset of the full Verilog language constructs

In this presentation, Verilog language constructs not supported in Synopsys FPGA Express are in red italics

There are other restrictions not detailed here, see [2].

The Module Concept

Basic design unit

Modules are:

Declared

Instantiated

Modules declarations cannot be nested

Digital Electronics Question Bank

Digital Electronics Question BankMathankumar S

Ěý

This document contains a question bank with multiple choice and short answer questions covering various topics in digital electronics across 5 units. Some of the key topics covered include binary, hexadecimal, octal number systems; logic gates and families (TTL, CMOS, ECL); flip-flops, counters, registers; basics of memory units (RAM, ROM); programmable logic devices (PLA, PLD); and asynchronous sequential circuits including hazards. The document is divided into parts for each unit with concepts ranging from introductory to advanced level questions.Combinational circuits

Combinational circuitsNabarun Chakraborty

Ěý

The document discusses digital circuits including combinational and sequential circuits. It describes various combinational logic circuits such as half adders, full adders, comparators, multiplexers, encoders, decoders. It also discusses sequential circuits and how they employ memory elements. Arithmetic circuits, binary adders, subtractors, and BCD to 7-segment decoders are explained in detail through diagrams and examples.Vhdl programming

Vhdl programmingYogesh Mashalkar

Ěý

This document provides examples of VHDL code for modeling basic logic gates and multiplexers. It begins with syntax for VHDL programs and then provides behavioral VHDL code for modeling common logic gates like AND, OR, NOR, NAND, XOR and XNOR gates. It also provides code for half adder, full adder, half subtractor and full subtractor. The document further contains VHDL code examples to model a 4-to-1 multiplexer and 1-to-4 demultiplexer using different types of statements like if-else, case, when-else and with-select.VLSI Lab manual PDF

VLSI Lab manual PDFUR11EC098

Ěý

The document describes the design and simulation of half adders, full adders, multiplexers, and demultiplexers using VHDL. It includes block diagrams, truth tables, and VHDL code for implementing these circuits using dataflow, behavioral, and structural modeling in Xilinx ISE. Code examples and output waveforms are provided for half adders, full adders, 4-to-1 multiplexers, and 1-to-4 demultiplexers. The aim is to learn how to design and simulate basic digital circuits using different VHDL modeling approaches.Analog to digital converters, adc

Analog to digital converters, adcSaumya Ranjan Behura

Ěý

1) The document discusses analog-to-digital converters (ADCs), including their basic function of converting continuous analog signals to discrete digital numbers.

2) It describes several types of ADCs - flash, successive approximation, dual slope, and delta-sigma - along with their relative speeds and costs.

3) The document then focuses on the ATD10B8C ADC present on the MC9S12C32 microcontroller, outlining its key features, registers, and how to set it up and use it to take single-channel or multi-channel conversions.Digital electronics logic families

Digital electronics logic familiesBLESSINAR0

Ěý

This document provides an overview of different digital logic families. It begins by introducing logic gates and integrated circuits. It then classifies logic families as either bipolar or unipolar, and lists examples of each. Key specifications of digital ICs are defined, including propagation delay, fan-in/fan-out, input/output logic levels, and noise margin. Transistor-transistor logic (TTL) and complementary metal-oxide-semiconductor (CMOS) circuits are described. The TTL NAND gate uses multiple emitter transistors while the CMOS NAND gate uses both P-channel and N-channel MOSFETs. Emitter-coupled logic (ECL) provides the fastestVERILOG CODE FOR Adder

VERILOG CODE FOR AdderRakesh kumar jha

Ěý

The document contains Verilog code for half adders and full adders. It provides two implementations for each: a half adder is implemented using either XOR and AND gates, or XOR and AND modules; a full adder is implemented using XOR, AND and OR gates arranged in a specific way to calculate the sum and carry outputs, or using XOR, AND and OR modules and a wire to decompose the calculation into steps.VLSI Testing Techniques

VLSI Testing TechniquesDr. A. B. Shinde

Ěý

This document discusses various VLSI testing techniques. It begins by explaining the need for testing circuits when they are first developed and manufactured to check that they meet specifications. The main testing approach is to apply test inputs and compare the outputs to expected patterns. It then describes different testing techniques for combinational and sequential circuits, including fault modeling, path sensitizing, scan path testing, built-in self-test (BIST), boundary scan testing, and signature analysis. Specific circuit examples are provided to illustrate scan path testing, BIST using linear feedback shift registers (LFSRs) and compressor circuits, and boundary scan testing.Pass Transistor Logic

Pass Transistor LogicSudhanshu Janwadkar

Ěý

This presentation discusses the basics of Pass Transistor Logic, its advantages, limitation and finally implementation of Boolean functions/Combinational Logic circuits using Pass Transistor Logic.Information Theory - Introduction

Information Theory - IntroductionBurdwan University

Ěý

The document discusses key concepts in information theory including information sources, entropy, channel capacity, and coding. It defines a discrete memoryless source as producing symbols randomly according to a probability distribution. Entropy is introduced as the average uncertainty or information per symbol from a source. Channel capacity is the maximum information rate that can be reliably transmitted over a channel and depends on factors like noise and error probability. Coding techniques can allow reliable communication at rates below the channel capacity.Intel 8051 Programming in C

Intel 8051 Programming in CSudhanshu Janwadkar

Ěý

This presentation gives the details about the data types available in Embedded C. It also discusses the pros and cons of writing codes in C for 8051. Different example codes are considered.DAC Interfacing with 8051.pdf

DAC Interfacing with 8051.pdfSrikrishna Thota

Ěý

This document discusses interfacing a digital-to-analog converter (DAC) with an 8051 microcontroller. It explains that a DAC is used to convert digital pulses from the 8051 into analog signals that can be read by systems requiring analog inputs. Specifically, it describes using an 8-bit DAC 0808 chip to convert digital data from the 8051 into a corresponding analog output voltage. It also provides 8051 assembly code examples to generate triangular and square wave outputs using a DAC interfaced with an 8051 port.Multipliers in VLSI

Multipliers in VLSIKiranmai Sony

Ěý

This document discusses various designs for digital multipliers. It begins by reviewing the basic building blocks used in digital circuits and how binary multiplication works by adding partial products. It then describes approaches for implementing multiplication, including right shift and add serial multipliers and faster parallel array and tree multipliers. Booth encoding is introduced as a technique to reduce the number of stages in a multiplier. Implementation details are provided for array and Wallace tree multipliers, including the use of compression cells like the (4,2) counter. Optimization goals for multipliers differ from adders in emphasizing reducing the critical path.Pn sequence

Pn sequenceDarshil Shah

Ěý

This document discusses pseudo-noise (PN) sequences, which are random-looking bit sequences that repeat periodically and have useful properties for applications like code division multiple access (CDMA) networks. It outlines a 15-stage PN generator using a shift register, describes the properties of equal probability of 1s and 0s and high auto-correlation. It also discusses how PN sequences are used for data detection through correlation and includes a MATLAB code example to generate a PN sequence.PPT ON Arduino

PPT ON Arduino Ravi Phadtare

Ěý

This presentation summarizes a summer training on Arduino. It defines Arduino as an open-source hardware and software platform for building electronics projects. It describes the main types of Arduino boards including the Arduino Uno, Mega 2560, Duemilanove, and Fio. It also outlines some key features of the Arduino Uno board. Furthermore, it provides examples of interfacing Arduino with a DC motor and RC car motor. The presentation concludes by listing some common applications of Arduino and its advantages.Design and development of carry select adder

Design and development of carry select adderABIN THOMAS

Ěý

DESIGN AND DEVELOPMENT OF DIFFERENT TYPE OF CARRY SELECT ADDER AND IMPLEMENTED USING VERING IN XILINX ISE 14.7 AND COMPARE THEM TO FIND EFFICIENT CSLAChap 6

Chap 6Tanuj Patel

Ěý

The document discusses different digital communication formats including unipolar RZ, NRZ, bipolar RZ, NRZ, split-phase Manchester, and polar quaternary NRZ. It provides examples of transmitting sample bit sequences using each format and drawing the corresponding waveforms. For one example, it also compares the bandwidth requirements of unipolar RZ, NRZ, bipolar RZ, and split-phase Manchester formats. The document contains solutions to exercises that involve drawing waveforms for transmitting data using the various formats.halfadder & halfsubtractor using 4:1 MUX

halfadder & halfsubtractor using 4:1 MUXU Reshmi

Ěý

This document discusses using a 4:1 multiplexer to create half adder and half subtractor combinational circuits. It defines half adders, half subtractors, and multiplexers. It then shows the logic diagrams and transistor-level implementations of half adders and half subtractors using a 4:1 multiplexer. The document concludes that combinational circuits like these produce outputs only based on present inputs and have no memory elements, resulting in no delay in producing outputs.Clippers AND Clampers

Clippers AND ClampersJUNAID SK

Ěý

This document describes the theory, circuit diagrams, and experimental procedures for studying clipping and clamping circuits using diodes. Clipping circuits are used to clip off portions of an input waveform above or below certain voltage levels. Clamping circuits add or subtract a DC voltage to a waveform without changing its shape. The document provides details on setting up series and shunt clipping circuits, as well as positive, negative, and double clipping circuits. It also covers positive, negative, and double clamping circuits and how they operate to clamp the input signal at different voltage levels. Procedures for observing input and output waveforms on an oscilloscope are included.Convolution codes - Coding/Decoding Tree codes and Trellis codes for multiple...

Convolution codes - Coding/Decoding Tree codes and Trellis codes for multiple...Madhumita Tamhane

Ěý

In contrast to block codes, Convolution coding scheme has an information frame together with previous m information frames encoded into a single code word frame, hence coupling successive code word frames. Convolution codes are most important Tree codes that satisfy certain additional linearity and time invariance properties. Decoding procedure is mainly devoted to correcting errors in first frame. The effect of these information symbols on subsequent code word frames can be computed and subtracted from subsequent code word frames. Hence in spite of infinitely long code words, computations can be arranged so that the effect of earlier frames, properly decoded, on the current frame is zero. Single Sideband Suppressed Carrier (SSB-SC)

Single Sideband Suppressed Carrier (SSB-SC)Muhammad Ridwanul Hoque

Ěý

Single-sideband suppressed carrier (SSB-SC) modulation improves spectral efficiency by transmitting only one sideband. It requires a bandwidth equal to the signal bandwidth. SSB-SC can be detected coherently using multiplication by the carrier. Quadrature amplitude modulation (QAM) transmits two baseband signals over the same bandwidth using in-phase and quadrature carriers that are 90 degrees out of phase. Vestigial sideband (VSB) modulation is a compromise between DSB and SSB that inherits advantages of both while requiring only slightly greater bandwidth than SSB. It is used for broadcast television transmission.Interfacing Stepper motor with 8051

Interfacing Stepper motor with 8051Pantech ProLabs India Pvt Ltd

Ěý

The document discusses interfacing a stepper motor with an 8051 microcontroller. A stepper motor can divide a full rotation into discrete steps through energizing coils in different sequences. The stepper motor can be interfaced with an 8051 using an L293D motor driver connected to ports P1.0, P1.2, P1.3, and P1.4 of the 8051. Both full-step and half-step sequences are described for energizing the coils to precisely control the motor's position without feedback. Assembly and C code examples are provided to demonstrate clockwise and counterclockwise rotation of the stepper motor connected to the 8051.Discrete Fourier Transform

Discrete Fourier TransformAbhishek Choksi

Ěý

This document summarizes key aspects of the discrete Fourier transform (DFT). It defines the DFT, provides the formula for calculating it, and explains that the DFT transforms a discrete-time signal from the time domain to the frequency domain. It also outlines several important properties of the DFT, including linearity, shift property, duality, symmetry, and circular convolution. Examples are provided to illustrate duality and symmetry. References for further information on the discrete Fourier transform are also included.Enabling SSL Elasticsearch on server

Enabling SSL Elasticsearch on serverOmkar Rane

Ěý

This document provides steps to enable SSL/HTTPS for an Elasticsearch server. It involves generating certificates, configuring Elasticsearch, and enabling TLS for both transport and HTTP layers. The process includes generating a CA certificate, creating node certificates signed by the CA, editing the Elasticsearch configuration file, and restarting Elasticsearch to enable HTTPS.Anti lock braking (ABS) Model based Design in MATLAB-Simulink

Anti lock braking (ABS) Model based Design in MATLAB-SimulinkOmkar Rane

Ěý

This document describes the modeling and simulation of an anti-lock braking system (ABS) using Simulink. It includes models of vehicle dynamics, wheel dynamics, and a simplified ABS controller. The vehicle model accounts for mass, friction forces, and acceleration. The wheel model includes torque from braking and friction. Simulation results show wheel slip and stopping distance with and without the ABS controller engaged. The ABS system helps maintain optimal slip to minimize stopping distance.More Related Content

What's hot (20)

VLSI Lab manual PDF

VLSI Lab manual PDFUR11EC098

Ěý

The document describes the design and simulation of half adders, full adders, multiplexers, and demultiplexers using VHDL. It includes block diagrams, truth tables, and VHDL code for implementing these circuits using dataflow, behavioral, and structural modeling in Xilinx ISE. Code examples and output waveforms are provided for half adders, full adders, 4-to-1 multiplexers, and 1-to-4 demultiplexers. The aim is to learn how to design and simulate basic digital circuits using different VHDL modeling approaches.Analog to digital converters, adc

Analog to digital converters, adcSaumya Ranjan Behura

Ěý

1) The document discusses analog-to-digital converters (ADCs), including their basic function of converting continuous analog signals to discrete digital numbers.

2) It describes several types of ADCs - flash, successive approximation, dual slope, and delta-sigma - along with their relative speeds and costs.

3) The document then focuses on the ATD10B8C ADC present on the MC9S12C32 microcontroller, outlining its key features, registers, and how to set it up and use it to take single-channel or multi-channel conversions.Digital electronics logic families

Digital electronics logic familiesBLESSINAR0

Ěý

This document provides an overview of different digital logic families. It begins by introducing logic gates and integrated circuits. It then classifies logic families as either bipolar or unipolar, and lists examples of each. Key specifications of digital ICs are defined, including propagation delay, fan-in/fan-out, input/output logic levels, and noise margin. Transistor-transistor logic (TTL) and complementary metal-oxide-semiconductor (CMOS) circuits are described. The TTL NAND gate uses multiple emitter transistors while the CMOS NAND gate uses both P-channel and N-channel MOSFETs. Emitter-coupled logic (ECL) provides the fastestVERILOG CODE FOR Adder

VERILOG CODE FOR AdderRakesh kumar jha

Ěý

The document contains Verilog code for half adders and full adders. It provides two implementations for each: a half adder is implemented using either XOR and AND gates, or XOR and AND modules; a full adder is implemented using XOR, AND and OR gates arranged in a specific way to calculate the sum and carry outputs, or using XOR, AND and OR modules and a wire to decompose the calculation into steps.VLSI Testing Techniques

VLSI Testing TechniquesDr. A. B. Shinde

Ěý

This document discusses various VLSI testing techniques. It begins by explaining the need for testing circuits when they are first developed and manufactured to check that they meet specifications. The main testing approach is to apply test inputs and compare the outputs to expected patterns. It then describes different testing techniques for combinational and sequential circuits, including fault modeling, path sensitizing, scan path testing, built-in self-test (BIST), boundary scan testing, and signature analysis. Specific circuit examples are provided to illustrate scan path testing, BIST using linear feedback shift registers (LFSRs) and compressor circuits, and boundary scan testing.Pass Transistor Logic

Pass Transistor LogicSudhanshu Janwadkar

Ěý

This presentation discusses the basics of Pass Transistor Logic, its advantages, limitation and finally implementation of Boolean functions/Combinational Logic circuits using Pass Transistor Logic.Information Theory - Introduction

Information Theory - IntroductionBurdwan University

Ěý

The document discusses key concepts in information theory including information sources, entropy, channel capacity, and coding. It defines a discrete memoryless source as producing symbols randomly according to a probability distribution. Entropy is introduced as the average uncertainty or information per symbol from a source. Channel capacity is the maximum information rate that can be reliably transmitted over a channel and depends on factors like noise and error probability. Coding techniques can allow reliable communication at rates below the channel capacity.Intel 8051 Programming in C

Intel 8051 Programming in CSudhanshu Janwadkar

Ěý

This presentation gives the details about the data types available in Embedded C. It also discusses the pros and cons of writing codes in C for 8051. Different example codes are considered.DAC Interfacing with 8051.pdf

DAC Interfacing with 8051.pdfSrikrishna Thota

Ěý

This document discusses interfacing a digital-to-analog converter (DAC) with an 8051 microcontroller. It explains that a DAC is used to convert digital pulses from the 8051 into analog signals that can be read by systems requiring analog inputs. Specifically, it describes using an 8-bit DAC 0808 chip to convert digital data from the 8051 into a corresponding analog output voltage. It also provides 8051 assembly code examples to generate triangular and square wave outputs using a DAC interfaced with an 8051 port.Multipliers in VLSI

Multipliers in VLSIKiranmai Sony

Ěý

This document discusses various designs for digital multipliers. It begins by reviewing the basic building blocks used in digital circuits and how binary multiplication works by adding partial products. It then describes approaches for implementing multiplication, including right shift and add serial multipliers and faster parallel array and tree multipliers. Booth encoding is introduced as a technique to reduce the number of stages in a multiplier. Implementation details are provided for array and Wallace tree multipliers, including the use of compression cells like the (4,2) counter. Optimization goals for multipliers differ from adders in emphasizing reducing the critical path.Pn sequence

Pn sequenceDarshil Shah

Ěý

This document discusses pseudo-noise (PN) sequences, which are random-looking bit sequences that repeat periodically and have useful properties for applications like code division multiple access (CDMA) networks. It outlines a 15-stage PN generator using a shift register, describes the properties of equal probability of 1s and 0s and high auto-correlation. It also discusses how PN sequences are used for data detection through correlation and includes a MATLAB code example to generate a PN sequence.PPT ON Arduino

PPT ON Arduino Ravi Phadtare

Ěý

This presentation summarizes a summer training on Arduino. It defines Arduino as an open-source hardware and software platform for building electronics projects. It describes the main types of Arduino boards including the Arduino Uno, Mega 2560, Duemilanove, and Fio. It also outlines some key features of the Arduino Uno board. Furthermore, it provides examples of interfacing Arduino with a DC motor and RC car motor. The presentation concludes by listing some common applications of Arduino and its advantages.Design and development of carry select adder

Design and development of carry select adderABIN THOMAS

Ěý

DESIGN AND DEVELOPMENT OF DIFFERENT TYPE OF CARRY SELECT ADDER AND IMPLEMENTED USING VERING IN XILINX ISE 14.7 AND COMPARE THEM TO FIND EFFICIENT CSLAChap 6

Chap 6Tanuj Patel

Ěý

The document discusses different digital communication formats including unipolar RZ, NRZ, bipolar RZ, NRZ, split-phase Manchester, and polar quaternary NRZ. It provides examples of transmitting sample bit sequences using each format and drawing the corresponding waveforms. For one example, it also compares the bandwidth requirements of unipolar RZ, NRZ, bipolar RZ, and split-phase Manchester formats. The document contains solutions to exercises that involve drawing waveforms for transmitting data using the various formats.halfadder & halfsubtractor using 4:1 MUX

halfadder & halfsubtractor using 4:1 MUXU Reshmi

Ěý

This document discusses using a 4:1 multiplexer to create half adder and half subtractor combinational circuits. It defines half adders, half subtractors, and multiplexers. It then shows the logic diagrams and transistor-level implementations of half adders and half subtractors using a 4:1 multiplexer. The document concludes that combinational circuits like these produce outputs only based on present inputs and have no memory elements, resulting in no delay in producing outputs.Clippers AND Clampers

Clippers AND ClampersJUNAID SK

Ěý

This document describes the theory, circuit diagrams, and experimental procedures for studying clipping and clamping circuits using diodes. Clipping circuits are used to clip off portions of an input waveform above or below certain voltage levels. Clamping circuits add or subtract a DC voltage to a waveform without changing its shape. The document provides details on setting up series and shunt clipping circuits, as well as positive, negative, and double clipping circuits. It also covers positive, negative, and double clamping circuits and how they operate to clamp the input signal at different voltage levels. Procedures for observing input and output waveforms on an oscilloscope are included.Convolution codes - Coding/Decoding Tree codes and Trellis codes for multiple...

Convolution codes - Coding/Decoding Tree codes and Trellis codes for multiple...Madhumita Tamhane

Ěý

In contrast to block codes, Convolution coding scheme has an information frame together with previous m information frames encoded into a single code word frame, hence coupling successive code word frames. Convolution codes are most important Tree codes that satisfy certain additional linearity and time invariance properties. Decoding procedure is mainly devoted to correcting errors in first frame. The effect of these information symbols on subsequent code word frames can be computed and subtracted from subsequent code word frames. Hence in spite of infinitely long code words, computations can be arranged so that the effect of earlier frames, properly decoded, on the current frame is zero. Single Sideband Suppressed Carrier (SSB-SC)

Single Sideband Suppressed Carrier (SSB-SC)Muhammad Ridwanul Hoque

Ěý

Single-sideband suppressed carrier (SSB-SC) modulation improves spectral efficiency by transmitting only one sideband. It requires a bandwidth equal to the signal bandwidth. SSB-SC can be detected coherently using multiplication by the carrier. Quadrature amplitude modulation (QAM) transmits two baseband signals over the same bandwidth using in-phase and quadrature carriers that are 90 degrees out of phase. Vestigial sideband (VSB) modulation is a compromise between DSB and SSB that inherits advantages of both while requiring only slightly greater bandwidth than SSB. It is used for broadcast television transmission.Interfacing Stepper motor with 8051

Interfacing Stepper motor with 8051Pantech ProLabs India Pvt Ltd

Ěý

The document discusses interfacing a stepper motor with an 8051 microcontroller. A stepper motor can divide a full rotation into discrete steps through energizing coils in different sequences. The stepper motor can be interfaced with an 8051 using an L293D motor driver connected to ports P1.0, P1.2, P1.3, and P1.4 of the 8051. Both full-step and half-step sequences are described for energizing the coils to precisely control the motor's position without feedback. Assembly and C code examples are provided to demonstrate clockwise and counterclockwise rotation of the stepper motor connected to the 8051.Discrete Fourier Transform

Discrete Fourier TransformAbhishek Choksi

Ěý

This document summarizes key aspects of the discrete Fourier transform (DFT). It defines the DFT, provides the formula for calculating it, and explains that the DFT transforms a discrete-time signal from the time domain to the frequency domain. It also outlines several important properties of the DFT, including linearity, shift property, duality, symmetry, and circular convolution. Examples are provided to illustrate duality and symmetry. References for further information on the discrete Fourier transform are also included.More from Omkar Rane (20)

Enabling SSL Elasticsearch on server

Enabling SSL Elasticsearch on serverOmkar Rane

Ěý

This document provides steps to enable SSL/HTTPS for an Elasticsearch server. It involves generating certificates, configuring Elasticsearch, and enabling TLS for both transport and HTTP layers. The process includes generating a CA certificate, creating node certificates signed by the CA, editing the Elasticsearch configuration file, and restarting Elasticsearch to enable HTTPS.Anti lock braking (ABS) Model based Design in MATLAB-Simulink

Anti lock braking (ABS) Model based Design in MATLAB-SimulinkOmkar Rane

Ěý

This document describes the modeling and simulation of an anti-lock braking system (ABS) using Simulink. It includes models of vehicle dynamics, wheel dynamics, and a simplified ABS controller. The vehicle model accounts for mass, friction forces, and acceleration. The wheel model includes torque from braking and friction. Simulation results show wheel slip and stopping distance with and without the ABS controller engaged. The ABS system helps maintain optimal slip to minimize stopping distance.Autosar fundamental

Autosar fundamentalOmkar Rane

Ěý

The document discusses Autosar's layered architecture and communication capabilities. It describes the layered architecture with basic software, runtime environment and application layers. The runtime environment implements a virtual function bus to allow software components to communicate within and across ECUs. Communication can be intra-ECU, inter-ECU, or inter-partition. The runtime environment uses services like AUTOSAR COM and IOC to enable different types of communication.Stress Management

Stress ManagementOmkar Rane

Ěý

The document discusses stress, its causes and effects, and strategies for managing stress. It defines stress as the body's response to any physical or mental demand, which can be triggered by events or thoughts that make one feel frustrated, angry or nervous. Both moderate and excessive stress can impact one's physical and emotional health negatively. While stress is a normal experience, anxiety involves worrying and affects one's lifestyle longer term. The document recommends stress management techniques like relaxation exercises, physical activity, meditation and counseling to improve physical, emotional and cognitive functioning.Bootloaders (U-Boot)

Bootloaders (U-Boot) Omkar Rane

Ěý

This document discusses bootloaders for embedded systems. It defines a bootloader as the first code executed after a system powers on or resets that is responsible for loading the operating system kernel. The document then describes the tasks of a bootloader like initializing hardware, loading binaries from storage, and providing a shell. It outlines the booting process differences between desktops and embedded systems. Finally, it focuses on the universal bootloader U-Boot, describing its directory structure, configuration, building process, and commands.Concept of Diversity & Fading (wireless communication)

Concept of Diversity & Fading (wireless communication)Omkar Rane

Ěý

This document discusses concepts related to fading and diversity in wireless communication systems. It introduces fading as signal variations caused by multipath interference from multiple signal propagation paths. It describes two types of fading: large-scale fading due to path loss and shadowing, and small-scale fading which includes fast fading due to mobility and slow fading due to shadowing. It also discusses different diversity techniques that can be used to combat fading, including space, polarization, frequency and time diversity.Tata Motors GDC .LTD Internship

Tata Motors GDC .LTD Internship Omkar Rane

Ěý

The document describes several projects completed as part of a semester-long internship at Tata Motors. The projects include:

1. Developing a vendor chatbot using Rasa and Telegram APIs to provide invoice information to users. NLP techniques were used to extract intent and entities.

2. Creating a dashboard using HTML, CSS, and Flask for employee health monitoring.

3. Building a system to automatically add new employee data from Excel files to an AWS RDS database to then be viewed on a dashboard.

4. Deploying projects to AWS EC2 and RDS instances.

5. Working on a contract lifecycle management dashboard for Tata Motors using various technologies.Machine Learning Model for M.S admissions

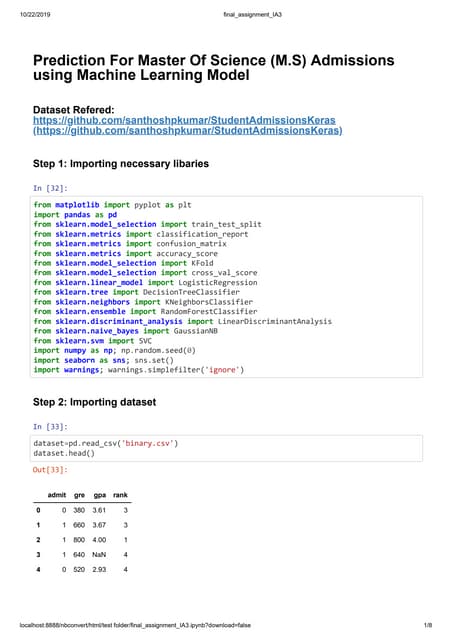

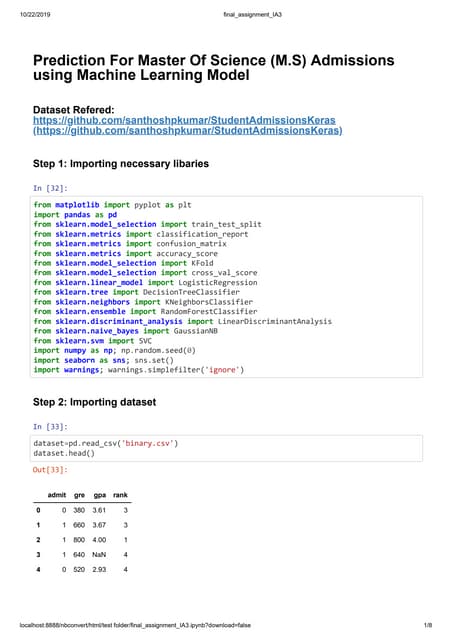

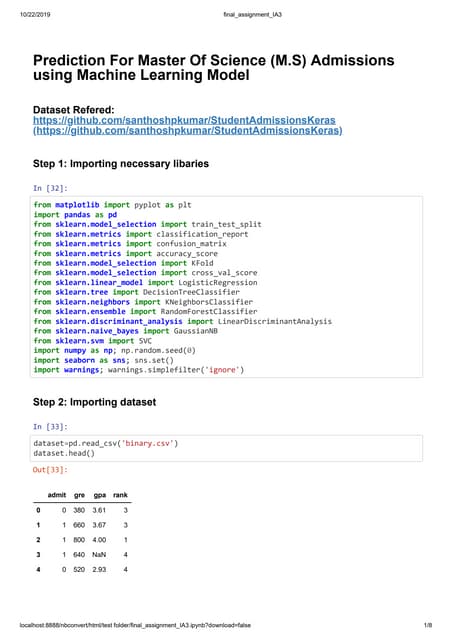

Machine Learning Model for M.S admissionsOmkar Rane

Ěý

The document describes building a machine learning model to predict admissions for a Master's program. It loads student data, preprocesses it by imputing missing values, splits it into training and test sets, trains several models and evaluates their accuracy via cross-validation. Logistic regression achieved the best results with 77.5% accuracy. The trained logistic regression model is used to make predictions on new student data.Timer 0 programming on LPC 1768

Timer 0 programming on LPC 1768Omkar Rane

Ěý

The document defines a function called DelayMs that uses Timer0 to create delays in milliseconds. It initializes Timer0 to increment every 12,000 clock cycles, which at a clock speed of 12MHz equals 1ms. The main function blinks an LED by turning it on for 500ms, then off for 500ms in a continuous loop using the DelayMs function.ADC (Analog to Digital conversion) using LPC 1768

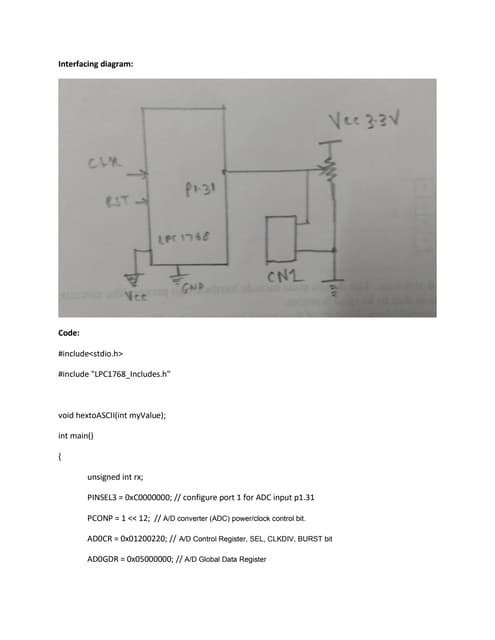

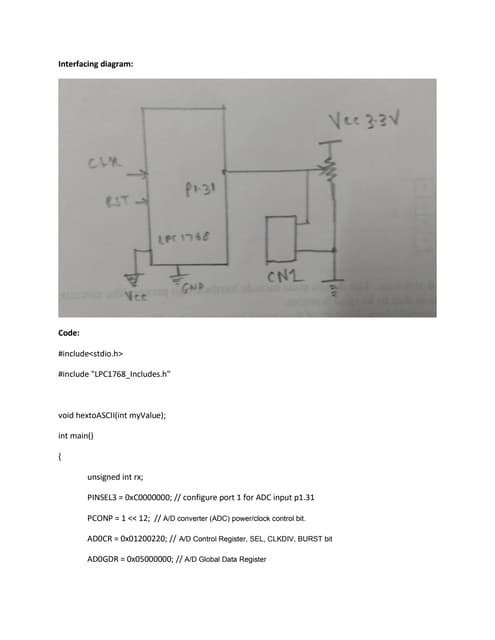

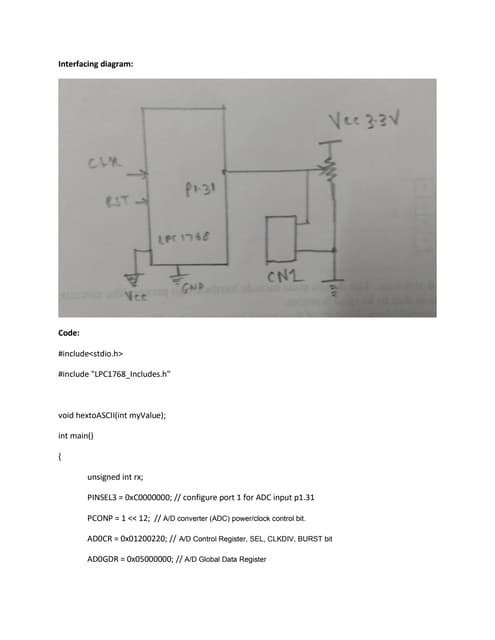

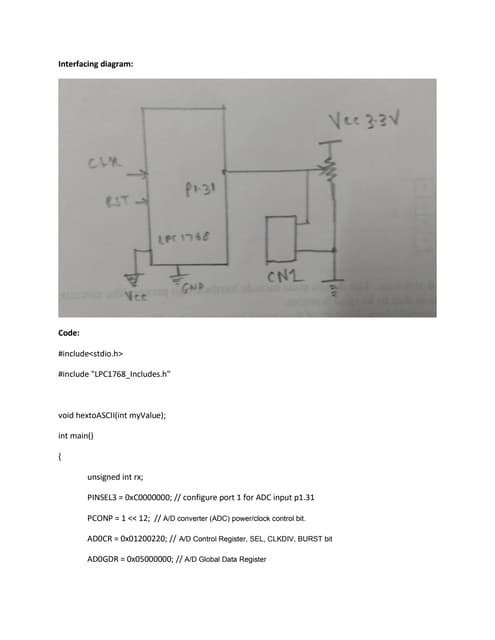

ADC (Analog to Digital conversion) using LPC 1768Omkar Rane

Ěý

This document contains code for an interfacing diagram that converts analog to digital values and displays the output in hexadecimal on an LCD screen. The code configures the ADC and UART ports, performs an analog to digital conversion on an input voltage, converts the output to hexadecimal, and transmits the values over UART. It also contains calculations for the step size of the ADC based on the reference voltage and bits. An observation table shows theoretical and measured output values for different input voltages.PWM based motor speed control using LPC 1768

PWM based motor speed control using LPC 1768Omkar Rane

Ěý

This code configures the LPC1768 microcontroller's PWM peripheral to generate a pulse width modulated signal on pin PWM1.5. It initializes the PWM timer and match registers, enables the PWM output, and then uses a for loop to incrementally change the duty cycle of the PWM signal from 10% to 100% over 10 steps, pausing 1 second between each step. This allows the user to see the PWM output change frequency smoothly over time.UART interfacing on LPC1768 (Cortex M3 micro controller)

UART interfacing on LPC1768 (Cortex M3 micro controller)Omkar Rane

Ěý

This code configures the UART0 port on an LPC1768 microcontroller to communicate at 9600 baud. It sets the pin configuration for transmit and receive, enables the FIFO and clears flags. It then configures the baud rate divisor, character length, parity and stop bits. The code enters a loop to continuously read incoming serial data and echo it back on the transmit line.LED Blinking logic on LPC1768

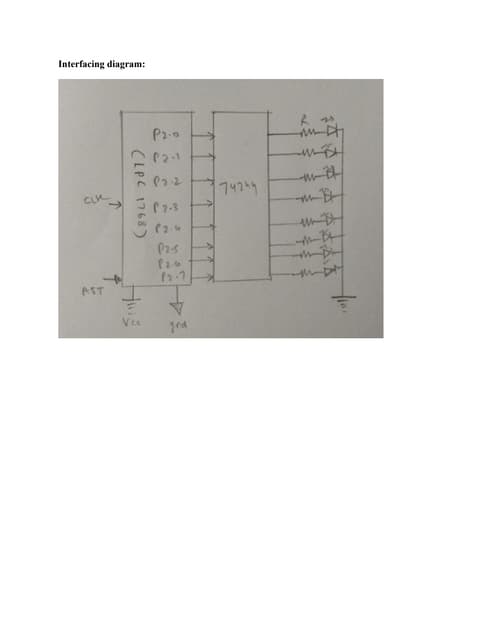

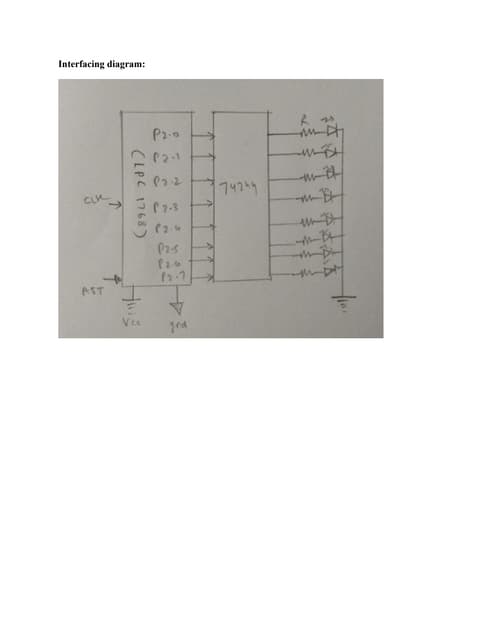

LED Blinking logic on LPC1768Omkar Rane

Ěý

This document provides an interfacing diagram and code for an LPC1768 microcontroller to toggle a set of GPIO pins. The code uses PINSEL4 and FIO2DIR registers to configure pins P0.2 to P0.7 as GPIO outputs. It then uses a for loop to toggle all the pins high and low by setting and clearing the FIO2SET and FIO2CLR registers respectively.CAN interfacing on LPC1768 (ARM Cortex M3 based Micro controller)

CAN interfacing on LPC1768 (ARM Cortex M3 based Micro controller)Omkar Rane

Ěý

The document describes code for initializing and transmitting messages over a CAN bus on an LPC1768 microcontroller, including initializing the CAN controller, setting an acceptance filter to define which message IDs will be received, and sending a test message over CAN1 while monitoring reception on CAN2. Functions are defined for CAN initialization, setting the acceptance filter, and transmitting messages with given IDs and data over CAN1.Vlisi Course project presentation:Keypad Scanner

Vlisi Course project presentation:Keypad ScannerOmkar Rane

Ěý

This document describes a keypad scanner project implemented on an FPGA board. It includes the truth table and equations for scanning the keys of a 3x4 keypad to drive 4 LEDs. The Verilog code implements this design using logic gates and assigns statements. The code was submitted by 3 students for their VLSI design course, overseen by instructor Dr. Dipti Sakhare. References on Verilog, digital design, and the FPGA board used are also listed.VlSI course project report : Keypad Scanner

VlSI course project report : Keypad Scanner Omkar Rane

Ěý

This project report describes the design, simulation, and implementation of a keypad scanner on an FPGA board. A Verilog code was written using a dataflow modeling style to scan a 3x4 keypad and output a 5-bit binary number corresponding to the pressed key. The code was simulated using Xilinx Vivado software. Finally, the design was implemented on a Digilent Nexys ddr FPGA board and tested successfully.LPC 1768 A study on Real Time clock features

LPC 1768 A study on Real Time clock featuresOmkar Rane

Ěý

The document discusses the real-time clock (RTC) and backup registers for the LPC176x/5x microcontroller. It describes the RTC oscillator, clock control register, time counter registers, consolidated time registers, and steps for using the RTC including initializing, setting date and time, and reading date and time. Potential applications mentioned include a digital clock, timer controller, and data logging systems.Nexys4ddr rm FPGA board Datasheet

Nexys4ddr rm FPGA board DatasheetOmkar Rane

Ěý

This document provides an overview and reference manual for the Nexys4 DDR FPGA board. It describes the board's features such as the Artix-7 FPGA, memory resources, ports, and peripherals. It also provides details on power supplies, FPGA configuration options, and migrating designs from the original Nexys4 board. The manual is intended to help users understand and utilize the capabilities of the Nexys4 DDR board.Linear Regression (Machine Learning)

Linear Regression (Machine Learning)Omkar Rane

Ěý

The document discusses linear regression for predicting salary based on years of experience. It introduces gradient descent for linear regression, which iteratively updates the slope and intercept parameters (θ1 and θ2) to minimize cost and improve predictions. Gradient descent takes steps in the direction of the steepest descent down the cost function landscape. The learning rate determines step sizes and must be optimized for accurate predictions within a reasonable time.transmission gate based design for 2:1 Multiplexer in micro-wind

transmission gate based design for 2:1 Multiplexer in micro-windOmkar Rane

Ěý

2:1 Multiplexer using Transmission Gate in Microwind.Recently uploaded (20)

applicationof differential equation.pptx

applicationof differential equation.pptxPPSTUDIES

Ěý

irst-order differential equations find applications in modeling various phenomena, including growth and decay processes, Newton's law of cooling, electrical circuits, falling body problems, and mixing problems. Water Industry Process Automation & Control Monthly - April 2025

Water Industry Process Automation & Control Monthly - April 2025Water Industry Process Automation & Control

Ěý

Welcome to the April 2025 edition of WIPAC Monthly, the magazine brought to you by the LInkedIn Group Water Industry Process Automation & Control.

In this month's issue, along with all of the industries news we have a number of great articles for your edification

The first article is my annual piece looking behind the storm overflow numbers that are published each year to go into a bit more depth and look at what the numbers are actually saying.

The second article is a taster of what people will be seeing at the SWAN Annual Conference next month in Berlin and looks at the use of fibre-optic cable for leak detection and how its a technology we should be using more of

The third article, by Rob Stevens, looks at what the options are for the Continuous Water Quality Monitoring that the English Water Companies will be installing over the next year and the need to ensure that we install the right technology from the start.

Hope you enjoy the current edition,

OliverUHV UNIT-5 IMPLICATIONS OF THE ABOVE HOLISTIC UNDERSTANDING OF HARMONY ON ...

UHV UNIT-5 IMPLICATIONS OF THE ABOVE HOLISTIC UNDERSTANDING OF HARMONY ON ...ariomthermal2031

Ěý

IMPLICATIONS OF THE ABOVE HOLISTIC UNDERSTANDING OF HARMONY ON PROFESSIONAL ETHICS Virtual Power plants-Cleantech-Revolution

Virtual Power plants-Cleantech-RevolutionAshoka Saket

Ěý

VPPs are virtual aggregations of distributed energy resources, such as energy storage, solar panels, and wind turbines, that can be controlled and optimized in real-time to provide grid services.Distillation Types & It's Applications 1-Mar-2025.pptx

Distillation Types & It's Applications 1-Mar-2025.pptxmrcr123

Ěý

Distillation is a widely used method for separating mixturesĚýbased on differences in the conditions required to change theĚýphase of components of the mixture.

To separate a mixture of liquids, the liquid can be heated to force components, which have different boiling points, into the gas phase. The gas is then condensed back into liquid form and collected.

Distillation can be considered as a physical separation process not a chemical reaction.

Distillation involves selective evaporation and subsequent condensation of a component in a liquid mixture.

It is a separation technique that can be used to either increase the concentration of a particular component in the mixture or to obtain (almost) pure components from the mixture.

Under a given pressure, the temperature at which a pure liquid distills (or boils) is known as “ Boiling Point “.

Technically, the boiling point of a liquid is the temperature at which the vapor pressure of a liquid equals to the surrounding atmospheric pressure, allowing bubbles of vapor to form and rise through the liquid.Ěý

Distillation allows one of the liquid mixture's components into a gaseous state, taking advantage of the difference in their boiling points.

Artificial intelligence and Machine learning in remote sensing and GIS

Artificial intelligence and Machine learning in remote sensing and GISamirthamm2083

Ěý

Artificial intelligence and Machine learning in remote sensing and GIS Machine Elements in Mechanical Design.pdf

Machine Elements in Mechanical Design.pdfSLatorreAndrs

Ěý

Elementos importantes para el diseño de elementos mecánicosTelehealth technology – A new horizon in health care

Telehealth technology – A new horizon in health careDr INBAMALAR T M

Ěý

Telehealth technology – A new horizon in health care, Telemedicine, E-healthPrivilege Escalation Techniques and methodology.pdf

Privilege Escalation Techniques and methodology.pdfharshvikramshahi2

Ěý

Consolidated 40 different ways to escalate privilege Scalling Rails: The Journey to 200M Notifications

Scalling Rails: The Journey to 200M NotificationsGustavo Araujo

Ěý

Talk presented at Tropical On Rails.Knowledge-Based Agents in AI: Principles, Components, and Functionality

Knowledge-Based Agents in AI: Principles, Components, and FunctionalityRashmi Bhat

Ěý

This PowerPoint presentation provides an in-depth exploration of Knowledge-Based Agents (KBAs) in Artificial Intelligence (AI). It explains how these agents make decisions using stored knowledge and logical reasoning rather than direct sensor input. The presentation covers key components such as the Knowledge Base (KB), Inference Engine, Perception, and Action Execution.

Key topics include:

âś… Definition and Working Mechanism of Knowledge-Based Agents

âś… The Process of TELL, ASK, and Execution in AI Agents

âś… Representation of Knowledge and Decision-Making Approaches

âś… Logical Inference and Rule-Based Reasoning

âś… Applications of Knowledge-Based Agents in Real-World AI

This PPT is useful for students, educators, and AI enthusiasts who want to understand how intelligent agents operate using stored knowledge and logic-based inference. The slides are well-structured with explanations, examples, and an easy-to-follow breakdown of AI agent functions.Airport Components Part1 ppt.pptx-Site layout,RUNWAY,TAXIWAY,TAXILANE

Airport Components Part1 ppt.pptx-Site layout,RUNWAY,TAXIWAY,TAXILANEPriyanka Dange

Ěý

RUNWAY,TAXIWAY,TAXILANEUHV Unit - 4 HARMONY IN THE NATURE AND EXISTENCE.pptx

UHV Unit - 4 HARMONY IN THE NATURE AND EXISTENCE.pptxariomthermal2031

Ěý

HARMONY IN THE NATURE AND EXISTENCE Why the Engineering Model is Key to Successful Projects

Why the Engineering Model is Key to Successful ProjectsMaadhu Creatives-Model Making Company

Ěý

In this PDF document, the importance of engineering models in successful project execution is discussed. It explains how these models enhance visualization, planning, and communication. Engineering models help identify potential issues early, reducing risks and costs. Ultimately, they improve collaboration and client satisfaction by providing a clear representation of the project.Intro of Airport Engg..pptx-Definition of airport engineering and airport pla...

Intro of Airport Engg..pptx-Definition of airport engineering and airport pla...Priyanka Dange

Ěý

Definition of airport engineering and airport planning, Types of surveys required for airport site, Factors affecting the selection of site for AirportWater Industry Process Automation & Control Monthly - April 2025

Water Industry Process Automation & Control Monthly - April 2025Water Industry Process Automation & Control

Ěý

Verilog full adder in dataflow & gate level modelling style.

- 1. Full Adder in Dataflow model: Code: module fulladder( input a, input b, input cin, output s, output cout ); assign s=a^b^cin; assign cout=(a & b) | cin & (a ^ b); endmodule Output:

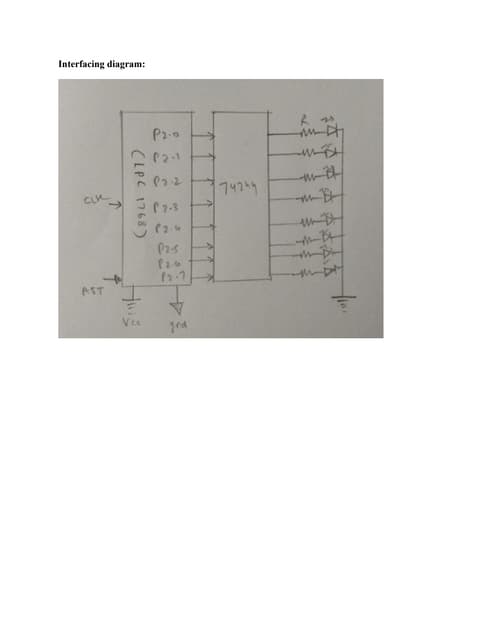

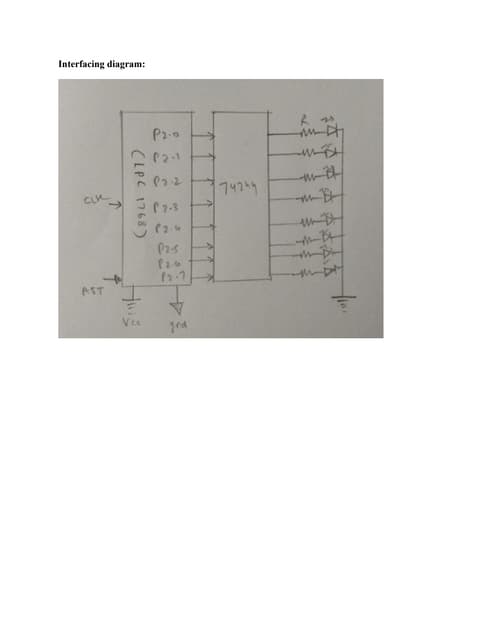

- 3. Hardware:

- 5. Full Adder in Gate level model : Code: module fa( input a, input b, input cin, output s, output cout ); wire x1,x2,x3; xor(x1,a,b); and(x3,a,b); xor(s,x1,cin); and(x2,x1,cin); or(cout,x2,x3); endmodule Output: