Vhdl

Download as PPTX, PDF1 like457 views

VHDL is a hardware description language used to model electronic systems. It allows describing a system's behavior and structure which can then be synthesized into an actual integrated circuit. VHDL has capabilities for simulation, synthesis, and modeling at different levels of abstraction. The basic structure of a VHDL program includes libraries, entities to declare inputs and outputs, and architectures to describe the design behavior.

1 of 22

Download to read offline

![Architecture

’āÆ Description of how the circuit should behave

’āÆ Syntax

’āÆ Two parts:

’āÉDeclarative part (optional): signals and

constants are declared here

’āÉCode part

ARCHITECTURE architecture_name OF entity_name IS

[declaration]

BEGIN

(code)

END architecture_name;

ChipA

B

C

D

EX

Y](https://image.slidesharecdn.com/vhdl-171129112940/85/Vhdl-11-320.jpg)

Recommended

Spdas2 vlsibput

Spdas2 vlsibputGIET,Bhubaneswar

╠²

VHDL is a hardware description language used to model and design digital circuits. It can be used for simulation, synthesis, and verification of circuits. VHDL has different language elements like entities, architectures, processes, and packages that allow modeling at different levels of abstraction like behavioral, dataflow, and structural. Common data types in VHDL include std_logic, std_logic_vector, and integers. VHDL supports modeling concurrency using processes and signal assignments.vhdl

vhdlNAGASAI547

╠²

VHDL is a hardware description language used to design digital systems. It allows systems to be modeled at different levels of abstraction like behavioral and structural. The behavioral model describes a system's behavior as inputs and outputs, while the structural model shows how system components are interconnected. VHDL uses entities to define a system's ports and architectures to describe its structure or behavior. Examples show implementing a half adder using behavioral and structural modeling in VHDL.Short.course.introduction.to.vhdl for beginners

Short.course.introduction.to.vhdl for beginners Ravi Sony

╠²

This document provides an introduction to VHDL (VHSIC Hardware Description Language). It discusses modeling and different levels of abstraction in modeling. It describes the design flow from idea to fabrication. It gives examples of architectural design, data path design, control path design, and register allocation. It discusses high-level synthesis and the tasks of scheduling and allocation. Finally, it provides some historical context and applications of hardware description languages.Introduction to VHDL

Introduction to VHDLFarzan Dehbashi

╠²

This document provides an introduction to VHDL (VHSIC Hardware Description Language). It discusses the history of VHDL and how it is based on ADA. It describes some key elements of VHDL including entities, architectures, components, and instantiation. Entities define the interface, architectures provide the implementation, and components allow for modular hierarchical design. The document also discusses structural modeling in VHDL using components, with examples of how to declare components and instantiate them by mapping ports.Vhdl

Vhdlvandanamalode

╠²

The document discusses VHDL (VHSIC Hardware Description Language) and provides information on various topics related to VHDL such as the design flow, levels of abstraction, types of HDLs, comparing VHDL and Verilog, simulation vs. synthesis, logic simulation, motivation for mixed-signal microelectronics, viewing designs by chip technology, concepts of modules and chips, levels of abstraction, types of VHDL, comparing VHDL and Verilog, choosing an HDL, the IEEE standard 1164, entities, architectures, and data objects in VHDL like constants, signals, and variables.VHDL-Behavioral-Programs-Structure of VHDL

VHDL-Behavioral-Programs-Structure of VHDLRevathi Subramaniam

╠²

The document discusses the structure and behavioral modeling of VHDL. It explains the main components of VHDL structure including entity, architecture, package, and configuration. It provides examples of how to write behavioral models for half adder, full adder, AND gate, and D flip flop in VHDL. The document concludes with references for further reading on VHDL design. VHDL summer training (ppt)

VHDL summer training (ppt)HoneyKumar34

╠²

This document provides an overview of VHDL (VHSIC Hardware Description Language). It defines HDL as a language used to describe the functionality of digital circuits. It explains that VHDL is used for designing complex digital circuits since drawing them by hand is not scalable. The document then discusses the history, capabilities, and design flow of VHDL. It compares VHDL to C language and describes different modeling styles in VHDL including structural, dataflow, behavioral, and mixed modeling. Key design units in VHDL like entity, architecture, configuration, and packages are also summarized.VHDL

VHDLAmit Kumar Rathi

╠²

VHDL is a hardware description language used to model digital circuits at different levels of abstraction. It can be used for simulation, synthesis and verification of digital hardware. VHDL has various design units like entity, architecture and configuration that allow hierarchical modeling. The architecture can be described using behavioral, structural or dataflow styles depending on the level of abstraction. Behavioral models use processes to describe circuit operation. Structural models connect components. Dataflow models use signal assignments. VHDL also supports concepts like generics and generate statements for parameterization and repetition. Test benches are used to simulate and verify VHDL designs.Hdl

HdlAreeba Gill

╠²

HDL stands for hardware description language. It is a textual language used to formally describe and design electronic circuits and digital logic. HDL allows for automated analysis, simulation, and testing of electronic circuits before they are physically implemented. Common HDLs include VHDL and Verilog. HDL is used to write executable specifications for hardware and model circuits before physical creation, enabling simulation and synthesis into programmable logic devices like FPGAs.Vhdl design flow

Vhdl design flowRohit Chintu

╠²

This document provides an overview of the VHDL design flow process from modeling a digital system in VHDL to implementing it in an FPGA. It describes 5 main steps: 1) design entry using a hardware description language like VHDL, 2) functional simulation to verify logical behavior, 3) synthesis to convert the design to logic gates and components, 4) implementation which places and routes the design in the target FPGA, and 5) generating a configuration bitstream file to download to the FPGA. It then guides the reader through an example of designing an 8-bit up/down counter using this flow in Xilinx tools including writing VHDL code, simulating in ModelSim, and synthesizing andIntroduction to VHDL - Part 1

Introduction to VHDL - Part 1Abhilash Nair

╠²

VHDL is a hardware description language used to model digital systems. It allows modeling at different levels of abstraction from the system level down to the gate level. The basic VHDL design flow involves creating a block diagram, coding the design in VHDL, compiling and simulating for functional verification, synthesizing to a lower level representation, fitting the design to a technology, and verifying timing.Introduction to VHDL

Introduction to VHDLMohamed Samy

╠²

Overview on VHDL

Skills gained:

1- VHDL History and usage

2- VHDL design flow

3- Understand concurrency

This is part of VHDL 360 courseLogic Synthesis

Logic SynthesisVandanaPagar1

╠²

Logic synthesis is the process of converting a high-level design description into an optimized gate-level representation using a standard cell library and design constraints. The process involves translating the RTL description into an unoptimized internal representation, optimizing the logic, technology mapping, and producing an optimized gate-level netlist. An example logic synthesis flow is described for a 4-bit magnitude comparator design from RTL to optimized gates.Vhdl

Vhdlm.karthik Mkarthik.Jan

╠²

This document provides an introduction to VHDL including:

- An overview of the goals which are to further the author's knowledge of VHDL, provide history, and introduce syntax and concepts.

- A brief history of VHDL including its origins in the 1970s and standardization in the 1980s and beyond.

- Examples of VHDL code including a 4-to-1 multiplexer, 8-bit shifter, and testbenches with explanations of the code.Verilog

VerilogDEVANSHU JAISWAL

╠²

This document provides an overview of Verilog, including:

- Verilog is a hardware description language used to model and simulate digital circuits.

- It allows designing at different levels of abstraction from transistor to system level.

- The design process involves defining specifications, simulating designs, and redesigning until the design is correct.

- Verilog has constructs for modeling delays and parallel execution unlike programs that execute serially.

- Examples of Verilog code are provided to model a multiplexer and half adder circuit.Chapter 5 introduction to VHDL

Chapter 5 introduction to VHDLSSE_AndyLi

╠²

This document provides an overview of hardware description language (HDL) and VHDL. It begins with an introduction to HDLs and why they are needed to model digital hardware. It then presents an example VHDL code for an even parity detector circuit to demonstrate basic VHDL concepts like entities, architectures, signals, and concurrent statements. Finally, it discusses how VHDL fits into the digital design flow from coding to simulation to synthesis.HDL (hardware description language) presentation

HDL (hardware description language) presentationDigital Marketing Evangelist

╠²

This document discusses hardware description languages used in electronics design. It describes how HDLs like VHDL and Verilog are used to program digital and mixed-signal circuits. Simulation allows validation of the design against specifications. The document also discusses formal verification using property specification languages and different modeling styles for Verilog like gate-level, dataflow, and behavioral modeling.Vhdl 1

Vhdl 1žŁž│┘Ŗ┘å žŻ┘Ŗž»┘Ŗ┘å

╠²

The document discusses VHDL (VHSIC Hardware Description Language) and its use in circuit design. It provides three key points:

1. VHDL is used to describe the behavior of electronic circuits and systems and can then be used to implement those circuits in programmable devices like FPGAs or fabricate custom chips.

2. The VHDL design flow involves writing VHDL code with entities, architectures and processes to describe a circuit's behavior, then simulating and synthesizing the code to create a physical circuit implementation.

3. VHDL code structure includes library declarations to share code, entities defining a design's ports and interfaces, and architectures describing its functional behavior using processesVhdl 1 ppg

Vhdl 1 ppgAkshay Nagpurkar

╠²

The document provides an overview of VHDL (Very High Speed Integrated Circuit Hardware Description Language). It discusses the history and features of VHDL, including that it can be used to describe hardware structure and behavior. It also summarizes key VHDL concepts like libraries, packages, entities, architectures, configurations, signals, data types, operators, and language statements.Verilog Lecture1

Verilog Lecture1B├®o T├║

╠²

This document provides an overview of the ECE 551 Digital Design and Synthesis course for Fall 2009 at UW-Madison. It introduces the instructor, Eric Hoffman, and TA Vinod Nalamalapu. It outlines course goals, materials, tools, evaluation criteria and schedule. Key topics covered include Verilog, simulation, synthesis, FPGAs, standard cells and digital design flows. Students are expected to have prior knowledge of digital logic concepts from ECE 352.Verilog

VerilogMr SMAK

╠²

Verilog is a hardware description language that can be used to describe digital systems like microprocessors, switches, and memory. It allows designs to be created using either a bottom-up or top-down methodology. Bottom-up designs are built up from individual gates, while top-down designs start at a higher level and are easier to change. Verilog supports designing at different levels of abstraction like behavioral, register-transfer, and gate levels.Verilog HDL Training Course

Verilog HDL Training CoursePaul Laskowski

╠²

Verilog HDL (Hardware Description Language) Training Course for self-taught instructional. User should be familiar with basic digital and logic design. Helpful to have a Verilog simulator while going through examples.How to design Programs using VHDL

How to design Programs using VHDLEutectics

╠²

This Presentation covers most of VHDL designing basic from scratch.

click the below link for contents

http://eutectics.blogspot.com/2014/01/how-to-design-programs-using-vhdl-all.html

Lecture2 vhdl refresher

Lecture2 vhdl refresherNima Shafiee

╠²

This document provides an overview of VHDL and FPGA design using VHDL. It discusses the required and recommended reading materials, gives a brief history of VHDL, and covers some VHDL fundamentals including entity declaration, architecture, libraries, port modes, and the STD_LOGIC data type. Tips are provided on formatting, naming conventions, and increasing readability and portability of VHDL designs.Vhdl introduction

Vhdl introductionDhaval Shukla

╠²

VHDL is a hardware description language used to model digital circuits. It allows modeling at different levels of abstraction like behavioral, dataflow, and structural. VHDL supports design reuse through libraries and packages. Key benefits include being public standard, technology independent, and supporting design hierarchy, simulation, synthesis and documentation. The basic units in VHDL are entities which define the interface and architectures which describe the internal implementation. Architectures contain concurrent statements that execute in parallel and sequential statements in processes that execute sequentially.Vhdl

VhdlSHRUTI MURGAI

╠²

This document provides an introduction to VHDL and discusses its purpose and history. Some key points:

- VHDL stands for Very High Speed Integrated Circuit Hardware Description Language and is used to model and test digital circuits.

- VHDL allows for simulation and synthesis of digital designs, enabling the creation of actual working circuits from the VHDL model.

- VHDL is a concurrent language, meaning statements execute simultaneously rather than sequentially as in typical programming languages. This must be considered when writing VHDL code.

- The document outlines some golden rules for VHDL and stresses that it is a hardware design language, not a general purpose programming language. Proper VHDLIntroduction to VHDL

Introduction to VHDLYaser Kalifa

╠²

Yaser Khalifa introduces you to VHDL (VHSIC Hardware Description Language), a hardware description language used in electronic design automation to describe digital and mixed-signal systems such as field-programmable gate arrays and integrated circuits.Hardware Description Language

Hardware Description Language Prachi Pandey

╠²

Hardware Description Language (HDL) is used to describe digital systems in a textual format similar to a programming language. HDL represents both the structure and behavior of hardware at different levels of abstraction. It can be used for documentation, simulation to verify design functionality, and synthesis to automate hardware design processes. The two most common HDLs are VHDL and Verilog.VHDL_VIKAS.pptx

VHDL_VIKAS.pptxABHISHEKJHA176786

╠²

The document provides an overview of VHDL (Very High Speed Integrated Circuits Hardware Description Language). It discusses the key elements and features of VHDL including concurrent and sequential statements, signals and variables, generics, multi-valued logic systems, and operator overloading. It also describes different levels of abstraction in VHDL design including behavioral, register transfer, logic, and layout levels. Finally, it discusses some basic building blocks of VHDL like entities, architectures, configurations, and libraries.Dica ii chapter slides

Dica ii chapter slidesSIVA NAGENDRA REDDY

╠²

The document discusses the history and benefits of VHDL. It originated in the 1970s with the goal of creating a common language to shorten the time from hardware concept to implementation. The first version was released in 1985 by the Department of Defense. VHDL became an IEEE standard in 1987 and was updated in 1993 and 2001. It allows for technology-independent design, supports various design methodologies, simulation, synthesis and documentation. Key aspects include entities, architectures, configurations and using libraries.More Related Content

What's hot (20)

Hdl

HdlAreeba Gill

╠²

HDL stands for hardware description language. It is a textual language used to formally describe and design electronic circuits and digital logic. HDL allows for automated analysis, simulation, and testing of electronic circuits before they are physically implemented. Common HDLs include VHDL and Verilog. HDL is used to write executable specifications for hardware and model circuits before physical creation, enabling simulation and synthesis into programmable logic devices like FPGAs.Vhdl design flow

Vhdl design flowRohit Chintu

╠²

This document provides an overview of the VHDL design flow process from modeling a digital system in VHDL to implementing it in an FPGA. It describes 5 main steps: 1) design entry using a hardware description language like VHDL, 2) functional simulation to verify logical behavior, 3) synthesis to convert the design to logic gates and components, 4) implementation which places and routes the design in the target FPGA, and 5) generating a configuration bitstream file to download to the FPGA. It then guides the reader through an example of designing an 8-bit up/down counter using this flow in Xilinx tools including writing VHDL code, simulating in ModelSim, and synthesizing andIntroduction to VHDL - Part 1

Introduction to VHDL - Part 1Abhilash Nair

╠²

VHDL is a hardware description language used to model digital systems. It allows modeling at different levels of abstraction from the system level down to the gate level. The basic VHDL design flow involves creating a block diagram, coding the design in VHDL, compiling and simulating for functional verification, synthesizing to a lower level representation, fitting the design to a technology, and verifying timing.Introduction to VHDL

Introduction to VHDLMohamed Samy

╠²

Overview on VHDL

Skills gained:

1- VHDL History and usage

2- VHDL design flow

3- Understand concurrency

This is part of VHDL 360 courseLogic Synthesis

Logic SynthesisVandanaPagar1

╠²

Logic synthesis is the process of converting a high-level design description into an optimized gate-level representation using a standard cell library and design constraints. The process involves translating the RTL description into an unoptimized internal representation, optimizing the logic, technology mapping, and producing an optimized gate-level netlist. An example logic synthesis flow is described for a 4-bit magnitude comparator design from RTL to optimized gates.Vhdl

Vhdlm.karthik Mkarthik.Jan

╠²

This document provides an introduction to VHDL including:

- An overview of the goals which are to further the author's knowledge of VHDL, provide history, and introduce syntax and concepts.

- A brief history of VHDL including its origins in the 1970s and standardization in the 1980s and beyond.

- Examples of VHDL code including a 4-to-1 multiplexer, 8-bit shifter, and testbenches with explanations of the code.Verilog

VerilogDEVANSHU JAISWAL

╠²

This document provides an overview of Verilog, including:

- Verilog is a hardware description language used to model and simulate digital circuits.

- It allows designing at different levels of abstraction from transistor to system level.

- The design process involves defining specifications, simulating designs, and redesigning until the design is correct.

- Verilog has constructs for modeling delays and parallel execution unlike programs that execute serially.

- Examples of Verilog code are provided to model a multiplexer and half adder circuit.Chapter 5 introduction to VHDL

Chapter 5 introduction to VHDLSSE_AndyLi

╠²

This document provides an overview of hardware description language (HDL) and VHDL. It begins with an introduction to HDLs and why they are needed to model digital hardware. It then presents an example VHDL code for an even parity detector circuit to demonstrate basic VHDL concepts like entities, architectures, signals, and concurrent statements. Finally, it discusses how VHDL fits into the digital design flow from coding to simulation to synthesis.HDL (hardware description language) presentation

HDL (hardware description language) presentationDigital Marketing Evangelist

╠²

This document discusses hardware description languages used in electronics design. It describes how HDLs like VHDL and Verilog are used to program digital and mixed-signal circuits. Simulation allows validation of the design against specifications. The document also discusses formal verification using property specification languages and different modeling styles for Verilog like gate-level, dataflow, and behavioral modeling.Vhdl 1

Vhdl 1žŁž│┘Ŗ┘å žŻ┘Ŗž»┘Ŗ┘å

╠²

The document discusses VHDL (VHSIC Hardware Description Language) and its use in circuit design. It provides three key points:

1. VHDL is used to describe the behavior of electronic circuits and systems and can then be used to implement those circuits in programmable devices like FPGAs or fabricate custom chips.

2. The VHDL design flow involves writing VHDL code with entities, architectures and processes to describe a circuit's behavior, then simulating and synthesizing the code to create a physical circuit implementation.

3. VHDL code structure includes library declarations to share code, entities defining a design's ports and interfaces, and architectures describing its functional behavior using processesVhdl 1 ppg

Vhdl 1 ppgAkshay Nagpurkar

╠²

The document provides an overview of VHDL (Very High Speed Integrated Circuit Hardware Description Language). It discusses the history and features of VHDL, including that it can be used to describe hardware structure and behavior. It also summarizes key VHDL concepts like libraries, packages, entities, architectures, configurations, signals, data types, operators, and language statements.Verilog Lecture1

Verilog Lecture1B├®o T├║

╠²

This document provides an overview of the ECE 551 Digital Design and Synthesis course for Fall 2009 at UW-Madison. It introduces the instructor, Eric Hoffman, and TA Vinod Nalamalapu. It outlines course goals, materials, tools, evaluation criteria and schedule. Key topics covered include Verilog, simulation, synthesis, FPGAs, standard cells and digital design flows. Students are expected to have prior knowledge of digital logic concepts from ECE 352.Verilog

VerilogMr SMAK

╠²

Verilog is a hardware description language that can be used to describe digital systems like microprocessors, switches, and memory. It allows designs to be created using either a bottom-up or top-down methodology. Bottom-up designs are built up from individual gates, while top-down designs start at a higher level and are easier to change. Verilog supports designing at different levels of abstraction like behavioral, register-transfer, and gate levels.Verilog HDL Training Course

Verilog HDL Training CoursePaul Laskowski

╠²

Verilog HDL (Hardware Description Language) Training Course for self-taught instructional. User should be familiar with basic digital and logic design. Helpful to have a Verilog simulator while going through examples.How to design Programs using VHDL

How to design Programs using VHDLEutectics

╠²

This Presentation covers most of VHDL designing basic from scratch.

click the below link for contents

http://eutectics.blogspot.com/2014/01/how-to-design-programs-using-vhdl-all.html

Lecture2 vhdl refresher

Lecture2 vhdl refresherNima Shafiee

╠²

This document provides an overview of VHDL and FPGA design using VHDL. It discusses the required and recommended reading materials, gives a brief history of VHDL, and covers some VHDL fundamentals including entity declaration, architecture, libraries, port modes, and the STD_LOGIC data type. Tips are provided on formatting, naming conventions, and increasing readability and portability of VHDL designs.Vhdl introduction

Vhdl introductionDhaval Shukla

╠²

VHDL is a hardware description language used to model digital circuits. It allows modeling at different levels of abstraction like behavioral, dataflow, and structural. VHDL supports design reuse through libraries and packages. Key benefits include being public standard, technology independent, and supporting design hierarchy, simulation, synthesis and documentation. The basic units in VHDL are entities which define the interface and architectures which describe the internal implementation. Architectures contain concurrent statements that execute in parallel and sequential statements in processes that execute sequentially.Vhdl

VhdlSHRUTI MURGAI

╠²

This document provides an introduction to VHDL and discusses its purpose and history. Some key points:

- VHDL stands for Very High Speed Integrated Circuit Hardware Description Language and is used to model and test digital circuits.

- VHDL allows for simulation and synthesis of digital designs, enabling the creation of actual working circuits from the VHDL model.

- VHDL is a concurrent language, meaning statements execute simultaneously rather than sequentially as in typical programming languages. This must be considered when writing VHDL code.

- The document outlines some golden rules for VHDL and stresses that it is a hardware design language, not a general purpose programming language. Proper VHDLIntroduction to VHDL

Introduction to VHDLYaser Kalifa

╠²

Yaser Khalifa introduces you to VHDL (VHSIC Hardware Description Language), a hardware description language used in electronic design automation to describe digital and mixed-signal systems such as field-programmable gate arrays and integrated circuits.Hardware Description Language

Hardware Description Language Prachi Pandey

╠²

Hardware Description Language (HDL) is used to describe digital systems in a textual format similar to a programming language. HDL represents both the structure and behavior of hardware at different levels of abstraction. It can be used for documentation, simulation to verify design functionality, and synthesis to automate hardware design processes. The two most common HDLs are VHDL and Verilog.Similar to Vhdl (20)

VHDL_VIKAS.pptx

VHDL_VIKAS.pptxABHISHEKJHA176786

╠²

The document provides an overview of VHDL (Very High Speed Integrated Circuits Hardware Description Language). It discusses the key elements and features of VHDL including concurrent and sequential statements, signals and variables, generics, multi-valued logic systems, and operator overloading. It also describes different levels of abstraction in VHDL design including behavioral, register transfer, logic, and layout levels. Finally, it discusses some basic building blocks of VHDL like entities, architectures, configurations, and libraries.Dica ii chapter slides

Dica ii chapter slidesSIVA NAGENDRA REDDY

╠²

The document discusses the history and benefits of VHDL. It originated in the 1970s with the goal of creating a common language to shorten the time from hardware concept to implementation. The first version was released in 1985 by the Department of Defense. VHDL became an IEEE standard in 1987 and was updated in 1993 and 2001. It allows for technology-independent design, supports various design methodologies, simulation, synthesis and documentation. Key aspects include entities, architectures, configurations and using libraries.VHDL for beginners in Printed Circuit Board designing

VHDL for beginners in Printed Circuit Board designingmerlynsheena

╠²

Very High scale integrated circuit hardware description language abbreviated as a.k.a VHDL, is a smart software tool for designing and simulation basic to layered PCB structures and comes as an elite and reliable design software in the field of electronic technologies.VHDL-PRESENTATION.ppt

VHDL-PRESENTATION.pptDr.YNM

╠²

This document provides an introduction to VHDL and behavioral modeling. It discusses how VHDL was developed to address the need for modeling increasingly complex digital circuits. VHDL allows designs to be specified at different levels of abstraction through behavioral, dataflow, and structural descriptions. The document reviews key VHDL concepts like libraries, entities, architectures, and sequential/concurrent statements. Examples are given to demonstrate how basic digital components can be modeled in VHDL including gates, multiplexers, and flip-flops.L6_║▌║▌▀Żs_vhdl coures temporary hair dye for dark hair

L6_║▌║▌▀Żs_vhdl coures temporary hair dye for dark hairloyad20119

╠²

1. The document introduces VHDL language concepts including entities, architectures, concurrent and sequential constructs, and structural design. It then discusses CAD tools used for VHDL design including editors, checkers, simulators, and optimizers. 2. Designs can be targeted to a variety of FPGAs. The output of the design kit can also be converted to other formats like VHDL, Verilog, EDIF and SystemC. 3. The document provides examples of VHDL code including entities, architectures, processes, and structural descriptions. It also discusses modeling methods in VHDL including structural, behavioral, data flow, and mixed approaches.Verilogspk1

Verilogspk1supriya kurlekar

╠²

Verilog and VHDL are hardware description languages used to design digital circuits. Verilog was developed starting in 1985 and became an IEEE standard in 1995. VHDL was developed for the US Department of Defense starting in 1981 and also became an IEEE standard. Both languages use syntax similar to C and allow designers to describe circuits at different levels, from behavioral to structural descriptions using logic gates and modules. They support data types like nets, registers, vectors, and integers to model hardware. Common constructs include modules, ports, continuous assignments, procedural blocks, and instantiating lower-level modules.Digital principle and computer design Presentation (1).pptx

Digital principle and computer design Presentation (1).pptxMalligaarjunanN

╠²

This document discusses the Hardware Description Language (HDL) VHDL. It provides an overview of VHDL, including that it is used to describe and simulate digital circuits, and is an IEEE standard. The key elements of VHDL are then described - entities define input/output ports, architectures describe how the circuit operates, and configurations define how designs are linked together. Examples of each element are provided. Finally, it briefly discusses VHDL modeling styles and objects like constants, variables, and signals.vlsi introduction to hdl and its typesunit-1.pptx

vlsi introduction to hdl and its typesunit-1.pptxiconicyt2

╠²

This document provides an introduction to VHDL and Verilog HDL. It discusses the need for HDLs to describe digital systems, as well as the basic structure and components of VHDL and Verilog modules. The key capabilities of VHDL and Verilog are described, including their support for hierarchy, flexible design methodologies, and modeling of different description styles. Basic concepts like entities, architectures, modules, ports, and data types are introduced.Vhdl new

Vhdl newSharad Institute of Technology,college of Engineering,Yadrav

╠²

The document introduces VHDL to engineers who will use it to describe circuits for implementation in programmable logic or ASICs. It aims to provide enough information for engineers to quickly get started using VHDL while avoiding prolonged discussions more relevant for simulation developers. The document suggests coding styles appropriate for a variety of synthesis and simulation tools.Embedded system

Embedded systemashraf eltholth

╠²

An embedded system is a microprocessor-based system designed to perform specific tasks and embedded as a component in a larger system. Common application areas include automotive electronics, aircraft electronics, trains, and telecommunications. The key design challenge is to optimize numerous design metrics like unit cost, size, performance, power consumption, and flexibility simultaneously. Common integrated circuit technologies used include full-custom/VLSI, semi-custom ASICs, and programmable logic devices like FPGAs. VHDL and Verilog are hardware description languages used to model and simulate the system at different levels of abstraction from transistors to functional behavior.02 direct3 d_pipeline

02 direct3 d_pipelineGirish Ghate

╠²

The document provides an introduction to DirectX and its components for 3D graphics programming. DirectX includes Direct3D for 3D rendering, DXGI for managing graphics resources, and HLSL for writing shaders. Direct3D uses a graphics pipeline with stages like vertex shading, rasterization, and pixel shading. Programmers interface with Direct3D through COM objects and interfaces.Design And Simulation of Electronic Circuits Lec_02

Design And Simulation of Electronic Circuits Lec_02Mohamed Atef

╠²

This document provides an introduction to VHDL, including:

- VHDL is used to describe hardware and allows for concurrent execution of instructions.

- VHDL models allow for more intelligent modeling of digital circuits than other methods.

- Key features of VHDL include case insensitivity, white space insensitivity, and use of "--" for comments.

- VHDL uses entities to abstract circuit functionality and architectures to describe circuit operation using various modeling approaches.

- Signals, variables, and constants represent wires, local storage, and immutable values in VHDL models.hardware description language power point presentation

hardware description language power point presentationdhananjeyanrece

╠²

A hardware description language enables a precise, formal description of an electronic circuit that allows for the automated analysis and simulation of an electronic circuit. It also allows for the synthesis of an HDL description into a netlist (a specification of physical electronic components and how they are connected together), which can then be placed and routed to produce the set of masks used to create an integrated circuit.Verilog

VerilogMohamed Rayan

╠²

Those slides describe digital design using Verilog HDL,

starting with Design methodologies for any digital circuit then difference between s/w (C/C++) and H/w (Verilog) and the most important constructs that let us start hardware design using Verilog HDL.vhdlTutorial VHDL notes, introductions and Basic concepts

vhdlTutorial VHDL notes, introductions and Basic conceptsAnilNaik42

╠²

VHDL notes, introductions and Basic conceptsVerilog tutorial

Verilog tutorialraju reddy

╠²

This document discusses Verilog HDL as a solution for designing digital circuits. It provides an overview of traditional design approaches like gate-level and schematic design and their limitations for large, complex designs. Verilog HDL was developed in the 1980s to provide a simple, intuitive way to describe digital circuits for modeling, simulation, and analysis. It allows a top-down design approach with modules that have well-defined interfaces and behaviors. The document covers various coding styles in Verilog like structural, dataflow, and behavioral, as well as concepts like ports, parameters, nets, registers, delays, and test benches. It provides examples of memory operations and emphasizes thinking concurrently when writing Verilog code.Recently uploaded (20)

Sachpazis: Foundation Analysis and Design: Single Piles

Sachpazis: Foundation Analysis and Design: Single PilesDr.Costas Sachpazis

╠²

Žü. ╬ÜŽÄŽāŽä╬▒Žé ╬Ż╬▒ŽćŽĆ╬¼╬Č╬ĘŽé: Foundation Analysis and Design: Single Piles

Welcome to this comprehensive presentation on "Foundation Analysis and Design," focusing on Single PilesŌĆöStatic Capacity, Lateral Loads, and Pile/Pole Buckling. This presentation will explore the fundamental concepts, equations, and practical considerations for designing and analyzing pile foundations.

We'll examine different pile types, their characteristics, load transfer mechanisms, and the complex interactions between piles and surrounding soil. Throughout this presentation, we'll highlight key equations and methodologies for calculating pile capacities under various conditions.Unit II: Design of Static Equipment Foundations

Unit II: Design of Static Equipment FoundationsSanjivani College of Engineering, Kopargaon

╠²

Design of Static Equipment, that is vertical vessels foundation.Air pollution is contamination of the indoor or outdoor environment by any ch...

Air pollution is contamination of the indoor or outdoor environment by any ch...dhanashree78

╠²

Air pollution is contamination of the indoor or outdoor environment by any chemical, physical or biological agent that modifies the natural characteristics of the atmosphere.

Household combustion devices, motor vehicles, industrial facilities and forest fires are common sources of air pollution. Pollutants of major public health concern include particulate matter, carbon monoxide, ozone, nitrogen dioxide and sulfur dioxide. Outdoor and indoor air pollution cause respiratory and other diseases and are important sources of morbidity and mortality.

WHO data show that almost all of the global population (99%) breathe air that exceeds WHO guideline limits and contains high levels of pollutants, with low- and middle-income countries suffering from the highest exposures.

Air quality is closely linked to the earthŌĆÖs climate and ecosystems globally. Many of the drivers of air pollution (i.e. combustion of fossil fuels) are also sources of greenhouse gas emissions. Policies to reduce air pollution, therefore, offer a win-win strategy for both climate and health, lowering the burden of disease attributable to air pollution, as well as contributing to the near- and long-term mitigation of climate change.

Frankfurt University of Applied Science urkunde

Frankfurt University of Applied Science urkundeLisa Emerson

╠²

Duplicate Frankfurt University of Applied Science urkunde, make a Frankfurt UAS degree.Industrial Valves, Instruments Products Profile

Industrial Valves, Instruments Products Profilezebcoeng

╠²

WeŌĆÖre excited to share our product profile, showcasing our expertise in Industrial Valves, Instrumentation, and Hydraulic & Pneumatic Solutions.

We also supply API-approved valves from globally trusted brands, ensuring top-notch quality and internationally certified solutions. LetŌĆÖs explore valuable business opportunities together!

We specialize in:

ŌĆó Industrial Valves (Gate, Globe, Ball, Butterfly, Check)

ŌĆó Instrumentation (Pressure Gauges, Transmitters, Flow Meters)

ŌĆó Pneumatic Products (Cylinders, Solenoid Valves, Fittings)

As authorized partners of trusted global brands, we deliver high-quality solutions tailored to meet your industrial needs with seamless support.Turbocor Product and Technology Review.pdf

Turbocor Product and Technology Review.pdfTotok Sulistiyanto

╠²

High Efficiency Chiller System in HVACIntegration of Additive Manufacturing (AM) with IoT : A Smart Manufacturing A...

Integration of Additive Manufacturing (AM) with IoT : A Smart Manufacturing A...ASHISHDESAI85

╠²

Combining 3D printing with Internet of Things (IoT) enables the creation of smart, connected, and customizable objects that can monitor, control, and optimize their performance, potentially revolutionizing various industries. oT-enabled 3D printers can use sensors to monitor the quality of prints during the printing process. If any defects or deviations from the desired specifications are detected, the printer can adjust its parameters in real time to ensure that the final product meets the required standards.How Engineering Model Making Brings Designs to Life.pdf

How Engineering Model Making Brings Designs to Life.pdfMaadhu Creatives-Model Making Company

╠²

This PDF highlights how engineering model making helps turn designs into functional prototypes, aiding in visualization, testing, and refinement. It covers different types of models used in industries like architecture, automotive, and aerospace, emphasizing cost and time efficiency.How to Build a Maze Solving Robot Using Arduino

How to Build a Maze Solving Robot Using ArduinoCircuitDigest

╠²

Learn how to make an Arduino-powered robot that can navigate mazes on its own using IR sensors and "Hand on the wall" algorithm.

This step-by-step guide will show you how to build your own maze-solving robot using Arduino UNO, three IR sensors, and basic components that you can easily find in your local electronics shop.Syntax Directed Definitions Synthesized Attributes and Inherited Attributes

Syntax Directed Definitions Synthesized Attributes and Inherited AttributesGunjalSanjay

╠²

Syntax Directed Definitions

google_developer_group_ramdeobaba_university_EXPLORE_PPT

google_developer_group_ramdeobaba_university_EXPLORE_PPTJayeshShete1

╠²

EXPLORE 6 EXCITING DOMAINS:

1. Machine Learning: Discover the world of AI and ML!

2. App Development: Build innovative mobile apps!

3. Competitive Programming: Enhance your coding skills!

4. Web Development: Create stunning web applications!

5. Blockchain: Uncover the power of decentralized tech!

6. Cloud Computing: Explore the world of cloud infrastructure!

Join us to unravel the unexplored, network with like-minded individuals, and dive into the world of tech!How to Make an RFID Door Lock System using Arduino

How to Make an RFID Door Lock System using ArduinoCircuitDigest

╠²

Learn how to build an RFID-based door lock system using Arduino to enhance security with contactless access control.Mathematics behind machine learning INT255 INT255__Unit 3__PPT-1.pptx

Mathematics behind machine learning INT255 INT255__Unit 3__PPT-1.pptxppkmurthy2006

╠²

Mathematics behind machine learning INT255 Multi objective genetic approach with Ranking

Multi objective genetic approach with Rankingnamisha18

╠²

Multi objective genetic approach with Ranking Wireless-Charger presentation for seminar .pdf

Wireless-Charger presentation for seminar .pdfAbhinandanMishra30

╠²

Wireless technology used in chargerVhdl

- 1. VHDL Presented by :- Aaqib Ashraf Parrey Basit

- 2. VHDL ŌĆó VHDL is Hardware Language ŌĆó Describes the behavior of an electronic circuit or system ŌĆó Full form VHDL is VHSIC HDL or Very High Speed Integrated Circuit Hardware Description Language ŌĆó VHDL is only for Digital IC and not for Analog IC ŌĆó VHDL uses gate level design abstraction

- 3. History of VHDL ŌĆó VHDL was developed by Department of Defense ŌĆō US 1980 ŌĆó 1980-87= Department of Defense ŌĆó 1987 DOD permitted for commercial purpose and got IEEE Std (1076) ŌĆó 1993 Revised Edition (not synthesizable in this period) ŌĆó 1996 Revised Further( It is synthesized language and simulation tools were added)

- 4. VHDL vs. ŌĆśCŌĆÖ language ŌĆó VHDL is Concurrent Language while as ŌĆśCŌĆÖ is sequential language. ŌĆó VHDL is synthesizable while as ŌĆśCŌĆÖ is not.

- 5. VHDL Capabilities ŌĆó It is case insensitive Language ŌĆó It is vendor independent (Xilinx, Altera, Modelsim.etc) ŌĆó It supports synthesis (VHDL to Netlist) ŌĆó It supports simulation i.e. in the absence of real system we simulate the function by taking a model of the function ŌĆó It supports 9 value logic system

- 6. Program structure in VHDL ŌĆó Library --- list of libraries ŌĆó Entity ---I/O pins of the circuit ŌĆó Architecture --- VHDL code

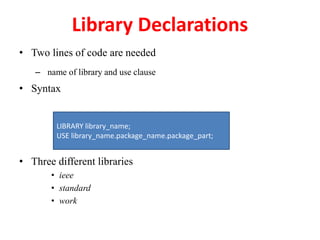

- 7. Library Declarations ŌĆó Two lines of code are needed ŌĆō name of library and use clause ŌĆó Syntax ŌĆó Three different libraries ŌĆó ieee ŌĆó standard ŌĆó work LIBRARY library_name; USE library_name.package_name.package_part;

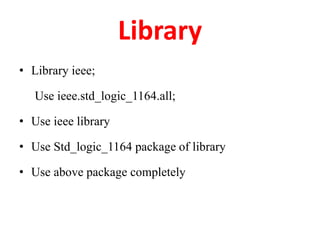

- 8. Library ŌĆó Library ieee; Use ieee.std_logic_1164.all; ŌĆó Use ieee library ŌĆó Use Std_logic_1164 package of library ŌĆó Use above package completely

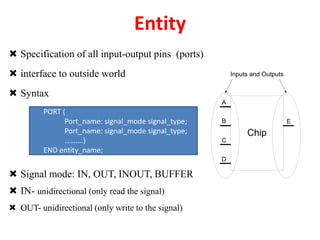

- 9. Entity ’āÆ Specification of all input-output pins (ports) ’āÆ interface to outside world ’āÆ Syntax ’āÆ Signal mode: IN, OUT, INOUT, BUFFER ’āÆ IN- unidirectional (only read the signal) ’āÆ OUT- unidirectional (only write to the signal) ENTITY entity_name IS PORT ( Port_name: signal_mode signal_type; Port_name: signal_mode signal_type; ŌĆ”ŌĆ”ŌĆ”.) END entity_name; Inputs and Outputs Chip A B C D E

- 10. Entity ŌĆó Entity is the building block of VHDL program. It is used to declare input and output ports. ŌĆó Example :- entity ABCD is port ( a : in std_logic; b : in std_logic; c : out std_logic); end ABCD;

- 11. Architecture ’āÆ Description of how the circuit should behave ’āÆ Syntax ’āÆ Two parts: ’āÉDeclarative part (optional): signals and constants are declared here ’āÉCode part ARCHITECTURE architecture_name OF entity_name IS [declaration] BEGIN (code) END architecture_name; ChipA B C D EX Y

- 12. Architecture ŌĆó It is the last and the third part of VHDL program. In this part we are writing logic of program. ŌĆó Example architecture myDEF of ABCD is begin output <= input1 and input2; end myDEF;

- 13. Types of modeling style in VHDL ŌĆó Data flow modeling (Design Equations) ŌĆó Behavioral modeling (Explains Behavior) ŌĆó Structural modeling (Connection of sub modules) ŌĆó Hybrid modeling

- 14. Signal ŌĆó All internal variables Signal X,Y : std_logic; Chip Signal A B C D EX Y

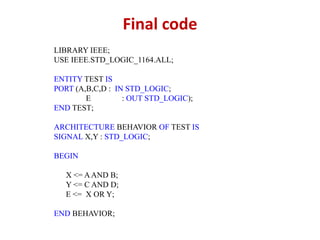

- 15. Final code LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; ENTITY TEST IS PORT (A,B,C,D : IN STD_LOGIC; E : OUT STD_LOGIC); END TEST; ARCHITECTURE BEHAVIOR OF TEST IS SIGNAL X,Y : STD_LOGIC; BEGIN X <= AAND B; Y <= C AND D; E <= X OR Y; END BEHAVIOR;

- 16. Multiplexer

- 19. D- flip flop d q DFF Clk rst R C D Q 1 1/0 1/0 0 0 0 1 0 0 1 1 1

- 21. SIMULATION RESULT OF D-FLIP FLOP

- 22. THANK YOU