vlsi

Download as PPT, PDF1 like1,093 views

This document provides an introduction to VLSI design. It discusses the evolution of integrated circuits from SSI to VLSI, CMOS transistor structure and logic gates, the VLSI design process involving different levels of abstraction, design styles including full custom, ASIC, programmable logic, and system-on-chip. It also covers trends in transistor size, interconnect delay becoming dominant, and issues like power consumption and noise. The objectives are to understand transistor operation, CMOS logic, power and delay estimation, and layout design rules.

1 of 30

Downloaded 49 times

Recommended

ZERO WIRE LOAD MODEL.pptx

ZERO WIRE LOAD MODEL.pptxVishalYadav29718

Ã˝

Here are the key points about setup time, hold time, and insertion delay in VLSI physical design:

- Setup time is the minimum time before the clock edge that the data needs to be stable in order for it to be correctly captured by the flip-flop.

- Hold time is the minimum time after the clock edge that the data needs to remain stable. It provides a "window" after the clock edge for the data to remain valid.

- Insertion delay is the time it takes for the clock signal to propagate from the clock source to a flip-flop input pin through the clock tree.

- During clock tree synthesis, the tool aims to balance the insertion delays across the clock tree to minimizeBasics of vlsi

Basics of vlsiScientech Technologies Pvt. Ltd.

Ã˝

VLSI stands for Very Large Scale integration is the art of integrating millions of transistors on a Silicon Chip. Researchers are working to incorporate large scale integration of electronic devices on a single silica chip “Integrated Circuit or IC” to fulfill the market demand. Here, in this presentation we will learn introduction and history of VLSI, VLSI Design Style and Flow, VLSI Design Approaches, CPLD, FPGA, Programmable Logic Arrays, Xilinx vs. Altera Design tools, flow and files.The composition and packaging of integrated circuits

The composition and packaging of integrated circuitsVinsion Chan

Ã˝

Integrated circuits (ICs) are electronic circuits formed on a small chip of semiconductor material. They consist of transistors, resistors, capacitors, and other components connected together to form complete circuits. ICs can be categorized in several ways, including by function (analog, digital, or mixed-signal), manufacturing process (semiconductor or thin-film), integration level (small-scale to very large-scale), conductive type (bipolar or unipolar), application (computers, communications, etc.), and physical appearance (circular, flat, or dual-in-line package). Modern ICs allow many circuit elements to be miniaturized and placed on a single semiconductor chip, improving performance, reliability, and energy efficiency.Totem Technologies for Analog, Memory, Mixed-Signal Designs

Totem Technologies for Analog, Memory, Mixed-Signal DesignsAnsys

Ã˝

Analog, mixed-signal and custom designs face unique challenges when it comes to power and reliability analysis. SRAM and FLASH memories are pushing the envelope to handle large designs, while mixed-signal and RF designs need concurrent analysis of large analog blocks with interspersed digital logic as well as substrate noise coupling. This presentation demonstrates how Totem, a single platform for Power Noise and Reliability, can be used to address the unique challenges for analog, mixed-signal and custom designs. Learn more on our website: https://bit.ly/1qk5JujLect01 flow

Lect01 flowprabhu_vlsi

Ã˝

The document outlines the generalized ASIC design flow, including high level design, RTL design, system and timing verification, physical design involving floorplanning, placement and routing, and performance and manufacturability verification through extraction, timing analysis, and design rule checking. Key steps involve specification capture, logic design and verification through simulation, RTL synthesis, gate-level mapping to a target library, placement and routing, and post-layout verification.VLSI Design-Lecture2 introduction to ic technology

VLSI Design-Lecture2 introduction to ic technologysritulasiadigopula

Ã˝

VLSI is the process of integrating millions of transistors on a single chip. It was invented in 1980 and allows for 20,000 to 1,000,000 transistors per chip. VLSI enables devices to be physically smaller, cheaper to produce, faster, more reliable and efficient. Integrated circuits are used in consumer electronics, computers, wireless devices, automotive electronics, aerospace, defense and more. Moore's Law predicts that the number of transistors on a chip will double every 18 months, allowing continued advancement and miniaturization of chips. Common processing technologies for VLSI include CMOS, Bipolar, BiCMOS, GaAs and SOI.Discrete time filter design by windowing 3

Discrete time filter design by windowing 3HIMANSHU DIWAKAR

Ã˝

The document discusses filter design by windowing, which is the simplest method for designing finite impulse response (FIR) filters in discrete time. It involves starting with an ideal frequency response and approximating it using a window function to make the impulse response finite. Various window functions are presented such as rectangular, Bartlett, Hanning, Hamming, and Blackman, along with their properties. The Kaiser window is also discussed as it allows trading off main lobe width and side lobe levels. An example is provided to design a lowpass filter using the Kaiser window method. Finally, the document notes that window design methods can also be applied to multiband filters.Design challenges in physical design

Design challenges in physical designDeiptii Das

Ã˝

The document discusses several key challenges in physical design for semiconductor chips. It outlines general challenges faced in analog, digital, and mixed-signal design such as manufacturing technology limitations, leakage power, interconnect delay, and congestion. Specific issues discussed in more detail include routing congestion, IR drop causing voltage variations, crosstalk interference, scaling challenges between different process nodes, and thermal issues in 3D chip design involving through-silicon vias. The document provides an overview of design objectives to optimize power, timing, area, and yield against these physical implementation challenges.Design of ring oscillator using controlled low voltage swing inverter

Design of ring oscillator using controlled low voltage swing inverter khush_19

Ã˝

Hello everyone. I am khushboo kumari.

I am pursuing M.tech from NIT Agartala(2017-2019). This is my 3rd semester partial project where i have successfully implemented the design of low voltage swing inverter. In the 4th semester i would be designing ring oscillator by connecting odd number of this inverter design in cascade.

I was able to complete this under the supervision of my respected guide Bidyut kumar .

Hope this presentation helps you to some extent.

Thank you.

Please do comment me if you have any doubts/ query/ or suggestions.Vlsi physical design

Vlsi physical designI World Tech

Ã˝

The document discusses the physical design process for VLSI circuits. It describes the main steps as partitioning, floor planning and placement, routing, layout optimization, and extraction and verification. The goals of physical design are to minimize signal delays, interconnection area, and power usage. Physical design transforms the logical structure of a circuit into its physical layout.Fpga in space

Fpga in spaceJBPooMahaVinuShree

Ã˝

"Field Programmable Gate Array (FPGA)" devices have been used in space for more than a decade with a mixed level of success. Until now, few reprogrammable devices have been used on European spacecraft due to their sensitivity to involuntary reconfiguration due to Single Event Upsets (SEU) induced by radiation.Digital VLSI Design : Introduction

Digital VLSI Design : IntroductionUsha Mehta

Ã˝

This document discusses digital VLSI design flows. It begins by acknowledging previous work that informed the presentation. It then discusses considerations in developing an electronic system, including components of the system. It describes integrated circuits based on application, fabrication technology, device, and device count. It discusses using standard or application-specific integrated circuits. It outlines a top-down design approach and terminology used in the design flow.Placement and routing in full custom physical design

Placement and routing in full custom physical designDeiptii Das

Ã˝

The document discusses placement and routing in full custom VLSI design. Placement involves techniques like diffusion sharing, gate matrix layout, and common centroid to optimize area and performance. Routing creates physical interconnects and involves global routing, track assignment, detail routing, and search and repair to meet timing constraints while resolving design rule checking violations. The quality of placement impacts routability, and routing aims to minimize delay along critical paths through techniques like buffer insertion and wire sizing.Vlsi technology-dinesh

Vlsi technology-dineshdinesh kumar

Ã˝

The document discusses the history and development of VLSI (Very Large Scale Integration) technology. It explains that Jack Kilby invented the integrated circuit in 1958, combining multiple transistors on a single silicon chip. This helped address issues with circuit size and speed. Developments since then have led to billions of transistors on modern microprocessors, enabled by advances in semiconductor fabrication processes down to 65nm. The document outlines the fabrication process for ICs and their uses in electronic devices and space communications.Multi mode multi corner (mmmc)

Multi mode multi corner (mmmc)shaik sharief

Ã˝

This document discusses multi mode multi corner (MMMC) analysis for chip design. It defines that a mode is a set of design parameters like clocks and timing constraints, and a corner captures process, voltage, and temperature variations. It provides examples of multiple modes like normal, sleep, and test modes and corners for temperature, voltage, process variations, and parasitic interconnects. The document gives an example of analyzing a chip with 4 modes under 3 process-voltage-temperature corners and 3 parasitic interconnect corners, showing 9 analysis cases.Basic synthesis flow and commands in digital VLSI

Basic synthesis flow and commands in digital VLSISurya Raj

Ã˝

This document discusses logic synthesis, including the basic synthesis flow and commands, synthesis script flow, technology libraries, design objects like cells and ports, timing paths, and constraints like defining clocks and input/output delays. It provides examples of setting library variables, reading and writing designs, and applying constraints to clocks and I/O. The document contains information on synthesis tools and processes at a high level.Vlsi physical design automation on partitioning

Vlsi physical design automation on partitioningSushil Kundu

Ã˝

This document provides an introduction to VLSI physical design automation and partitioning. It discusses the importance of partitioning large circuits into smaller subcircuits for manageable design. The objectives of partitioning are to minimize the number of partitions and interconnections between partitions. Common partitioning algorithms discussed include min-cut bipartitioning, Kernighan-Lin iterative improvement algorithm, and other methods like ratio cut, genetic algorithms, and simulated annealing. Partitioning is an essential step in the physical design flow and impacts circuit performance and layout costs.Verilog Test Bench

Verilog Test BenchDr.YNM

Ã˝

This PPT is meant to explain the construction and implementation of Verilog Test Bench with examples.Introduction to VLSI

Introduction to VLSI illpa

Ã˝

This document provides an overview of VLSI design for a course. It discusses topics including CMOS transistors and logic gates, VLSI levels of abstraction, the VLSI design process, design styles like full custom and ASIC, and trends like Moore's Law. The roadmap outlines topics to be covered like CMOS processing, combinational and sequential circuit design, and a design project to complete a chip. Course objectives are listed relating to VLSI analysis, layout design, and system design skills.Soc architecture and design

Soc architecture and designSatya Harish

Ã˝

The document discusses system-on-chip (SOC) architectures and designs. It covers topics like different processor types (e.g. superscalar, VLIW), on-chip storage like caches and memory, interconnects like buses and networks-on-chip, and how SOCs are customized for applications like graphics, media, and security. Examples of SOCs include the iPhone SOC with an ARM processor and AMD's Barcelona multicore processor. The document also discusses design tradeoffs involving time, area, power, and costs as SOCs increase in complexity.Clk-to-q delay, library setup and hold time

Clk-to-q delay, library setup and hold timeVLSI SYSTEM Design

Ã˝

I have been receiving multiple queries on what is clk-to-q delay, how's it different from library setup time and library hold time, etc. I mentioned in my discussions, that the videos on CMOS digital circuit will be uploaded soon, but looks like, it might take some time, and hence decided to uploaded few images from my CMOS course, to explain the difference between all of them.Morello Technology Demonstrator Hardware Overview - Mark Inskip, Arm

Morello Technology Demonstrator Hardware Overview - Mark Inskip, ArmKTN

Ã˝

Presentation from the briefing event for ISCF Digital Security by Design competition: Technology Enabled Business-Led Demonstator Stage 1 Expression of InterestHigh efficiency power amplifiers

High efficiency power amplifiersAbhishek Kadam

Ã˝

This document discusses high efficiency power amplifier technologies. It describes:

1) The requirements for future power amplifiers including high linearity, output power, bandwidth, and reduced energy consumption.

2) How switch-mode power amplifier technology using pulse width modulation can achieve up to 90% efficiency but is limited to low frequencies.

3) Different classes of switch-mode power amplifier operation (Class D, E, and F) and how they work to achieve high efficiency by minimizing voltage-current overlap losses.

4) Performance comparisons of different technologies like GaN and LDMOS transistors, noting advantages like bandwidth and efficiency of GaN for radio applications.VLSI technology

VLSI technologyAidell2583

Ã˝

It was a company which designed and manufactured custom and semi-custom Ics."Are you looking best Real time final year engineering projects for ece in bangalore.embedded innovation lab is the right place."Catalog Feeo Solar

Catalog Feeo SolarHUY HOANG TECHNOLOGY JOINT STOCK COMPANY

Ã˝

This document provides information on YUEQING FEEO ELECTRIC CO.,LTD, a professional solar PV electric components manufacturer located in Yueqing City, China. It introduces their FEO-63 Solar DC Mini Circuit Breaker (DC MCB), including its specifications, applications, characteristic curve, dimensions, and connection details. The FEO-63 is designed to provide overcurrent protection within appliances or electrical equipment for direct current applications, with a rated operating voltage range of DC12V - DC1000V and rated current from 1A to 63A.SISTec Microelectronics VLSI design

SISTec Microelectronics VLSI designDr. Ravi Mishra

Ã˝

The document discusses trends in integration technologies such as VLSI. It describes how VLSI has allowed for more compact, lower power, and higher speed integrated circuits. It classifies integrated circuits based on application, fabrication technique, technology, and device count. It then discusses the history of integrated circuits from the transistor in 1947 to modern chips containing tens of millions of transistors. It outlines drivers for VLSI technology including smaller sizes, lower power, and reduced costs.Implementing Useful Clock Skew Using Skew Groups

Implementing Useful Clock Skew Using Skew GroupsM Mei

Ã˝

Implementing useful skew through skew groups or manual buffer insertion can improve timing in a large memory block design. Skew groups define a target skew value for groups of clock pins before clock tree synthesis, resulting in a smaller clock tree, lower power increase, and less routing complexity compared to manual buffer insertion. Manual insertion precisely controls skew by adding buffers but dramatically increases clock cell count and power consumption versus skew groups. Both methods effectively improved setup timing for the memory block design.VLSI UNIT-1.1.pdf.ppt

VLSI UNIT-1.1.pdf.pptrajukolluri

Ã˝

VLSI design involves integrating millions of transistors onto a single chip. There are various design styles including full custom, standard cell, gate array, and FPGA. Full custom designs have fully customized cells and layouts but require more design time. Standard cell and gate array styles use predesigned cells, reducing design time but only customizing interconnect layers. FPGA designs have no custom masks and the fastest design turnaround time.Ic tech unit 5- VLSI Process Integration

Ic tech unit 5- VLSI Process Integrationkriticka sharma

Ã˝

junction oxide and isolation techniques, LOCOS, Metallization, NMOS and CMOS technology, FAult diagnosisCMOS Topic 6 -_designing_combinational_logic_circuits

CMOS Topic 6 -_designing_combinational_logic_circuitsIkhwan_Fakrudin

Ã˝

This document discusses designing combinational logic circuits using static complementary CMOS design. It explains how to construct static CMOS circuits for logic gates like NAND and NOR by using pull-up and pull-down networks of PMOS and NMOS transistors respectively. Issues related to pass-transistor design like noise margins and static power consumption are also covered. The document provides details on implementing various logic functions using pass-transistor logic and differential pass-transistor logic. It discusses solutions to overcome the disadvantages of pass-transistor logic like level restoration and use of multiple threshold transistors.More Related Content

What's hot (20)

Design of ring oscillator using controlled low voltage swing inverter

Design of ring oscillator using controlled low voltage swing inverter khush_19

Ã˝

Hello everyone. I am khushboo kumari.

I am pursuing M.tech from NIT Agartala(2017-2019). This is my 3rd semester partial project where i have successfully implemented the design of low voltage swing inverter. In the 4th semester i would be designing ring oscillator by connecting odd number of this inverter design in cascade.

I was able to complete this under the supervision of my respected guide Bidyut kumar .

Hope this presentation helps you to some extent.

Thank you.

Please do comment me if you have any doubts/ query/ or suggestions.Vlsi physical design

Vlsi physical designI World Tech

Ã˝

The document discusses the physical design process for VLSI circuits. It describes the main steps as partitioning, floor planning and placement, routing, layout optimization, and extraction and verification. The goals of physical design are to minimize signal delays, interconnection area, and power usage. Physical design transforms the logical structure of a circuit into its physical layout.Fpga in space

Fpga in spaceJBPooMahaVinuShree

Ã˝

"Field Programmable Gate Array (FPGA)" devices have been used in space for more than a decade with a mixed level of success. Until now, few reprogrammable devices have been used on European spacecraft due to their sensitivity to involuntary reconfiguration due to Single Event Upsets (SEU) induced by radiation.Digital VLSI Design : Introduction

Digital VLSI Design : IntroductionUsha Mehta

Ã˝

This document discusses digital VLSI design flows. It begins by acknowledging previous work that informed the presentation. It then discusses considerations in developing an electronic system, including components of the system. It describes integrated circuits based on application, fabrication technology, device, and device count. It discusses using standard or application-specific integrated circuits. It outlines a top-down design approach and terminology used in the design flow.Placement and routing in full custom physical design

Placement and routing in full custom physical designDeiptii Das

Ã˝

The document discusses placement and routing in full custom VLSI design. Placement involves techniques like diffusion sharing, gate matrix layout, and common centroid to optimize area and performance. Routing creates physical interconnects and involves global routing, track assignment, detail routing, and search and repair to meet timing constraints while resolving design rule checking violations. The quality of placement impacts routability, and routing aims to minimize delay along critical paths through techniques like buffer insertion and wire sizing.Vlsi technology-dinesh

Vlsi technology-dineshdinesh kumar

Ã˝

The document discusses the history and development of VLSI (Very Large Scale Integration) technology. It explains that Jack Kilby invented the integrated circuit in 1958, combining multiple transistors on a single silicon chip. This helped address issues with circuit size and speed. Developments since then have led to billions of transistors on modern microprocessors, enabled by advances in semiconductor fabrication processes down to 65nm. The document outlines the fabrication process for ICs and their uses in electronic devices and space communications.Multi mode multi corner (mmmc)

Multi mode multi corner (mmmc)shaik sharief

Ã˝

This document discusses multi mode multi corner (MMMC) analysis for chip design. It defines that a mode is a set of design parameters like clocks and timing constraints, and a corner captures process, voltage, and temperature variations. It provides examples of multiple modes like normal, sleep, and test modes and corners for temperature, voltage, process variations, and parasitic interconnects. The document gives an example of analyzing a chip with 4 modes under 3 process-voltage-temperature corners and 3 parasitic interconnect corners, showing 9 analysis cases.Basic synthesis flow and commands in digital VLSI

Basic synthesis flow and commands in digital VLSISurya Raj

Ã˝

This document discusses logic synthesis, including the basic synthesis flow and commands, synthesis script flow, technology libraries, design objects like cells and ports, timing paths, and constraints like defining clocks and input/output delays. It provides examples of setting library variables, reading and writing designs, and applying constraints to clocks and I/O. The document contains information on synthesis tools and processes at a high level.Vlsi physical design automation on partitioning

Vlsi physical design automation on partitioningSushil Kundu

Ã˝

This document provides an introduction to VLSI physical design automation and partitioning. It discusses the importance of partitioning large circuits into smaller subcircuits for manageable design. The objectives of partitioning are to minimize the number of partitions and interconnections between partitions. Common partitioning algorithms discussed include min-cut bipartitioning, Kernighan-Lin iterative improvement algorithm, and other methods like ratio cut, genetic algorithms, and simulated annealing. Partitioning is an essential step in the physical design flow and impacts circuit performance and layout costs.Verilog Test Bench

Verilog Test BenchDr.YNM

Ã˝

This PPT is meant to explain the construction and implementation of Verilog Test Bench with examples.Introduction to VLSI

Introduction to VLSI illpa

Ã˝

This document provides an overview of VLSI design for a course. It discusses topics including CMOS transistors and logic gates, VLSI levels of abstraction, the VLSI design process, design styles like full custom and ASIC, and trends like Moore's Law. The roadmap outlines topics to be covered like CMOS processing, combinational and sequential circuit design, and a design project to complete a chip. Course objectives are listed relating to VLSI analysis, layout design, and system design skills.Soc architecture and design

Soc architecture and designSatya Harish

Ã˝

The document discusses system-on-chip (SOC) architectures and designs. It covers topics like different processor types (e.g. superscalar, VLIW), on-chip storage like caches and memory, interconnects like buses and networks-on-chip, and how SOCs are customized for applications like graphics, media, and security. Examples of SOCs include the iPhone SOC with an ARM processor and AMD's Barcelona multicore processor. The document also discusses design tradeoffs involving time, area, power, and costs as SOCs increase in complexity.Clk-to-q delay, library setup and hold time

Clk-to-q delay, library setup and hold timeVLSI SYSTEM Design

Ã˝

I have been receiving multiple queries on what is clk-to-q delay, how's it different from library setup time and library hold time, etc. I mentioned in my discussions, that the videos on CMOS digital circuit will be uploaded soon, but looks like, it might take some time, and hence decided to uploaded few images from my CMOS course, to explain the difference between all of them.Morello Technology Demonstrator Hardware Overview - Mark Inskip, Arm

Morello Technology Demonstrator Hardware Overview - Mark Inskip, ArmKTN

Ã˝

Presentation from the briefing event for ISCF Digital Security by Design competition: Technology Enabled Business-Led Demonstator Stage 1 Expression of InterestHigh efficiency power amplifiers

High efficiency power amplifiersAbhishek Kadam

Ã˝

This document discusses high efficiency power amplifier technologies. It describes:

1) The requirements for future power amplifiers including high linearity, output power, bandwidth, and reduced energy consumption.

2) How switch-mode power amplifier technology using pulse width modulation can achieve up to 90% efficiency but is limited to low frequencies.

3) Different classes of switch-mode power amplifier operation (Class D, E, and F) and how they work to achieve high efficiency by minimizing voltage-current overlap losses.

4) Performance comparisons of different technologies like GaN and LDMOS transistors, noting advantages like bandwidth and efficiency of GaN for radio applications.VLSI technology

VLSI technologyAidell2583

Ã˝

It was a company which designed and manufactured custom and semi-custom Ics."Are you looking best Real time final year engineering projects for ece in bangalore.embedded innovation lab is the right place."Catalog Feeo Solar

Catalog Feeo SolarHUY HOANG TECHNOLOGY JOINT STOCK COMPANY

Ã˝

This document provides information on YUEQING FEEO ELECTRIC CO.,LTD, a professional solar PV electric components manufacturer located in Yueqing City, China. It introduces their FEO-63 Solar DC Mini Circuit Breaker (DC MCB), including its specifications, applications, characteristic curve, dimensions, and connection details. The FEO-63 is designed to provide overcurrent protection within appliances or electrical equipment for direct current applications, with a rated operating voltage range of DC12V - DC1000V and rated current from 1A to 63A.SISTec Microelectronics VLSI design

SISTec Microelectronics VLSI designDr. Ravi Mishra

Ã˝

The document discusses trends in integration technologies such as VLSI. It describes how VLSI has allowed for more compact, lower power, and higher speed integrated circuits. It classifies integrated circuits based on application, fabrication technique, technology, and device count. It then discusses the history of integrated circuits from the transistor in 1947 to modern chips containing tens of millions of transistors. It outlines drivers for VLSI technology including smaller sizes, lower power, and reduced costs.Implementing Useful Clock Skew Using Skew Groups

Implementing Useful Clock Skew Using Skew GroupsM Mei

Ã˝

Implementing useful skew through skew groups or manual buffer insertion can improve timing in a large memory block design. Skew groups define a target skew value for groups of clock pins before clock tree synthesis, resulting in a smaller clock tree, lower power increase, and less routing complexity compared to manual buffer insertion. Manual insertion precisely controls skew by adding buffers but dramatically increases clock cell count and power consumption versus skew groups. Both methods effectively improved setup timing for the memory block design.VLSI UNIT-1.1.pdf.ppt

VLSI UNIT-1.1.pdf.pptrajukolluri

Ã˝

VLSI design involves integrating millions of transistors onto a single chip. There are various design styles including full custom, standard cell, gate array, and FPGA. Full custom designs have fully customized cells and layouts but require more design time. Standard cell and gate array styles use predesigned cells, reducing design time but only customizing interconnect layers. FPGA designs have no custom masks and the fastest design turnaround time.Viewers also liked (9)

Ic tech unit 5- VLSI Process Integration

Ic tech unit 5- VLSI Process Integrationkriticka sharma

Ã˝

junction oxide and isolation techniques, LOCOS, Metallization, NMOS and CMOS technology, FAult diagnosisCMOS Topic 6 -_designing_combinational_logic_circuits

CMOS Topic 6 -_designing_combinational_logic_circuitsIkhwan_Fakrudin

Ã˝

This document discusses designing combinational logic circuits using static complementary CMOS design. It explains how to construct static CMOS circuits for logic gates like NAND and NOR by using pull-up and pull-down networks of PMOS and NMOS transistors respectively. Issues related to pass-transistor design like noise margins and static power consumption are also covered. The document provides details on implementing various logic functions using pass-transistor logic and differential pass-transistor logic. It discusses solutions to overcome the disadvantages of pass-transistor logic like level restoration and use of multiple threshold transistors.9.sequential+circuits part+1

9.sequential+circuits part+1 liran1018

Ã˝

This document discusses sequential circuit design and various memory element designs. It covers topics such as static and dynamic latches, flip-flops, timing parameters, two-phase clocking, and clocked inverters. Memory elements store information by using positive feedback or charge-based storage. Two-phase clocking employs two non-overlapping clocks to avoid race conditions in master-slave designs. Clocked inverters act as inverters when enabled and provide a high impedance output when disabled.IS 151 Lecture 9

IS 151 Lecture 9wajanga

Ã˝

This document discusses basic combinational logic functions including adders, comparators, decoders, and encoders. It begins by explaining half adders and full adders, including their truth tables and logic expressions. It then covers parallel binary adders used to add multi-bit numbers. Comparators are introduced for comparing the magnitude of two binary quantities. Decoders and encoders are also discussed, with decoders detecting a specified input code and encoders performing the reverse by converting an input to a coded output. Examples and exercises are provided to illustrate the concepts.Vlsi design mosfet

Vlsi design mosfetvennila12

Ã˝

Here are the key points about NMOS transistor operation in the subthreshold region:

- When 0 < Vgs < Vt, a depletion region forms in the channel due to the electric field repelling majority carriers (holes).

- This depletion region means there are no carriers to conduct current through the channel.

- Only a small leakage current flows, as the channel is not fully "turned on".

- The transistor is not fully on or off in this region - it is said to be weakly inverted. Current has an exponential relationship with Vgs.

- Some applications exploit this behavior for very low power analog/digital circuits.

So in summary, a small current flows due to weak inversion in theLecture11 combinational logic dynamics

Lecture11 combinational logic dynamicsvidhya DS

Ã˝

- The document discusses various techniques for designing fast complex logic gates in VLSI circuits.

- Two transistor sizing techniques are presented: progressive transistor sizing and transistor ordering to reduce signal delay.

- Alternative logic structures, buffer insertion, and reducing voltage swing are additional techniques described.

- The concept of logical effort is introduced as a way to optimize logic paths for speed based on the topology rather than transistor sizing.Pass Transistor Logic

Pass Transistor LogicDiwaker Pant

Ã˝

This document compares the use of complementary pass-transistor logic (CPL) to conventional CMOS design. CPL uses fewer transistors than CMOS gates, has smaller capacitances, and is faster. A 2:1 multiplexer is designed using both CMOS and CPL in Microwind and DSCH2 layout tools. Simulation results show the CPL multiplexer has lower power consumption, smaller area, faster rise/fall delays compared to the CMOS multiplexer. Therefore, CPL offers advantages over conventional CMOS in terms of speed, area, and power-delay products.Analog vlsi

Analog vlsiKhuong Lamborghini

Ã˝

This document provides an overview of an "Analog VLSI Design" course. The goals of the course are to introduce principles of analog integrated circuit design and CMOS technology. Students will learn about CMOS layout design using CAD tools and complete a design project. The course covers topics including CMOS technology, resistors, capacitors, MOSFETs, current mirrors, amplifiers, and data converters. Assessment includes homework, a project, and a final exam.Pass transistor logic

Pass transistor logicTripurna Chary

Ã˝

The document discusses pass transistor logic circuits. It describes how nMOS pass transistors can transfer logic 1 and 0 signals. Transmission gates are introduced which use both nMOS and pMOS pass transistors to pass strong signals in both directions. Applications of transmission gates include multiplexers, XOR gates, D latches, and D flip-flops. Clock skew management and different pass transistor logic families are also covered.Similar to vlsi (20)

Semiconductor overview

Semiconductor overviewNabil Chouba

Ã˝

The document provides an overview of the history and evolution of semiconductors and integrated circuits from 1947 to present. It discusses key inventions and milestones such as the transistor in 1947, the integrated circuit in 1961, and Moore's Law predicting transistor doubling every two years. It also covers different chip design approaches including full custom, standard cell, gate arrays, and FPGAs, along with their relative costs, performance, and design complexities.VLSI unit 1 Technology - S.ppt

VLSI unit 1 Technology - S.pptindrajeetPatel22

Ã˝

This document outlines the course contents for a VLSI Design course. The course covers six units: (1) an introduction to VLSI design including Moore's Law and design challenges, (2) VLSI circuit design processes and technologies, (3) analysis of CMOS logic circuits, (4) advanced CMOS logic circuit techniques, (5) memories, and (6) testing and testability. The goal of the course is to provide students with knowledge of very large scale integration circuits, which are essential components in modern electronic devices.My profile

My profiledhruv_63

Ã˝

Ratan Devpura is passionate about analog and mixed-signal circuit design. He has worked on amplifier, ADC, and DAC designs for mixed-signal systems. As an intern, he worked on migrating analog circuits to newer process technologies and verifying circuit simulation tools. He holds an M.S. in electrical engineering and aims to become an outstanding circuit design engineer through continued learning and innovative analog circuit designs.Chapter_01 Course Introduction.pdf

Chapter_01 Course Introduction.pdfVoThanhPhong3

Ã˝

This document outlines a course on FPGA and ASIC design using Verilog. The course is taught by Associate Professor Truong Ngoc Son at the Department of Computer and Communication Engineering. The course covers Verilog coding, simulation, synthesis, FPGA implementation, and the full ASIC design flow. Students will learn design methodologies and use software tools like Xilinx ISE and synthesis tools. The goal is for students to understand the process of taking a design from idea to implementation on FPGAs or as an actual chip.VLSI Design- Guru.ppt

VLSI Design- Guru.pptRam Pavithra Guru

Ã˝

This document provides an introduction to VLSI design. It begins by defining VLSI as circuits containing over a million switching devices or logic gates. It then discusses the evolution of integrated circuits from SSI to VLSI and the trends in IC technology. The key advantages of MOS technology over BJT are summarized. The document outlines Moore's Law and provides evidence of its accuracy. It introduces the structured design methodology and top-down, bottom-up approaches. The various stages of the VLSI design flow and physical design cycle are described at a high level. Different design styles including full-custom, standard cell-based, and programmable logic are also summarized.Introduction to EDA Tools

Introduction to EDA Toolsvenkatasuman1983

Ã˝

This document provides an introduction to electronic design automation (EDA) tools and discusses different types of programmable logic devices including field programmable gate arrays (FPGAs) and complex programmable logic devices (CPLDs). It describes the basic architecture of FPGAs including logic blocks, interconnects, and input/output blocks. The advantages of FPGAs such as shorter development time and flexibility are also summarized.Implementation strategies for digital ics

Implementation strategies for digital icsaroosa khan

Ã˝

The document discusses various digital integrated circuit design implementation strategies. It describes very large scale integration (VLSI) and the VLSI design cycle. It then covers Moore's law, productivity growth rates, and two main design implementation strategies - full custom circuit design and standard cell-based semi-custom design. The document provides details on standard cell libraries, floorplanning, gate arrays, and field programmable gate arrays (FPGAs), and concludes with a comparison of the different design styles.Very Large Scale Integrated Circuits VLSI Overview

Very Large Scale Integrated Circuits VLSI OverviewEngr. Bilal Sarwar

Ã˝

VLSI stands for Very Large Scale Integrated Circuits.

SSI – Small Scale Integration (50s and 60s)

1 – 10 transistors

Simple logic gates

MSI – Medium Scale Integration(70s)

10-100 transistors

logic functions, counters, etc

LSI – Large Scale Integration(80s)

100-10,000 transistors

First microprocessors on the chip

Resume

Resumejaydippatel

Ã˝

This document is a resume for Jaydip Patel seeking an internship or entry-level position in VLSI design and validation. It summarizes his education, including an M.S. in Electrical and Electronics Engineering from California State University, Sacramento and a B.S. in Electronics and Communication Engineering from Gujarat University, India. It also lists relevant coursework, professional experience including internships, tools and software skills, and projects in analog and mixed signal design, logic design, computer architecture, and VLSI validation and testing.L1 introduction

L1 introductionpooja bagde

Ã˝

The document provides an introduction to VLSI (Very Large Scale Integration) design. It discusses the evolution of integrated circuits from early computers to modern microprocessors containing billions of transistors. The key aspects of VLSI design covered include CMOS technology, the VLSI design process involving multiple levels of abstraction, design methodologies, CAD tools, and emerging technologies. Future trends in scaling, performance, power and integration density based on the semiconductor industry roadmap are also summarized.Asic

Asicrajeevkr35

Ã˝

Application specific integrated circuits (ASICs) are microchips designed for special applications. There are two types: full-custom ASICs where all logic cells and mask layers are customized, and semi-custom where pre-designed logic cells have some customizable mask layers. ASICs have advantages over FPGAs like lower costs, higher speeds, and lower power usage, but have higher design costs and longer development times. Common applications of ASICs include aerospace systems, high-performance processors, and specialized consumer electronics.Unit-4_ESE.pdf

Unit-4_ESE.pdfSouravRoyElectronics

Ã˝

This document describes the ASIC design flow, including various design methodologies like full custom, standard cell, and gate array. It discusses the front-end design steps like specifications, design entry, functional verification, and synthesis. It also covers back-end steps like floorplanning, placement, routing, timing analysis, and GDS-II generation. Key techniques like design for test (DFT), scan insertion, and formal verification are also summarized. The document provides an overview of the complete digital ASIC design process.1st and 2nd Lecture

1st and 2nd Lecturebabak danyal

Ã˝

The document discusses different types of application specific integrated circuits (ASICs). It describes ASICs as integrated circuits customized for a particular application, such as chips for toys or automotive controls, as opposed to standard integrated circuits. The document summarizes that there are two main types of ASICs: full-custom ASICs that have all logic cells and mask layers customized, and semi-custom ASICs that use pre-designed logic cells with some customized mask layers. Within semi-custom ASICs, the document outlines different design approaches such as standard cell-based and gate array-based designs, as well as programmable ASICs like PLDs, CPLDs, and FPGAsAsic design lect1 2 august 28 2012

Asic design lect1 2 august 28 2012babak danyal

Ã˝

The document discusses different types of application specific integrated circuits (ASICs). It describes ASICs as integrated circuits customized for a particular application, as opposed to standard integrated circuits. The document outlines two main types of ASICs: full-custom ASICs which have all logic cells and mask layers customized, and semi-custom ASICs which use pre-designed logic cells but have customized mask layers. Within semi-custom ASICs it distinguishes between standard cell-based and gate array-based designs. The document also covers programmable ASICs including PLDs, CPLDs and FPGAs.Hard IP Core design | Convolution Encoder

Hard IP Core design | Convolution EncoderArchit Vora

Ã˝

Presentation of our major project during b.tech. Staring from requirements, we had developed soft ip and then hard ip for convolution encoder.Introduction to VLSI

Introduction to VLSIShams Tabrej

Ã˝

The document provides an overview of VLSI (very large scale integration) and the history and evolution of integrated circuits. It discusses key concepts like Moore's Law and scaling and summarizes different IC technologies like CMOS. It also covers IC design approaches including full custom, standard cells, gate arrays, macro cells and FPGAs and how they tradeoff factors like density, performance and design time/cost.M Tech New Syllabus(2012)

M Tech New Syllabus(2012)BGS Institute of Technology, Adichunchanagiri University (ACU)

Ã˝

This document provides information about the CMOS VLSI Design course. It outlines the course code, credit hours, exam details, and topics to be covered. The topics include MOS transistor theory, CMOS process technology, digital CMOS design including combinational and sequential logic circuits, analog CMOS design including amplifiers, and dynamic CMOS and clocking. It also lists reference books and laboratory experiments involving digital and analog design using EDA tools. The experiments involve designing circuits like inverters, adders, counters, and completing the full ASIC design flow from schematic to layout.Lecture20 asic back_end_design

Lecture20 asic back_end_designHung Nguyen

Ã˝

This document provides an overview of the ASIC back-end design flow, including timing driven placement. It discusses the inputs to the Astro placement and routing tool, including the gate-level netlist, standard cell library, and timing constraints. It describes key aspects of the placement process, including floorplanning, placement rows, and timing driven placement to optimize critical paths. The goal is to meet all timing constraints by balancing timing, area, power, and signal integrity.vlsi

- 1. Introduction to VLSI Design V. Jagathi M Tech , VLSI DESIGN SRM University

- 2. Overview  VLSI Overview  Transistor Structure  Static CMOS Logic  VLSI Trends

- 3. Objectives VLSI Circuit Analysis:  Understand MOS transistor operation, design eqns.  Understand parasitic & perform simple calculations  Understand static & dynamic CMOS logic  Estimate delay of CMOS gates, networks, & long wires  Estimate power consumption  Understand design and operation of latches & flip/flops

- 4. Objectives  CMOS Processing and Layout  Understand the VLSI manufacturing process.  Have an appreciation of current trends in VLSI manufacturing.  Understand layout design rules.  Design and analyze layouts for simple digital CMOS circuits  Design and analyze hierarchical circuit layouts.  Understand ASIC Layout styles.

- 5. VLSI Overview  Why Make IC  IC Evolution  Common technologies  CMOS Transistors & Logic Gates  Structure  “Switch-Level” Transistor Model  Basic gates  The VLSI Design Process  Levels of Abstraction  Design steps  Design styles  VLSI Trends

- 6. Why IC’s are Important  Integration improves  size  speed  power  Integration reduce manufacturing costs  (almost) no manual assembly

- 7. IC Evolution  SSI – Small Scale Integration (early 1970s)  contained 1 – 10 logic gates  MSI – Medium Scale Integration  logic functions, counters  LSI – Large Scale Integration  first microprocessors on the chip  VLSI – Very Large Scale Integration  now offers 64-bit microprocessors, complete with cache memory (L1 and often L2), floating-point arithmetic unit(s), etc.

- 8. IC Evolution  Bipolar technology  TTL (transistor-transistor logic)  ECL (emitter-coupled logic)  MOS (Metal-oxide-silicon)  although invented before bipolar transistor, was initially difficult to manufacture  nMOS (n-channel MOS) technology developed in 1970s required fewer masking steps, was denser, and consumed less power than equivalent bipolar ICs.

- 9. IC Evolution  aluminum gates for replaced by polysilicon by early 1980  CMOS (Complementary MOS): n-channel and p- channel MOS transistors => lower power consumption, simplified fabrication process  Bi-CMOS - hybrid Bipolar, CMOS (for high speed)  GaAs - Gallium Arsenide (for high speed)  Si-Ge - Silicon Germanium (for RF)

- 10. Silicon Manufacturing Alternatives Standard Components Application Specific ICs Fixed Application Application by Programming Semi Custom Silicon Compilation Full Custom Logic Families Hardware Programming (MASK) Software Programming TTL CMOS PLA ROM Microprocessor EPROM,EEPROM PLD

- 11. VLSI Technology - CMOS Transistors Key feature: transistor length L p+ p+ n substrate channel Source Drain p transistor G S D SB Polysilicon Gate SiO 2 Insulator L W G substrate connected to VDD Polysilicon Gate SiO 2 Insulator n+ n+ p substrate channel Source Drain n transistor G S D SB L W G S D substrate connected to GND 2002: L=130nm 2003: L=90nm 2005: L=65nm?

- 12. Transistor Switch Model  NFET or n transistor  on when gate H  "good" switch for logic L  "poor" switch for logic H  "pull-down" device  PFET or p transistor  on when gate L  "good" switch for logic H  "poor" switch for logic L  "pull-up" device L H L L L L H L H H OFF when gate=L ON when gate=H OFF when gate=H ON when gate=L

- 13. CMOS Logic Design  Complementary transistor networks  Pullup: p transistors  Pulldown - n transistors VDD Out Gnd VDD Out Gnd Pullup Network (p-transistors) Pulldown Network (n-transistors) InInputs Inverter

- 14. CMOS Inverter Operation V DD L Gnd H O N O FF V DD H Gnd L O FF O N

- 15. CMOS Logic Example A B A B O UT +V DD GND P Transistors on when gate “L” N Transistors on when gate “H” A B O UT NA ND

- 16. VLSI Levels of Abstraction Specification (what the chip does, inputs/outputs) Architecture major resources, connections Register-Transfer logic blocks, FSMs, connections Circuit transistors, parasitics, connections Layout mask layers, polygons Logic gates, flip-flops, latches, connections

- 17. The VLSI Design Process  Move from higher to lower levels of abstraction  Use CAD tools to automate parts of the process  Use hierarchy to manage complexity  Different design styles trade off: Design time Non-recurring engineering (NRE) cost Unit cost Performance Power Consumption

- 18. VLSI Design Tradeoffs  Non-Recurring Engineering (NRE) Costs Design Costs Mask “Tooling” costs  Unit Cost - related to chip size Amount of logic Current technology  Performance Clock speed Implementation

- 19. VLSI Design Tradeoffs  Power consumption - a relatively new concern  Power supply voltage  Clock speed

- 20. VLSI Design Styles  Full Custom  Application-Specific Integrated Circuit (ASIC)  Programmable Logic (PLD, FPGA)  System-on-a-Chip

- 21. Full Custom Design  Each circuit element carefully “handcrafted”  Huge design effort  High Design & NRE Costs / Low Unit Cost  High Performance  Typically used for high-volume applications

- 22. Application-Specific Integrated Circuit (ASIC)  Constrained design using pre-designed (and sometimes pre-manufactured) components  Also called semi-custom design  CAD tools greatly reduce design effort  Low Design Cost / High NRE Cost / Med. Unit Cost  Medium Performance

- 23. Programmable Logic (PLDs, FPGAs)  Pre-manufactured components with programmable interconnect  CAD tools greatly reduce design effort  Low Design Cost / Low NRE Cost / High Unit Cost  Lower Performance

- 24. System-on-a-chip (SOC)  Idea: combine several large blocks  Predesigned custom cores (e.g., microcontroller) - “intellectual property” (IP)  ASIC logic for special-purpose hardware  Programmable Logic (PLD, FPGA)  Analog  Open issues  Keeping design cost low  Verifying correctness of design

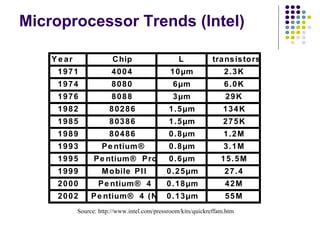

- 25. Microprocessor Trends (Intel) Y e ar Chip L transistors 1971 4004 10µm 2.3K 1974 8080 6µm 6.0K 1976 8088 3µm 29K 1982 80286 1.5µm 134K 1985 80386 1.5µm 275K 1989 80486 0.8µm 1.2M 1993 Pe ntium® 0.8µm 3.1M 1995 Pe ntium® Pro 0.6µm 15.5M 1999 Mobile PII 0.25µm 27.4 2000 Pe ntium® 4 0.18µm 42M 2002 Pe ntium® 4 (N) 0.13µm 55M Source: http://www.intel.com/pressroom/kits/quickreffam.htm

- 26. Trends in VLSI  Transistor Smaller, faster, use less power  Interconnect Less resistive, faster, longer (denser design)  Yield Smaller die size, higher yield

- 27. Power and Noise  Huge power consumption and heat dissipation becomes a problem  Noise and cross talk.  Solutions: Better physical design

- 28. Interconnect Delay  Interconnect delay becomes a dominating factor in circuit performance  Solutions: Use copper wire Interconnect optimization in physical design, e.g., wire sizing, buffer insertion, buffer sizing.

- 29. Interconnect Delay 0.65 1989 0.5 1992 0.35 1995 0.25 1998 0.18 2001 0.13 2004 0.1 2007 0 5 10 15 20 25 30 35 40 Gate delay Interconnect delay Source: SIA Roadmap 1997