High-speed Sorting using Portable FPGA Accelerator (IPSJ 77th National Convention, March 2015)

- 1. ╩ų▌Xż╩═ŌĖČż▒FPGAźóź»ź╗źķźņ®`ź┐ż╦żĶżļ źĮ®`źŲźŻź¾ź░ż╬Ė▀╦┘╗» 2015/03/18 Ūķł¾äI└Ēč¦╗ß Ą┌77╗ž╚½╣·┤¾╗ß @Š®Č╝┤¾č¦╝¬╠’źŁźŃź¾źčź╣ FPGAż╚źóź»ź╗źķźņ®`ź┐[3K╗ßł÷] ░k▒Ē12Ęų + ┘|ę╔ÅĻ┤3Ęų ĪŅŠ╩Š« ū┴šµ?1 ╝¬×ü ųtČ■?2 ?1 ¢|Š®╣żśI┤¾č¦ ╣żč¦▓┐Ūķł¾╣żč¦┐Ų ?2¢|Š®╣żśI┤¾č¦ ┤¾č¦į║Ūķł¾└Ē╣żč¦čąŠ┐┐Ų High-speed Sorting using Portable FPGA Accelerator

- 2. ░k▒Ēż╬┴„żņ ?Motivation ?FPGA-ź█ź╣ź╚ķgż╬źżź¾ź┐®`źšź¦®`ź╣Ś╩ėæ ?╠ß░Ėż╣żļFPGAźĮ®`źŲźŻź¾ź░źóź»ź╗źķźņ®`ź┐ ?Ė┼ę¬ ?Merge Sorter Tree, System Architecture ?īgū░?Ś╩į^ ?įuü² ?įuü²ŁhŠ│ ?źóź»ź╗źķźņ®`ź┐ż╬ąį─▄įuü² ?ĮYšō?Į±ßßż╬šnŅ} 1

- 3. ░k▒Ēż╬┴„żņ ?Motivation ?FPGA-ź█ź╣ź╚ķgż╬źżź¾ź┐®`źšź¦®`ź╣Ś╩ėæ ?╠ß░Ėż╣żļFPGAźĮ®`źŲźŻź¾ź░źóź»ź╗źķźņ®`ź┐ ?Ė┼ę¬ ?Merge Sorter Tree, System Architecture ?īgū░?Ś╩į^ ?įuü² ?įuü²ŁhŠ│ ?źóź»ź╗źķźņ®`ź┐ż╬ąį─▄įuü² ?ĮYšō?Į±ßßż╬šnŅ} 2

- 5. ░k▒Ēż╬┴„żņ ?Motivation ?FPGA-ź█ź╣ź╚ķgż╬źżź¾ź┐®`źšź¦®`ź╣Ś╩ėæ ?╠ß░Ėż╣żļFPGAźĮ®`źŲźŻź¾ź░źóź»ź╗źķźņ®`ź┐ ?Ė┼ę¬ ?Merge Sorter Tree, System Architecture ?īgū░?Ś╩į^ ?įuü² ?įuü²ŁhŠ│ ?źóź»ź╗źķźņ®`ź┐ż╬ąį─▄įuü² ?ĮYšō?Į±ßßż╬šnŅ} 5

- 6. FPGA-ź█ź╣ź╚PCķgż╬źżź¾ź┐®`źšź¦®`ź╣▒╚▌^ USB3.0żŽŻ¼═ŌĖČż▒źżź¾ź┐®`źšź¦®`ź╣ż╬ųążŪżŌ ?ĮėŠAż¼ĘŪ│Żż╦╚▌ęūżŪŻ¼śöĪ®ż╩ŁhŠ│żŪ╩╣ż©żļ ?PCI Express x1 ż╦Ų╚żļĖ▀żż▄×╦═╦┘Č╚ ?═©ą┼╦┘Č╚ż¼ź▄ź╚źļź═ź├ź»ż╦ż╩żĻż╦ż»żż Ī·USB3.0ż“▀xÆk 6 ĮėŠAĘĮĘ© USB3.0 USB2.0 UART Ethernet PCI Express ūŅĖ▀╦┘Č╚(└ĒšōéÄ) 5Gbps 480Mbps ╩²Mbps 1Gbps@GbE 10Gbps@XGbE 8GB/s@2.0 x8 1GB/s@2.0 x1 ─┌╩i/═ŌĖČ ═ŌĖČ ═ŌĖČ ═ŌĖČ ═ŌĖČ ─┌╩i ūŅą┬PCżŪż╬Ųš╝░┬╩ Ī Ī Ī┴ Ī┴(XGbE) Ī„ ź█ź├ź╚ź╣ź’ź├źū Ī Ī Ī┴ Ī Ī źąź╣źčź’®` 900mA,5V 500mA,5V Ī┴ Ī┴ 25/75W@x16

- 7. ░k▒Ēż╬┴„żņ ?Motivation ?FPGA-ź█ź╣ź╚ķgż╬źżź¾ź┐®`źšź¦®`ź╣Ś╩ėæ ?╠ß░Ėż╣żļFPGAźĮ®`źŲźŻź¾ź░źóź»ź╗źķźņ®`ź┐ ?Ė┼ę¬ ?Merge Sorter Tree, System Architecture ?īgū░?Ś╩į^ ?įuü² ?įuü²ŁhŠ│ ?źóź»ź╗źķźņ®`ź┐ż╬ąį─▄įuü² ?ĮYšō?Į±ßßż╬šnŅ} 7

- 8. ░k▒Ēż╬┴„żņ ?Motivation ?FPGA-ź█ź╣ź╚ķgż╬źżź¾ź┐®`źšź¦®`ź╣Ś╩ėæ ?╠ß░Ėż╣żļFPGAźĮ®`źŲźŻź¾ź░źóź»ź╗źķźņ®`ź┐ ?Ė┼ę¬ ?Merge Sorter Tree, System Architecture ?īgū░?Ś╩į^ ?įuü² ?įuü²ŁhŠ│ ?źóź»ź╗źķźņ®`ź┐ż╬ąį─▄įuü² ?ĮYšō?Į±ßßż╬šnŅ} 8

- 10. ░k▒Ēż╬┴„żņ ?Motivation ?FPGA-ź█ź╣ź╚ķgż╬źżź¾ź┐®`źšź¦®`ź╣Ś╩ėæ ?╠ß░Ėż╣żļFPGAźĮ®`źŲźŻź¾ź░źóź»ź╗źķźņ®`ź┐ ?Ė┼ę¬ ?Merge Sorter Tree, System Architecture ?īgū░?Ś╩į^ ?įuü² ?įuü²ŁhŠ│ ?źóź»ź╗źķźņ®`ź┐ż╬ąį─▄įuü² ?ĮYšō?Į±ßßż╬šnŅ} 10

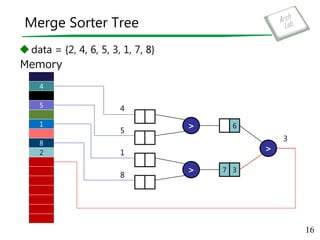

- 11. ?č}╩²ż╬źĮ®`ź╚£gż▀źŪ®`ź┐┴ąż“1ż─ż╦ź▐®`źĖż╣żļźŪ®`ź┐źčź╣ ?ćĒżŽ 4-way Merge Sorter Tree ?źĮ®`ź╚īØŽ¾ż╬źŪ®`ź┐┴ąż¼╚ļ┴”╩²żĶżĻČÓżżł÷║ŽżŽč}╩²╗ž═©ż╣▒žę¬ Merge Sorter Tree 11 ▓╬┐╝: A high performance sorting architecture exploiting run-time reconfiguration on fpgas for large problem sorting. (Dirk Koch and Jim Torresen, FPGA Ī»11,) > > > > Comparator Short FIFO ╚ļ┴”źņ®`ź¾ = way

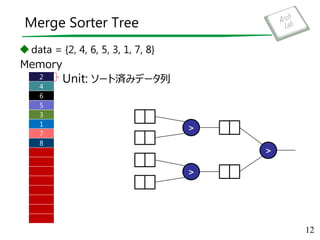

- 12. Merge Sorter Tree ?data = {2, 4, 6, 5, 3, 1, 7, 8} 12 2 Memory > > > 4 6 5 3 1 7 8 Unit: źĮ®`ź╚£gż▀źŪ®`ź┐┴ą

- 13. Merge Sorter Tree ?data = {2, 4, 6, 5, 3, 1, 7, 8} 13 Memory > > > 2 6 3 7 8 2 4 6 5 3 1 7

- 14. Merge Sorter Tree ?data = {2, 4, 6, 5, 3, 1, 7, 8} 14 Memory > > > 2 6 3 7 4 5 1 8 3 2 8 4 5 1

- 15. Merge Sorter Tree ?data = {2, 4, 6, 5, 3, 1, 7, 8} 15 Memory > > > 6 7 2 3 7 6 2 8 4 5 1 8 4 5 1

- 16. Merge Sorter Tree ?data = {2, 4, 6, 5, 3, 1, 7, 8} 16 Memory > > > 6 37 3 8 2 4 5 1 8 4 5 1

- 17. Merge Sorter Tree ?data = {2, 4, 6, 5, 3, 1, 7, 8} 17 Memory > > 6 7 6 8 2 3 > 4 5 1 8 4 5 1

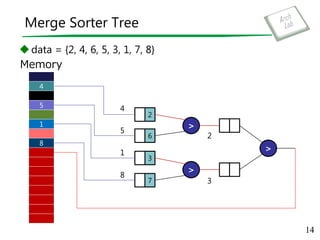

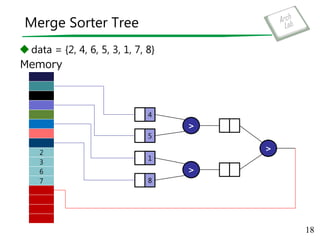

- 18. Merge Sorter Tree ?data = {2, 4, 6, 5, 3, 1, 7, 8} 18 Memory > > > 4 5 1 8 2 3 6 7

- 19. Merge Sorter Tree ?data = {2, 4, 6, 5, 3, 1, 7, 8} 19 Memory > > > 1 4 5 8 ═Ļ╚½ż╦żŽźĮ®`ź╚żĄżņżŲż¬żķż║ żŌż”ę╗Č╚═©ż╣▒žę¬ Unit Unit Unit╩²żŽ1/[way╩²] ż╚ż╩żļ 2 3 6 7

- 20. Merge Sorter Tree ?data = {2, 4, 6, 5, 3, 1, 7, 8} 20 Memory > > > 1 2 3 4 5 6 7 8

- 23. ░k▒Ēż╬┴„żņ ?Motivation ?FPGA-ź█ź╣ź╚ķgż╬źżź¾ź┐®`źšź¦®`ź╣Ś╩ėæ ?╠ß░Ėż╣żļFPGAźĮ®`źŲźŻź¾ź░źóź»ź╗źķźņ®`ź┐ ?Ė┼ę¬ ?Merge Sorter Tree, System Architecture ?īgū░?Ś╩į^ ?įuü² ?įuü²ŁhŠ│ ?źóź»ź╗źķźņ®`ź┐ż╬ąį─▄įuü² ?ĮYšō?Į±ßßż╬šnŅ} 23

- 24. ╠žļŖ Artix-7 įuü²ź▄®`ź╔ 24 72mm 50mm USB3.0 Peripheral Controller │ųż┴▀\ż┘żļ

- 25. USB3.0ż╬═©ą┼╦┘Č╚ 25 0.25 3.84 39.1 221 330 354 0.13 2.04 25.1 196 334 355 0 50 100 150 200 250 300 350 400 16 Bytes 256 Bytes 4K Bytes 64K Bytes 1M Bytes 16M Bytes Bandwidth[MB/s] Data Size Host PC Ī· FPGA FPGA Ī· Host PC ╣½│ŲŽ▐ĮńéÄ: 360[MB/s] Į±╗žźĮ®`ź╚īØŽ¾ż╬źŪ®`ź┐┴ążŽ32Mę¬╦žżŪ128MB Ž▐Įń▄×╦═╦┘Č╚▀_│╔ż╬ęŖ▐zż▀

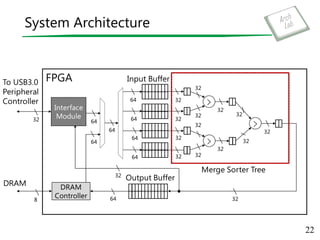

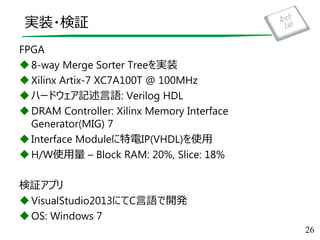

- 26. īgū░?Ś╩į^ FPGA ?8-way Merge Sorter Treeż“īgū░ ?Xilinx Artix-7 XC7A100T @ 100MHz ?źŽ®`ź╔ź”ź¦źóėø╩÷čįšZ: Verilog HDL ?DRAM Controller: Xilinx Memory Interface Generator(MIG) 7 ?Interface Moduleż╦╠žļŖIP(VHDL)ż“╩╣ė├ ?H/W╩╣ė├┴┐ ©C Block RAM: 20%, Slice: 18% Ś╩į^źóźūźĻ ?VisualStudio2013ż╦żŲCčįšZżŪķ_░k ?OS: Windows 7 26

- 27. 27 Ś╩į^źóźūźĻź│®`ź╔Ė┼┬į 01:#define ELM = 32*1024*1024; 02:int data[ELM]; 03: 04:int (main){ 05: init(data); // źŪ®`ź┐┴ą╔·│╔?│§Ų┌╗» 06: 07: start = getTime(); 08: USBWrite(data,ELM); // Send 09: USBRead(data,ELM); // Receive 10: end = getTime(); 11: 12: errchk(); 13: elapsed_time = end ©C start; 14: display(elapsed_time); 15:} 01:#define ELM = 32*1024*1024; 02:int data[ELM]; 03: 04:int (main){ 05: init(data); 06: 07: start = getTime(); 08: MergeSort(data,0,ELM-1); 09: 10: end = getTime(); 11: 12: errchk(); 13: elapsed_time = end ©C start; 14: display(elapsed_time); 15:} FPGAźóź»ź╗źķźņ®`ź┐ż╦ źĮ®`źŲźŻź¾ź░żĄż╗żļł÷║Ž ź█ź╣ź╚PC╔Žż╬ż▀żŪ źĮ®`źŲźŻź¾ź░ż“ąąż”ł÷║Ž

- 28. ░k▒Ēż╬┴„żņ ?Motivation ?FPGA-ź█ź╣ź╚ķgż╬źżź¾ź┐®`źšź¦®`ź╣Ś╩ėæ ?╠ß░Ėż╣żļFPGAźĮ®`źŲźŻź¾ź░źóź»ź╗źķźņ®`ź┐ ?Ė┼ę¬ ?Merge Sorter Tree, System Architecture ?īgū░?Ś╩į^ ?įuü² ?įuü²ŁhŠ│ ?źóź»ź╗źķźņ®`ź┐ż╬ąį─▄įuü² ?ĮYšō?Į±ßßż╬šnŅ} 28

- 30. 4ĘNŅÉż╬įuü²ŁhŠ│ ©C Computer A 30 Core i7-3770K @3.50GHz 16GB DDR3 Memory Supports USB3.0 High Performance!

- 31. 4ĘNŅÉż╬įuü²ŁhŠ│ ©C Computer B 31 Supports USB3.0 Core i3-4010U @1.70GHz 4GB DDR3 Memory Portable!

- 32. 4ĘNŅÉż╬įuü²ŁhŠ│ ©C Computer C 32 Only supports USB2.0 Core i7-870 @2.93GHz 4GB DDR3 Memory

- 33. 4ĘNŅÉż╬įuü²ŁhŠ│ ©C Computer D 33 Core Duo T2400 @1.83GHz 1GB DDR2 Memory Only supports USB2.0

- 34. 0 2 4 6 8 10 12 CPU FPGA CPU FPGA CPU FPGA CPU FPGA Computer A Computer B Computer C Computer D ElapsedTime[s] Data Transfer Sorting only USB3.0 USB2.0 įuü²©Dintą═32MéĆż╬źĮ®`źŲźŻź¾ź░ 34

- 35. 0 2 4 6 8 10 12 CPU FPGA CPU FPGA CPU FPGA CPU FPGA Computer A Computer B Computer C Computer D ElapsedTime[s] Data Transfer Sorting only USB3.0 USB2.0 Ęų╬÷ 35 ąį─▄Ž“╔Ž▓╗┐╔─▄ ═©ą┼Ģrķg > CPUż╦ż¬ż▒żļźĮ®`źŲźŻź¾ź░Ģrķg

- 36. 0 2 4 6 8 10 12 CPU FPGA CPU FPGA CPU FPGA CPU FPGA Computer A Computer B Computer C Computer D ElapsedTime[s] Data Transfer Sorting only USB3.0 USB2.0 Ęų╬÷ 36 ═©ą┼Ģrķg ┤¾Ę∙£p USB3.0żŪ ąį─▄Ž“╔Ž

- 37. 4.12 3.27 8.67 3.28 0 2 4 6 8 10 CPU FPGA CPU FPGA Computer A Computer B ElapsedTime[s] įuü² @USB3.0ŁhŠ│ 37 2.64x Faster 1.26x Faster ?Merge Sorter Treeż“32-wayż╦ÆłÅłżĘComputer Aż╬CPU▒╚ 1.88▒Čż╬Ė▀╦┘╗»▀_│╔ śöĪ®ż╩ŁhŠ│żŪ ╩╣ż©żļ

- 38. ░k▒Ēż╬┴„żņ ?Motivation ?FPGA-ź█ź╣ź╚ķgż╬źżź¾ź┐®`źšź¦®`ź╣Ś╩ėæ ?╠ß░Ėż╣żļFPGAźĮ®`źŲźŻź¾ź░źóź»ź╗źķźņ®`ź┐ ?Ė┼ę¬ ?Merge Sorter Tree, System Architecture ?īgū░?Ś╩į^ ?įuü² ?įuü²ŁhŠ│ ?źóź»ź╗źķźņ®`ź┐ż╬ąį─▄įuü² ?ĮYšō?Į±ßßż╬šnŅ} 38

- 40. ░k▒Ē┬─Üs?ėĶČ© ?ļŖūėŪķł¾═©ą┼č¦╗ß蹊┐╗ß(RECONF) ░k▒Ē (2015/01/30) ?ĪĖUSB3.0ĮėŠAż╬╩ų▌XżŪĖ▀╦┘ż╩FPGAźóź»ź╗źķźņ®`ź┐Ī╣ ?Š╩Š« ū┴šµŻ¼ąĪ┴ų šÅŲĮŻ¼╝¬×ü ųtČ■ ?ARC 2015 POSTER SESSION (2015/04/15-17) ?Ī░A Challenge of Portable and High-speed FPGA AcceleratorĪ▒ ?Takuma USUI, Ryohei KOBAYASHI, Kenji KISE 40

![╩ų▌Xż╩═ŌĖČż▒FPGAźóź»ź╗źķźņ®`ź┐ż╦żĶżļ

źĮ®`źŲźŻź¾ź░ż╬Ė▀╦┘╗»

2015/03/18 Ūķł¾äI└Ēč¦╗ß Ą┌77╗ž╚½╣·┤¾╗ß @Š®Č╝┤¾č¦╝¬╠’źŁźŃź¾źčź╣

FPGAż╚źóź»ź╗źķźņ®`ź┐[3K╗ßł÷] ░k▒Ē12Ęų + ┘|ę╔ÅĻ┤3Ęų

ĪŅŠ╩Š« ū┴šµ?1 ╝¬×ü ųtČ■?2

?1 ¢|Š®╣żśI┤¾č¦ ╣żč¦▓┐Ūķł¾╣żč¦┐Ų

?2¢|Š®╣żśI┤¾č¦ ┤¾č¦į║Ūķł¾└Ē╣żč¦čąŠ┐┐Ų

High-speed Sorting using Portable FPGA Accelerator](https://image.slidesharecdn.com/zenkokuslideshare-150427062118-conversion-gate01/85/High-speed-Sorting-using-Portable-FPGA-Accelerator-IPSJ-77th-National-Convention-March-2015-1-320.jpg)

![Merge Sorter Tree

?data = {2, 4, 6, 5, 3, 1, 7, 8}

19

Memory

>

>

>

1

4

5

8

═Ļ╚½ż╦żŽźĮ®`ź╚żĄżņżŲż¬żķż║

żŌż”ę╗Č╚═©ż╣▒žę¬

Unit

Unit

Unit╩²żŽ1/[way╩²]

ż╚ż╩żļ

2

3

6

7](https://image.slidesharecdn.com/zenkokuslideshare-150427062118-conversion-gate01/85/High-speed-Sorting-using-Portable-FPGA-Accelerator-IPSJ-77th-National-Convention-March-2015-19-320.jpg)

![USB3.0ż╬═©ą┼╦┘Č╚

25

0.25 3.84

39.1

221

330

354

0.13 2.04

25.1

196

334

355

0

50

100

150

200

250

300

350

400

16 Bytes 256 Bytes 4K Bytes 64K Bytes 1M Bytes 16M Bytes

Bandwidth[MB/s]

Data Size

Host PC Ī· FPGA

FPGA Ī· Host PC

╣½│ŲŽ▐ĮńéÄ: 360[MB/s]

Į±╗žźĮ®`ź╚īØŽ¾ż╬źŪ®`ź┐┴ążŽ32Mę¬╦žżŪ128MB

Ž▐Įń▄×╦═╦┘Č╚▀_│╔ż╬ęŖ▐zż▀](https://image.slidesharecdn.com/zenkokuslideshare-150427062118-conversion-gate01/85/High-speed-Sorting-using-Portable-FPGA-Accelerator-IPSJ-77th-National-Convention-March-2015-25-320.jpg)

![27

Ś╩į^źóźūźĻź│®`ź╔Ė┼┬į

01:#define ELM = 32*1024*1024;

02:int data[ELM];

03:

04:int (main){

05: init(data); // źŪ®`ź┐┴ą╔·│╔?│§Ų┌╗»

06:

07: start = getTime();

08: USBWrite(data,ELM); // Send

09: USBRead(data,ELM); // Receive

10: end = getTime();

11:

12: errchk();

13: elapsed_time = end ©C start;

14: display(elapsed_time);

15:}

01:#define ELM = 32*1024*1024;

02:int data[ELM];

03:

04:int (main){

05: init(data);

06:

07: start = getTime();

08: MergeSort(data,0,ELM-1);

09:

10: end = getTime();

11:

12: errchk();

13: elapsed_time = end ©C start;

14: display(elapsed_time);

15:}

FPGAźóź»ź╗źķźņ®`ź┐ż╦

źĮ®`źŲźŻź¾ź░żĄż╗żļł÷║Ž

ź█ź╣ź╚PC╔Žż╬ż▀żŪ

źĮ®`źŲźŻź¾ź░ż“ąąż”ł÷║Ž](https://image.slidesharecdn.com/zenkokuslideshare-150427062118-conversion-gate01/85/High-speed-Sorting-using-Portable-FPGA-Accelerator-IPSJ-77th-National-Convention-March-2015-27-320.jpg)

![0

2

4

6

8

10

12

CPU FPGA CPU FPGA CPU FPGA CPU FPGA

Computer A Computer B Computer C Computer D

ElapsedTime[s]

Data Transfer

Sorting only

USB3.0

USB2.0

įuü²©Dintą═32MéĆż╬źĮ®`źŲźŻź¾ź░

34](https://image.slidesharecdn.com/zenkokuslideshare-150427062118-conversion-gate01/85/High-speed-Sorting-using-Portable-FPGA-Accelerator-IPSJ-77th-National-Convention-March-2015-34-320.jpg)

![0

2

4

6

8

10

12

CPU FPGA CPU FPGA CPU FPGA CPU FPGA

Computer A Computer B Computer C Computer D

ElapsedTime[s]

Data Transfer

Sorting only

USB3.0

USB2.0

Ęų╬÷

35

ąį─▄Ž“╔Ž▓╗┐╔─▄

═©ą┼Ģrķg > CPUż╦ż¬ż▒żļźĮ®`źŲźŻź¾ź░Ģrķg](https://image.slidesharecdn.com/zenkokuslideshare-150427062118-conversion-gate01/85/High-speed-Sorting-using-Portable-FPGA-Accelerator-IPSJ-77th-National-Convention-March-2015-35-320.jpg)

![0

2

4

6

8

10

12

CPU FPGA CPU FPGA CPU FPGA CPU FPGA

Computer A Computer B Computer C Computer D

ElapsedTime[s]

Data Transfer

Sorting only

USB3.0

USB2.0

Ęų╬÷

36

═©ą┼Ģrķg

┤¾Ę∙£p

USB3.0żŪ

ąį─▄Ž“╔Ž](https://image.slidesharecdn.com/zenkokuslideshare-150427062118-conversion-gate01/85/High-speed-Sorting-using-Portable-FPGA-Accelerator-IPSJ-77th-National-Convention-March-2015-36-320.jpg)

![4.12 3.27 8.67 3.28

0

2

4

6

8

10

CPU FPGA CPU FPGA

Computer A Computer B

ElapsedTime[s]

įuü² @USB3.0ŁhŠ│

37

2.64x

Faster

1.26x

Faster

?Merge Sorter Treeż“32-wayż╦ÆłÅłżĘComputer Aż╬CPU▒╚

1.88▒Čż╬Ė▀╦┘╗»▀_│╔

śöĪ®ż╩ŁhŠ│żŪ

╩╣ż©żļ](https://image.slidesharecdn.com/zenkokuslideshare-150427062118-conversion-gate01/85/High-speed-Sorting-using-Portable-FPGA-Accelerator-IPSJ-77th-National-Convention-March-2015-37-320.jpg)