21EC71_Floor Planning _PPT Electronics and communication engineering module 2

Download as PPTX, PDF0 likes13 views

Electronics and communication engineering module 2

1 of 13

Download to read offline

Recommended

Floor plan & Power Plan

Floor plan & Power Plan Prathyusha Madapalli

Ěý

The document discusses floor planning, which is the first step in physical design. It involves defining the size of the chip, pre-placing hard macros, I/O pads, and defining the power grid. A good floorplan partitions the design into functional blocks, arranges the blocks on the chip, places macros and I/O pads, and decides on the power distribution. Key inputs to floorplanning include the netlist, physical and timing libraries, timing constraints, and power requirements. The document then discusses various aspects of floorplanning such as die size calculations, macro placement guidelines, and different types of physical cells.Physical design-complete

Physical design-completeMurali Rai

Ěý

This document discusses various concepts related to physical design implementation. It describes the inputs and outputs of physical design tools, important checks to perform before starting design such as clock and high fanout net budgeting, and concepts like floorplanning, placement, routing, libraries, multi-voltage design, and clock tree synthesis and optimization.VLSI Physical Design Physical Design Concepts

VLSI Physical Design Physical Design ConceptsJason J Pulikkottil

Ěý

VLSI Physical Design Physical Design Concepts Question BankFloorplanning Power Planning and Placement

Floorplanning Power Planning and PlacementJason J Pulikkottil

Ěý

Floorplanning Power Planning and PlacementFloorplan, Powerplan and Data Setup, Stages

Floorplan, Powerplan and Data Setup, StagesJason J Pulikkottil

Ěý

Floorplan, Powerplan and Data Setup, StagesFloor planning ppt

Floor planning pptThrinadh Komatipalli

Ěý

Floorplanning involves determining the approximate locations and shapes of modules on an integrated circuit to optimize the design for factors like area, wirelength, and timing. The goals are to partition the design into functional blocks, arrange the blocks, place macros and I/Os, and design the power distribution grid. Floorplanning algorithms use techniques like integer programming, rectangular dual graphs, and hierarchical and simulated annealing approaches to explore the design space and generate optimized floorplans. The outputs include the die area, placement of I/Os and macros, a preliminary power grid design, and definitions of standard cell placement regions.21EC71_Module-2_Routing PPT Electronics and communication engineering module 2

21EC71_Module-2_Routing PPT Electronics and communication engineering module 2yashithkumarbr

Ěý

Electronics and communication engineering module 2 Vlsi design-styles

Vlsi design-stylesPraveen kumar Deverkonda

Ěý

This document discusses various VLSI design styles including programmable logic devices (PLDs), field programmable gate arrays (FPGAs), gate arrays, standard cells, and full-custom design. FPGAs use an array of logic cells connected by routing channels with configurable interconnects implemented using SRAM switches. Gate arrays have a two-step manufacturing process where generic masks are first used to create transistor arrays that are later customized using metal interconnect masks. Standard cell design uses pre-designed and characterized logic cells stored in a library that can be placed in rows with power and ground rails for semi-custom designs. Full-custom design involves creating new mask designs without libraries for the entire chip layout.Ppt seminar noc

Ppt seminar nocmanjyanaikR

Ěý

AĚýnetwork on a chipĚýorĚýnetwork-on-chipĚý(NoCĚý)Ěýis aĚýnetwork-basedĚýcommunications subsystemĚýon anĚýintegrated circuitĚý("microchip"), most typically betweenĚýmodulesĚýin aĚýsystem on a chipĚý(SoC).

The network on chip is aĚýrouter-basedĚýpacket switchingĚýnetwork between SoCĚýmodules.

Networks-on-chip improve theĚýscalabilityĚýof systems-on-chip and theĚýpower efficiencyĚýof complex SoCs compared to other communication subsystem designs.

Used inĚýcomputer graphics,Ěývideo gamingĚýandĚýacceleratingĚýartificial intelligence.

Features:

Network on a chip helps in simplifying the hardware required for routing and switching functions.

Multi-topology and multi-option support is possible for different areas of the network.

Scalability, interoperability and feature development are enhanced when combined with network on a chip.

Power efficiency of complex system-on-chips is improved with network on a chip compared to other designs.

Synchronization issues are handled better than in other designs.

Network on a chip provides higher operating frequencies.

Timing closure is much easier to implement.

Verification of problems is much easier.

SYSTOLIC ARCH IN COMPUTER OPERATING SYSTEM.pptx

SYSTOLIC ARCH IN COMPUTER OPERATING SYSTEM.pptxSaiDhanushM

Ěý

SYSTOLIC ARCH IN COMPUTER OPERATING SYSTEMChip design-styles

Chip design-stylesHARSHALPRAJAPATI10

Ěý

The document discusses several VLSI chip design styles:

- Gate array uses prefabricated logic blocks and routing channels, allowing some customization.

- Standard cell uses rows of identical-height customized logic cells of varying widths. Routing is restricted to horizontal channels.

- Macro cell uses large customized blocks of varying sizes and functional complexity, with flexible placement and routing.

- Full custom allows complete customization of transistor-level design for highest optimization but highest design cost.

- FPGA uses programmable logic blocks and routing resources, allowing design customization by programming block functions and interconnects.Lecture24 clockpower routing

Lecture24 clockpower routingfreeloadtailieu

Ěý

This document discusses routing of clock and power nets in VLSI physical design automation. It describes how clock and power routing have special considerations compared to other signal nets due to factors like clock skew, IR drop, and being major power consumers. It provides details on clock tree routing techniques like H-trees, MMM algorithm, and GMA algorithm to minimize clock skew. It also discusses power grid routing using mesh structures in multiple metal layers to reduce voltage drop and electromigration issues. Non-tree clock routing and combining clock routing with other optimizations are noted as future trends.ASIC Synthesis Optimizations And Settings Part 3

ASIC Synthesis Optimizations And Settings Part 3Amr Adel

Ěý

Part 3 of Logic Synthesis

Topics included:

- ASIC Synthesis

- Standard Cell Libraries.

- Wire Load Model.

- Physical Synthesis

--- Tech File

--- ITF/TLU+ Files

--- LEF File

- Synthesis Settings

--- TNS Optimization

--- Register Duplication and Merging

--- Preferred MUX Implementation

--- Multi-Bit Banking

Physical Design Flow - Standard Cells and Special Cells

Physical Design Flow - Standard Cells and Special CellsJason J Pulikkottil

Ěý

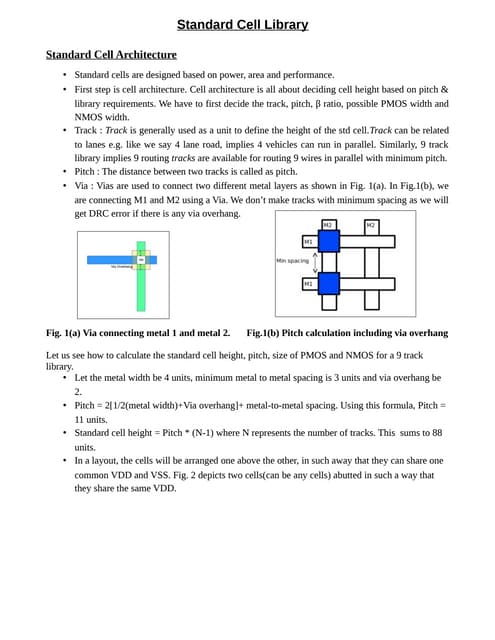

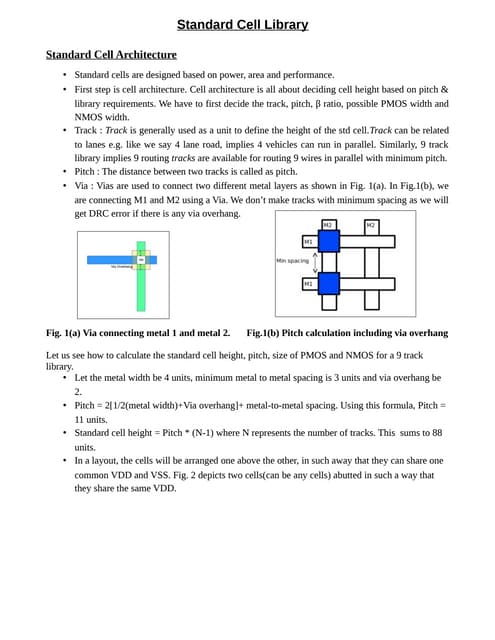

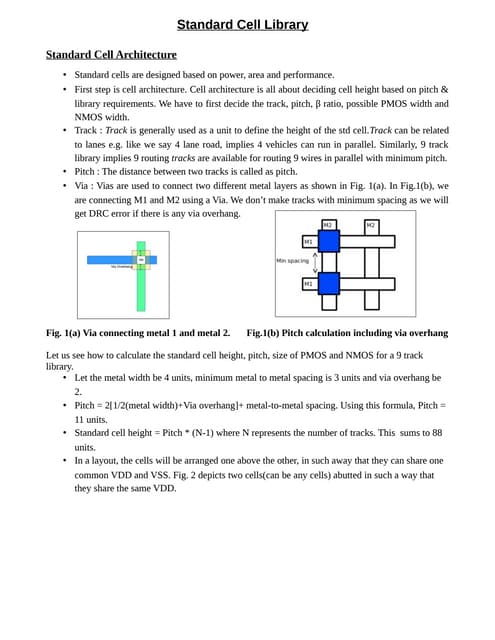

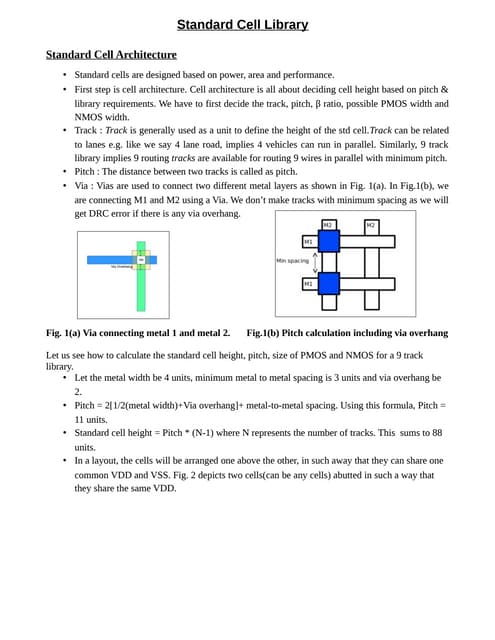

• Standard cells are designed based on power, area and performance.

• First step is cell architecture. Cell architecture is all about deciding cell height based on pitch &

library requirements. We have to first decide the track, pitch, β ratio, possible PMOS width and

NMOS width.

• Track : Track is generally used as a unit to define the height of the std cell.Track can be related

to lanes e.g. like we say 4 lane road, implies 4 vehicles can run in parallel. Similarly, 9 track

library implies 9 routing tracks are available for routing 9 wires in parallel with minimum pitch.

• Pitch : The distance between two tracks is called as pitch.

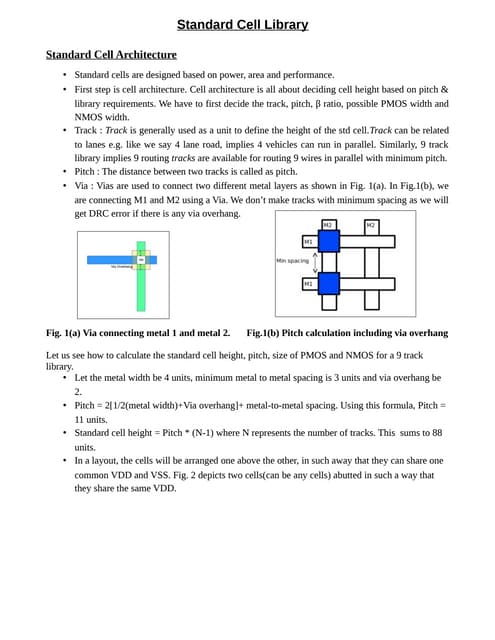

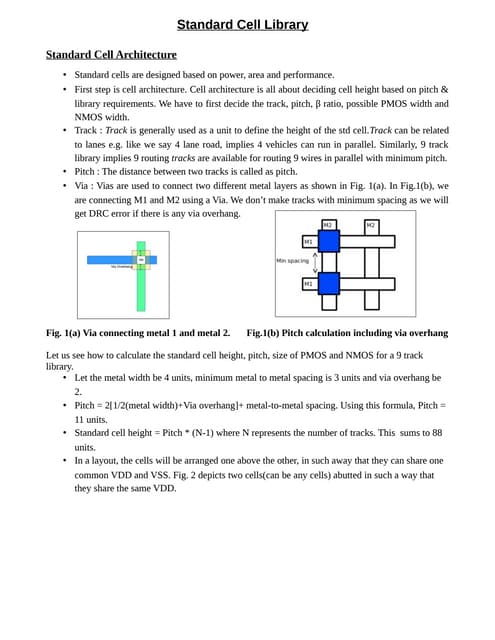

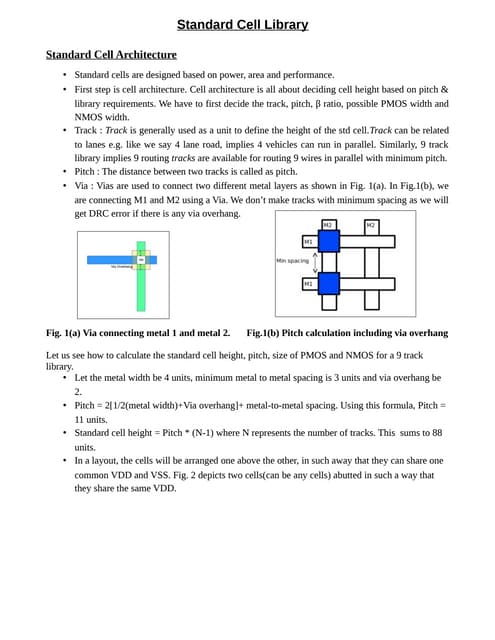

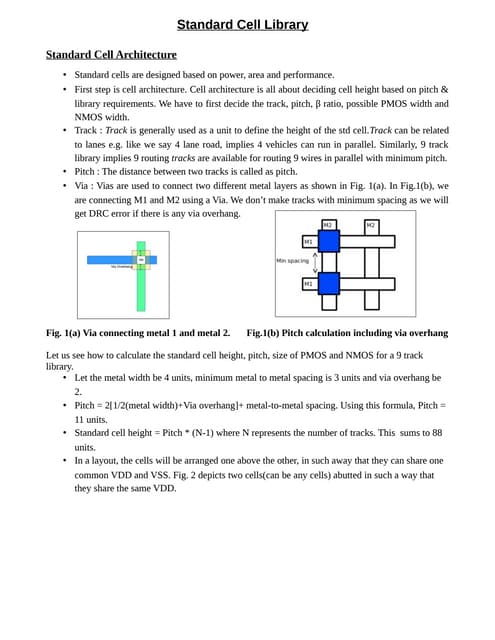

• Via : Vias are used to connect two different metal layers as shown in Fig. 1(a). In Fig.1(b), we

are connecting M1 and M2 using a Via. We don’t make tracks with minimum spacing as we will

get DRC error if there is any via overhang.Implementation strategies for digital ics

Implementation strategies for digital icsaroosa khan

Ěý

The document discusses various digital integrated circuit design implementation strategies. It describes very large scale integration (VLSI) and the VLSI design cycle. It then covers Moore's law, productivity growth rates, and two main design implementation strategies - full custom circuit design and standard cell-based semi-custom design. The document provides details on standard cell libraries, floorplanning, gate arrays, and field programmable gate arrays (FPGAs), and concludes with a comparison of the different design styles.A guide to common automation terms

A guide to common automation termsPratap Chandra

Ěý

This document provides definitions for common automation and PLC terminology. It defines terms from A to N, covering topics like analog and digital signals, input/output modules, communications protocols, programming concepts, and more. The document is an alphabetical guide to help understand common terms used in automation and PLC systems.Physical Design - Import Design Flow Floorplan

Physical Design - Import Design Flow FloorplanJason J Pulikkottil

Ěý

Physical design is process of transforming netlist into layout

which is manufacture-able [GDS]. Physical design process is

often referred as PnR (Place and Route) / APR (Automatic Place

& Route). Main steps in physical design are placement of all

logical cells, clock tree synthesis & routing. During this process

of physical design timing, power, design & technology

constraints have to be met. Further design might require being

optimized w.r.t area, power and performance.Introduction A digital circuit design

Introduction A digital circuit design wafawafa52

Ěý

1. FPGAs implement digital circuits using programmable logic blocks (CLBs) containing lookup tables (LUTs) and flip-flops. LUTs can implement combinational logic functions, while flip-flops allow implementing sequential logic.

2. The CLBs are connected through a programmable switch matrix that can be configured to route signals between LUTs and flip-flops as needed to implement a target circuit design.

3. An example circuit for a seatbelt warning light is mapped to the LUTs and switch matrix of an FPGA, showing how the design can be implemented without requiring a new fabrication run like with an ASIC.es_hardware_handout

es_hardware_handoutMohammad Ranjbar

Ěý

The document discusses hardware evolution, which applies evolutionary techniques to hardware design and synthesis. It is not just implementing evolutionary algorithms in hardware. Hardware evolution can optimize hardware designs, map designs to programmable chips like FPGAs, and even evolve digital circuits directly on reconfigurable hardware. The document provides examples of how evolution can be used to optimize adder circuits, image compression algorithms, and other applications implemented on reconfigurable hardware. It also discusses constraints and evaluation strategies in hardware evolution.Physical Design-Floor Planning Goals And Placement

Physical Design-Floor Planning Goals And PlacementJason J Pulikkottil

Ěý

Goals of Floor Plan:

1. Partition the design into functional blocks

2. Arrange the blocks on a chip

3. Place the Macros

4. Decide the location of the I/O pads

5. Decide the location and number of the power

pads

6. Decide the type of power distributionVHDL_Lec1.pptx

VHDL_Lec1.pptxEmmanuelGift7

Ěý

This document discusses digital systems and their use of discrete signals to represent information. It covers the history of digital systems from early computers using vacuum tubes to today's integrated circuits. The document also describes different types of logic devices including standard logic, custom logic, and programmable logic devices. It provides examples of number systems and conversions between binary, decimal, octal, and hexadecimal numbering systems. Exercises are included for practice converting between these number bases.Vlsi physical design (Back End Process)

Vlsi physical design (Back End Process)CHENCHU CHANDU PRASANTH NADELLA

Ěý

Physical Design Include Floor Planning, Placement,Routing,Power and Clock Distribution Problems in VLSIBack end[1] debdeep![Back end[1] debdeep](https://cdn.slidesharecdn.com/ss_thumbnails/backend1-debdeep-130715130113-phpapp01-thumbnail.jpg?width=560&fit=bounds)

![Back end[1] debdeep](https://cdn.slidesharecdn.com/ss_thumbnails/backend1-debdeep-130715130113-phpapp01-thumbnail.jpg?width=560&fit=bounds)

![Back end[1] debdeep](https://cdn.slidesharecdn.com/ss_thumbnails/backend1-debdeep-130715130113-phpapp01-thumbnail.jpg?width=560&fit=bounds)

![Back end[1] debdeep](https://cdn.slidesharecdn.com/ss_thumbnails/backend1-debdeep-130715130113-phpapp01-thumbnail.jpg?width=560&fit=bounds)

Back end[1] debdeepSandeep Patil

Ěý

The document discusses the backend design flow in VLSI, including floorplanning, placement, and routing. Floorplanning involves estimating block sizes and locations. Placement defines the location of logic cells and interconnect space. Routing connects the placed logic cells, with global routing determining interconnect locations and local routing connecting cells. The document outlines the goals and objectives of EDA tools for floorplanning, placement, and routing. It also discusses clock trees, placement strategies, and concludes with the overall backend flow.How to Make an RFID Door Lock System using Arduino

How to Make an RFID Door Lock System using ArduinoCircuitDigest

Ěý

Learn how to build an RFID-based door lock system using Arduino to enhance security with contactless access control.How to Build a Maze Solving Robot Using Arduino

How to Build a Maze Solving Robot Using ArduinoCircuitDigest

Ěý

Learn how to make an Arduino-powered robot that can navigate mazes on its own using IR sensors and "Hand on the wall" algorithm.

This step-by-step guide will show you how to build your own maze-solving robot using Arduino UNO, three IR sensors, and basic components that you can easily find in your local electronics shop.More Related Content

Similar to 21EC71_Floor Planning _PPT Electronics and communication engineering module 2 (20)

21EC71_Module-2_Routing PPT Electronics and communication engineering module 2

21EC71_Module-2_Routing PPT Electronics and communication engineering module 2yashithkumarbr

Ěý

Electronics and communication engineering module 2 Vlsi design-styles

Vlsi design-stylesPraveen kumar Deverkonda

Ěý

This document discusses various VLSI design styles including programmable logic devices (PLDs), field programmable gate arrays (FPGAs), gate arrays, standard cells, and full-custom design. FPGAs use an array of logic cells connected by routing channels with configurable interconnects implemented using SRAM switches. Gate arrays have a two-step manufacturing process where generic masks are first used to create transistor arrays that are later customized using metal interconnect masks. Standard cell design uses pre-designed and characterized logic cells stored in a library that can be placed in rows with power and ground rails for semi-custom designs. Full-custom design involves creating new mask designs without libraries for the entire chip layout.Ppt seminar noc

Ppt seminar nocmanjyanaikR

Ěý

AĚýnetwork on a chipĚýorĚýnetwork-on-chipĚý(NoCĚý)Ěýis aĚýnetwork-basedĚýcommunications subsystemĚýon anĚýintegrated circuitĚý("microchip"), most typically betweenĚýmodulesĚýin aĚýsystem on a chipĚý(SoC).

The network on chip is aĚýrouter-basedĚýpacket switchingĚýnetwork between SoCĚýmodules.

Networks-on-chip improve theĚýscalabilityĚýof systems-on-chip and theĚýpower efficiencyĚýof complex SoCs compared to other communication subsystem designs.

Used inĚýcomputer graphics,Ěývideo gamingĚýandĚýacceleratingĚýartificial intelligence.

Features:

Network on a chip helps in simplifying the hardware required for routing and switching functions.

Multi-topology and multi-option support is possible for different areas of the network.

Scalability, interoperability and feature development are enhanced when combined with network on a chip.

Power efficiency of complex system-on-chips is improved with network on a chip compared to other designs.

Synchronization issues are handled better than in other designs.

Network on a chip provides higher operating frequencies.

Timing closure is much easier to implement.

Verification of problems is much easier.

SYSTOLIC ARCH IN COMPUTER OPERATING SYSTEM.pptx

SYSTOLIC ARCH IN COMPUTER OPERATING SYSTEM.pptxSaiDhanushM

Ěý

SYSTOLIC ARCH IN COMPUTER OPERATING SYSTEMChip design-styles

Chip design-stylesHARSHALPRAJAPATI10

Ěý

The document discusses several VLSI chip design styles:

- Gate array uses prefabricated logic blocks and routing channels, allowing some customization.

- Standard cell uses rows of identical-height customized logic cells of varying widths. Routing is restricted to horizontal channels.

- Macro cell uses large customized blocks of varying sizes and functional complexity, with flexible placement and routing.

- Full custom allows complete customization of transistor-level design for highest optimization but highest design cost.

- FPGA uses programmable logic blocks and routing resources, allowing design customization by programming block functions and interconnects.Lecture24 clockpower routing

Lecture24 clockpower routingfreeloadtailieu

Ěý

This document discusses routing of clock and power nets in VLSI physical design automation. It describes how clock and power routing have special considerations compared to other signal nets due to factors like clock skew, IR drop, and being major power consumers. It provides details on clock tree routing techniques like H-trees, MMM algorithm, and GMA algorithm to minimize clock skew. It also discusses power grid routing using mesh structures in multiple metal layers to reduce voltage drop and electromigration issues. Non-tree clock routing and combining clock routing with other optimizations are noted as future trends.ASIC Synthesis Optimizations And Settings Part 3

ASIC Synthesis Optimizations And Settings Part 3Amr Adel

Ěý

Part 3 of Logic Synthesis

Topics included:

- ASIC Synthesis

- Standard Cell Libraries.

- Wire Load Model.

- Physical Synthesis

--- Tech File

--- ITF/TLU+ Files

--- LEF File

- Synthesis Settings

--- TNS Optimization

--- Register Duplication and Merging

--- Preferred MUX Implementation

--- Multi-Bit Banking

Physical Design Flow - Standard Cells and Special Cells

Physical Design Flow - Standard Cells and Special CellsJason J Pulikkottil

Ěý

• Standard cells are designed based on power, area and performance.

• First step is cell architecture. Cell architecture is all about deciding cell height based on pitch &

library requirements. We have to first decide the track, pitch, β ratio, possible PMOS width and

NMOS width.

• Track : Track is generally used as a unit to define the height of the std cell.Track can be related

to lanes e.g. like we say 4 lane road, implies 4 vehicles can run in parallel. Similarly, 9 track

library implies 9 routing tracks are available for routing 9 wires in parallel with minimum pitch.

• Pitch : The distance between two tracks is called as pitch.

• Via : Vias are used to connect two different metal layers as shown in Fig. 1(a). In Fig.1(b), we

are connecting M1 and M2 using a Via. We don’t make tracks with minimum spacing as we will

get DRC error if there is any via overhang.Implementation strategies for digital ics

Implementation strategies for digital icsaroosa khan

Ěý

The document discusses various digital integrated circuit design implementation strategies. It describes very large scale integration (VLSI) and the VLSI design cycle. It then covers Moore's law, productivity growth rates, and two main design implementation strategies - full custom circuit design and standard cell-based semi-custom design. The document provides details on standard cell libraries, floorplanning, gate arrays, and field programmable gate arrays (FPGAs), and concludes with a comparison of the different design styles.A guide to common automation terms

A guide to common automation termsPratap Chandra

Ěý

This document provides definitions for common automation and PLC terminology. It defines terms from A to N, covering topics like analog and digital signals, input/output modules, communications protocols, programming concepts, and more. The document is an alphabetical guide to help understand common terms used in automation and PLC systems.Physical Design - Import Design Flow Floorplan

Physical Design - Import Design Flow FloorplanJason J Pulikkottil

Ěý

Physical design is process of transforming netlist into layout

which is manufacture-able [GDS]. Physical design process is

often referred as PnR (Place and Route) / APR (Automatic Place

& Route). Main steps in physical design are placement of all

logical cells, clock tree synthesis & routing. During this process

of physical design timing, power, design & technology

constraints have to be met. Further design might require being

optimized w.r.t area, power and performance.Introduction A digital circuit design

Introduction A digital circuit design wafawafa52

Ěý

1. FPGAs implement digital circuits using programmable logic blocks (CLBs) containing lookup tables (LUTs) and flip-flops. LUTs can implement combinational logic functions, while flip-flops allow implementing sequential logic.

2. The CLBs are connected through a programmable switch matrix that can be configured to route signals between LUTs and flip-flops as needed to implement a target circuit design.

3. An example circuit for a seatbelt warning light is mapped to the LUTs and switch matrix of an FPGA, showing how the design can be implemented without requiring a new fabrication run like with an ASIC.es_hardware_handout

es_hardware_handoutMohammad Ranjbar

Ěý

The document discusses hardware evolution, which applies evolutionary techniques to hardware design and synthesis. It is not just implementing evolutionary algorithms in hardware. Hardware evolution can optimize hardware designs, map designs to programmable chips like FPGAs, and even evolve digital circuits directly on reconfigurable hardware. The document provides examples of how evolution can be used to optimize adder circuits, image compression algorithms, and other applications implemented on reconfigurable hardware. It also discusses constraints and evaluation strategies in hardware evolution.Physical Design-Floor Planning Goals And Placement

Physical Design-Floor Planning Goals And PlacementJason J Pulikkottil

Ěý

Goals of Floor Plan:

1. Partition the design into functional blocks

2. Arrange the blocks on a chip

3. Place the Macros

4. Decide the location of the I/O pads

5. Decide the location and number of the power

pads

6. Decide the type of power distributionVHDL_Lec1.pptx

VHDL_Lec1.pptxEmmanuelGift7

Ěý

This document discusses digital systems and their use of discrete signals to represent information. It covers the history of digital systems from early computers using vacuum tubes to today's integrated circuits. The document also describes different types of logic devices including standard logic, custom logic, and programmable logic devices. It provides examples of number systems and conversions between binary, decimal, octal, and hexadecimal numbering systems. Exercises are included for practice converting between these number bases.Vlsi physical design (Back End Process)

Vlsi physical design (Back End Process)CHENCHU CHANDU PRASANTH NADELLA

Ěý

Physical Design Include Floor Planning, Placement,Routing,Power and Clock Distribution Problems in VLSIBack end[1] debdeep![Back end[1] debdeep](https://cdn.slidesharecdn.com/ss_thumbnails/backend1-debdeep-130715130113-phpapp01-thumbnail.jpg?width=560&fit=bounds)

![Back end[1] debdeep](https://cdn.slidesharecdn.com/ss_thumbnails/backend1-debdeep-130715130113-phpapp01-thumbnail.jpg?width=560&fit=bounds)

![Back end[1] debdeep](https://cdn.slidesharecdn.com/ss_thumbnails/backend1-debdeep-130715130113-phpapp01-thumbnail.jpg?width=560&fit=bounds)

![Back end[1] debdeep](https://cdn.slidesharecdn.com/ss_thumbnails/backend1-debdeep-130715130113-phpapp01-thumbnail.jpg?width=560&fit=bounds)

Back end[1] debdeepSandeep Patil

Ěý

The document discusses the backend design flow in VLSI, including floorplanning, placement, and routing. Floorplanning involves estimating block sizes and locations. Placement defines the location of logic cells and interconnect space. Routing connects the placed logic cells, with global routing determining interconnect locations and local routing connecting cells. The document outlines the goals and objectives of EDA tools for floorplanning, placement, and routing. It also discusses clock trees, placement strategies, and concludes with the overall backend flow.Recently uploaded (20)

How to Make an RFID Door Lock System using Arduino

How to Make an RFID Door Lock System using ArduinoCircuitDigest

Ěý

Learn how to build an RFID-based door lock system using Arduino to enhance security with contactless access control.How to Build a Maze Solving Robot Using Arduino

How to Build a Maze Solving Robot Using ArduinoCircuitDigest

Ěý

Learn how to make an Arduino-powered robot that can navigate mazes on its own using IR sensors and "Hand on the wall" algorithm.

This step-by-step guide will show you how to build your own maze-solving robot using Arduino UNO, three IR sensors, and basic components that you can easily find in your local electronics shop.US Patented ReGenX Generator, ReGen-X Quatum Motor EV Regenerative Accelerati...

US Patented ReGenX Generator, ReGen-X Quatum Motor EV Regenerative Accelerati...Thane Heins NOBEL PRIZE WINNING ENERGY RESEARCHER

Ěý

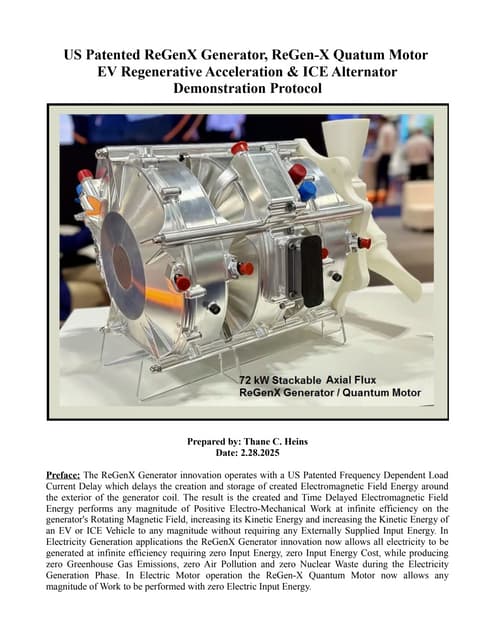

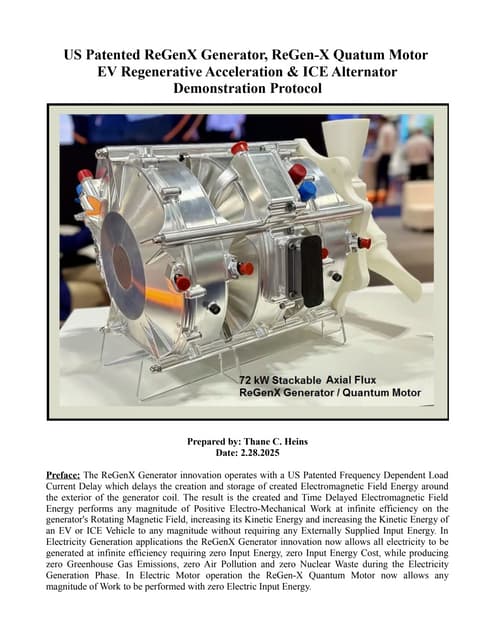

Preface: The ReGenX Generator innovation operates with a US Patented Frequency Dependent Load Current Delay which delays the creation and storage of created Electromagnetic Field Energy around the exterior of the generator coil. The result is the created and Time Delayed Electromagnetic Field Energy performs any magnitude of Positive Electro-Mechanical Work at infinite efficiency on the generator's Rotating Magnetic Field, increasing its Kinetic Energy and increasing the Kinetic Energy of an EV or ICE Vehicle to any magnitude without requiring any Externally Supplied Input Energy. In Electricity Generation applications the ReGenX Generator innovation now allows all electricity to be generated at infinite efficiency requiring zero Input Energy, zero Input Energy Cost, while producing zero Greenhouse Gas Emissions, zero Air Pollution and zero Nuclear Waste during the Electricity Generation Phase. In Electric Motor operation the ReGen-X Quantum Motor now allows any magnitude of Work to be performed with zero Electric Input Energy.

Demonstration Protocol: The demonstration protocol involves three prototypes;

1. Protytpe #1, demonstrates the ReGenX Generator's Load Current Time Delay when compared to the instantaneous Load Current Sine Wave for a Conventional Generator Coil.

2. In the Conventional Faraday Generator operation the created Electromagnetic Field Energy performs Negative Work at infinite efficiency and it reduces the Kinetic Energy of the system.

3. The Magnitude of the Negative Work / System Kinetic Energy Reduction (in Joules) is equal to the Magnitude of the created Electromagnetic Field Energy (also in Joules).

4. When the Conventional Faraday Generator is placed On-Load, Negative Work is performed and the speed of the system decreases according to Lenz's Law of Induction.

5. In order to maintain the System Speed and the Electric Power magnitude to the Loads, additional Input Power must be supplied to the Prime Mover and additional Mechanical Input Power must be supplied to the Generator's Drive Shaft.

6. For example, if 100 Watts of Electric Power is delivered to the Load by the Faraday Generator, an additional >100 Watts of Mechanical Input Power must be supplied to the Generator's Drive Shaft by the Prime Mover.

7. If 1 MW of Electric Power is delivered to the Load by the Faraday Generator, an additional >1 MW Watts of Mechanical Input Power must be supplied to the Generator's Drive Shaft by the Prime Mover.

8. Generally speaking the ratio is 2 Watts of Mechanical Input Power to every 1 Watt of Electric Output Power generated.

9. The increase in Drive Shaft Mechanical Input Power is provided by the Prime Mover and the Input Energy Source which powers the Prime Mover.

10. In the Heins ReGenX Generator operation the created and Time Delayed Electromagnetic Field Energy performs Positive Work at infinite efficiency and it increases the Kinetic Energy of the system.Water Industry Process Automation & Control Monthly - March 2025.pdf

Water Industry Process Automation & Control Monthly - March 2025.pdfWater Industry Process Automation & Control

Ěý

Welcome to the March 2025 issue of WIPAC Monthly the magazine brought to you by the LinkedIn Group WIPAC Monthly.

In this month's edition, on top of the month's news from the water industry we cover subjects from the intelligent use of wastewater networks, the use of machine learning in water quality as well as how, we as an industry, need to develop the skills base in developing areas such as Machine Learning and Artificial Intelligence.

Enjoy the latest editionOptimization of Cumulative Energy, Exergy Consumption and Environmental Life ...

Optimization of Cumulative Energy, Exergy Consumption and Environmental Life ...J. Agricultural Machinery

Ěý

Optimal use of resources, including energy, is one of the most important principles in modern and sustainable agricultural systems. Exergy analysis and life cycle assessment were used to study the efficient use of inputs, energy consumption reduction, and various environmental effects in the corn production system in Lorestan province, Iran. The required data were collected from farmers in Lorestan province using random sampling. The Cobb-Douglas equation and data envelopment analysis were utilized for modeling and optimizing cumulative energy and exergy consumption (CEnC and CExC) and devising strategies to mitigate the environmental impacts of corn production. The Cobb-Douglas equation results revealed that electricity, diesel fuel, and N-fertilizer were the major contributors to CExC in the corn production system. According to the Data Envelopment Analysis (DEA) results, the average efficiency of all farms in terms of CExC was 94.7% in the CCR model and 97.8% in the BCC model. Furthermore, the results indicated that there was excessive consumption of inputs, particularly potassium and phosphate fertilizers. By adopting more suitable methods based on DEA of efficient farmers, it was possible to save 6.47, 10.42, 7.40, 13.32, 31.29, 3.25, and 6.78% in the exergy consumption of diesel fuel, electricity, machinery, chemical fertilizers, biocides, seeds, and irrigation, respectively. Mathematics behind machine learning INT255 INT255__Unit 3__PPT-1.pptx

Mathematics behind machine learning INT255 INT255__Unit 3__PPT-1.pptxppkmurthy2006

Ěý

Mathematics behind machine learning INT255 Integration of Additive Manufacturing (AM) with IoT : A Smart Manufacturing A...

Integration of Additive Manufacturing (AM) with IoT : A Smart Manufacturing A...ASHISHDESAI85

Ěý

Combining 3D printing with Internet of Things (IoT) enables the creation of smart, connected, and customizable objects that can monitor, control, and optimize their performance, potentially revolutionizing various industries. oT-enabled 3D printers can use sensors to monitor the quality of prints during the printing process. If any defects or deviations from the desired specifications are detected, the printer can adjust its parameters in real time to ensure that the final product meets the required standards.Lecture -3 Cold water supply system.pptx

Lecture -3 Cold water supply system.pptxrabiaatif2

Ěý

The presentation on Cold Water Supply explored the fundamental principles of water distribution in buildings. It covered sources of cold water, including municipal supply, wells, and rainwater harvesting. Key components such as storage tanks, pipes, valves, and pumps were discussed for efficient water delivery. Various distribution systems, including direct and indirect supply methods, were analyzed for residential and commercial applications. The presentation emphasized water quality, pressure regulation, and contamination prevention. Common issues like pipe corrosion, leaks, and pressure drops were addressed along with maintenance strategies. Diagrams and case studies illustrated system layouts and best practices for optimal performance.US Patented ReGenX Generator, ReGen-X Quatum Motor EV Regenerative Accelerati...

US Patented ReGenX Generator, ReGen-X Quatum Motor EV Regenerative Accelerati...Thane Heins NOBEL PRIZE WINNING ENERGY RESEARCHER

Ěý

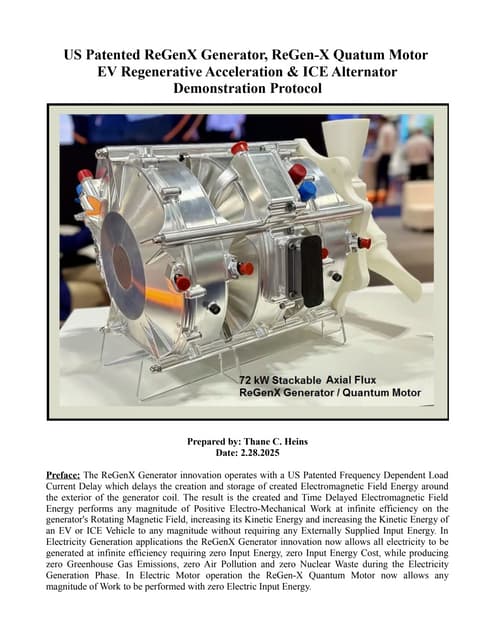

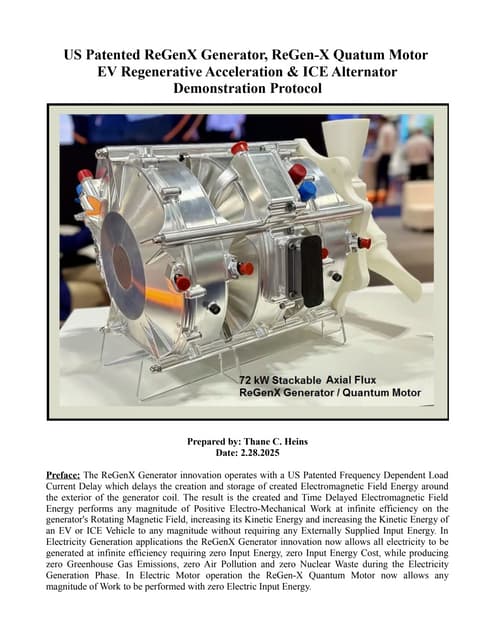

Preface: The ReGenX Generator innovation operates with a US Patented Frequency Dependent Load

Current Delay which delays the creation and storage of created Electromagnetic Field Energy around

the exterior of the generator coil. The result is the created and Time Delayed Electromagnetic Field

Energy performs any magnitude of Positive Electro-Mechanical Work at infinite efficiency on the

generator's Rotating Magnetic Field, increasing its Kinetic Energy and increasing the Kinetic Energy of

an EV or ICE Vehicle to any magnitude without requiring any Externally Supplied Input Energy. In

Electricity Generation applications the ReGenX Generator innovation now allows all electricity to be

generated at infinite efficiency requiring zero Input Energy, zero Input Energy Cost, while producing

zero Greenhouse Gas Emissions, zero Air Pollution and zero Nuclear Waste during the Electricity

Generation Phase. In Electric Motor operation the ReGen-X Quantum Motor now allows any

magnitude of Work to be performed with zero Electric Input Energy.

Demonstration Protocol: The demonstration protocol involves three prototypes;

1. Protytpe #1, demonstrates the ReGenX Generator's Load Current Time Delay when compared

to the instantaneous Load Current Sine Wave for a Conventional Generator Coil.

2. In the Conventional Faraday Generator operation the created Electromagnetic Field Energy

performs Negative Work at infinite efficiency and it reduces the Kinetic Energy of the system.

3. The Magnitude of the Negative Work / System Kinetic Energy Reduction (in Joules) is equal to

the Magnitude of the created Electromagnetic Field Energy (also in Joules).

4. When the Conventional Faraday Generator is placed On-Load, Negative Work is performed and

the speed of the system decreases according to Lenz's Law of Induction.

5. In order to maintain the System Speed and the Electric Power magnitude to the Loads,

additional Input Power must be supplied to the Prime Mover and additional Mechanical Input

Power must be supplied to the Generator's Drive Shaft.

6. For example, if 100 Watts of Electric Power is delivered to the Load by the Faraday Generator,

an additional >100 Watts of Mechanical Input Power must be supplied to the Generator's Drive

Shaft by the Prime Mover.

7. If 1 MW of Electric Power is delivered to the Load by the Faraday Generator, an additional >1

MW Watts of Mechanical Input Power must be supplied to the Generator's Drive Shaft by the

Prime Mover.

8. Generally speaking the ratio is 2 Watts of Mechanical Input Power to every 1 Watt of Electric

Output Power generated.

9. The increase in Drive Shaft Mechanical Input Power is provided by the Prime Mover and the

Input Energy Source which powers the Prime Mover.

10. In the Heins ReGenX Generator operation the created and Time Delayed Electromagnetic Field

Energy performs Positive Work at infinite efficiency and it increases the Kinetic Energy of the

system.

15. Smart Cities Big Data, Civic Hackers, and the Quest for a New Utopia.pdf

15. Smart Cities Big Data, Civic Hackers, and the Quest for a New Utopia.pdfNgocThang9

Ěý

Smart Cities Big Data, Civic Hackers, and the Quest for a New UtopiaEngineering at Lovely Professional University (LPU).pdf

Engineering at Lovely Professional University (LPU).pdfSona

Ěý

LPU’s engineering programs provide students with the skills and knowledge to excel in the rapidly evolving tech industry, ensuring a bright and successful future. With world-class infrastructure, top-tier placements, and global exposure, LPU stands as a premier destination for aspiring engineers.US Patented ReGenX Generator, ReGen-X Quatum Motor EV Regenerative Accelerati...

US Patented ReGenX Generator, ReGen-X Quatum Motor EV Regenerative Accelerati...Thane Heins NOBEL PRIZE WINNING ENERGY RESEARCHER

Ěý

Water Industry Process Automation & Control Monthly - March 2025.pdf

Water Industry Process Automation & Control Monthly - March 2025.pdfWater Industry Process Automation & Control

Ěý

Optimization of Cumulative Energy, Exergy Consumption and Environmental Life ...

Optimization of Cumulative Energy, Exergy Consumption and Environmental Life ...J. Agricultural Machinery

Ěý

US Patented ReGenX Generator, ReGen-X Quatum Motor EV Regenerative Accelerati...

US Patented ReGenX Generator, ReGen-X Quatum Motor EV Regenerative Accelerati...Thane Heins NOBEL PRIZE WINNING ENERGY RESEARCHER

Ěý

21EC71_Floor Planning _PPT Electronics and communication engineering module 2

- 2. Introduction • The input to the floorplanning step - output of system partitioning and design entry—a netlist. • Netlist - describing circuit blocks, the logic cells within the blocks, and their connections.

- 3. • th Te hevit se tr ab rti ingde pcod ne tr of floorplaning and placement steps for routing. •-collection of standard cells with no room set aside ye1t58for

- 4. The starting point of floorplaning and placement steps for the viterbi decoder • Small boxes that look like bricks - outlines of the standard cells. • Largest standard cells, at the bottom of the display (labeled dfctnb) - 188 D flipflops. • '+' symbols -drawing origins of the standard cells—for the D flip- flops they are shifted to the left and below the logic cell bottom left-hand corner. • Large box surrounding all the logic cells - estimated chip size. • (This is a screen shot from Cadence Cell Ensemble.)

- 5. The viterbi decoder after floorplanning and placement

- 6. The viterbi decoder after floorplanning and placement • 8 rows of standard cells separated by 17 horizontal channels (labeled 2–18). • Channels are routed as numbered. • In this example, the I/O pads are omitted to show the cell placement more clearly.

- 7. Floorplanning Goals and Objectives • The input to a floorplanning tool is a hierarchical netlist that describes – the interconnection of the blocks (RAM, ROM, ALU, cache controller, and so on) – the logic cells (NAND, NOR, D flip-flop, and so on) within the blocks – the logic cell connectors (terminals , pins , or ports) • The netlist is a logical description of the ASIC; • The floorplan is a physical description of an ASIC. • Floorplanning is a mapping between the logical description (the netlist) and the physical description (the floorplan). The Goals of Floorplanning are to: • Arrange the blocks on a chip, • Decide the location of the I/O pads, • Decide the location and number of the power pads, • Decide the type of power distribution, and • Decide the location and type of clock distribution. Objectives of Floorplanning – To minimize the chip area To minimize delay. Measuring area is straightforward,

- 8. Measurement of Delay in Floor planning •Floor planning - To predict interconnect delay by estimating interconnect length.

- 9. Measurement of Delay in Floor planning

- 10. Measurement of Delay in Floor planning (contd.,) • A floorplanning tool can use predicted-capacitance tables (also known as interconnect-load tables or wire-load tables ). • Typically between 60 and 70 percent of nets have a FO = 1. • The distribution for a FO = 1 has a very long tail, stretching to interconnects that run from corner to corner of the chip. • The distribution for a FO = 1 often has two peaks, corresponding to a distribution for close neighbors in subgroups within a block, superimposed on a distribution corresponding to routing between subgroups.

- 11. Measurement of Delay in Floor planning (contd.,) • We often see a twin-peaked distribution at the chip level also, corresponding to separate distributions for interblock routing (inside blocks) and intrablock routing (between blocks). • The distributions for FO > 1 are more symmetrical and flatter than for FO = 1. • The wire-load tables can only contain one number, for example the average net capacitance, for any one distribution. • Many tools take a worst-case approach and use the 80- or 90-percentile point instead of the average. Thus a tool may use a predicted capacitance for which we know 90 percent of the nets will have less than the estimated capacitance. 166

- 12. • Repeat the statistical analysis for blocks with different sizes. For example, a net with a FO = 1 in a 25 k-gate block will have a different (larger) average length than if the net were in a 5 k-gate block. • The statistics depend on the shape (aspect ratio) of the block (usually the statistics are only calculated for square blocks). • The statistics will also depend on the type of netlist. For example, the distributions will be different for a netlist generated by setting a constraint for minimum logic delay during synthesis—which tends to generate large numbers of two-input NAND gates—than for netlists generated using minimum-area constraints. Measurement of Delay in Floor planning (contd.,)