1 of 10

Download to read offline

Recommended

Presentazione Progetto CRio

Presentazione Progetto CRioSebastiano Merlino (eTr)

Ěý

Presentazione del progetto per il calcolo della posizione di un utente tramite utilizzo del controllore cRIO.Alcuni dei corsi ISICT

Alcuni dei corsi ISICT Istituto Superiore di Studi in Tecnologie dell'Informazione e della Comunicazione

Ěý

di Matteo Lodi Lesson 1

Lesson 1total

Ěý

This document provides instructions for students on how to use their laptops at school. It outlines three main points:

1) Students must charge their laptop every day after school so it is fully charged for classes. They should write down their login passwords in a safe place like their planner.

2) Teachers will show students how to log into the school network using their username and password. Students should save all work to their network drive in case their laptop breaks.

3) As an assignment, students are asked to create a Word document answering questions about charging their laptop and saving passwords. They should save this to a folder on their network drive.Lesson2

Lesson2total

Ěý

The document provides instructions for using Studywiz, an online learning platform. It explains how to log in, access personal folders like the e-locker for file storage, and find lesson resources. It details uploading homework assignments to the e-locker for teachers to review. For homework, students must create a guide to Studywiz for peers to explain how to use the program.

Podcasting_Educational _Essentials - Vol_1Andreas Auwärter

Ěý

How to recieve Podcasts - Additional şÝşÝߣs to the Screencast3D-DRESD ASIDA

3D-DRESD ASIDAMarco Santambrogio

Ěý

The document discusses audio signal improvement techniques for a D740 architecture, including:

1. Spectral subtraction is proposed to remove background noise from audio signals.

2. A simple microphone preamplifier design is presented that provides amplification but has limitations in distortion performance and power consumption.

3. Future work is proposed combining spectral subtraction with direction of arrival techniques using a microphone array to further improve noise reduction.

More Related Content

What's hot (17)

Presentazione Progetto CRio

Presentazione Progetto CRioSebastiano Merlino (eTr)

Ěý

Presentazione del progetto per il calcolo della posizione di un utente tramite utilizzo del controllore cRIO.Alcuni dei corsi ISICT

Alcuni dei corsi ISICT Istituto Superiore di Studi in Tecnologie dell'Informazione e della Comunicazione

Ěý

di Matteo Lodi Alcuni dei corsi ISICT

Alcuni dei corsi ISICT Istituto Superiore di Studi in Tecnologie dell'Informazione e della Comunicazione

Ěý

Viewers also liked (7)

Lesson 1

Lesson 1total

Ěý

This document provides instructions for students on how to use their laptops at school. It outlines three main points:

1) Students must charge their laptop every day after school so it is fully charged for classes. They should write down their login passwords in a safe place like their planner.

2) Teachers will show students how to log into the school network using their username and password. Students should save all work to their network drive in case their laptop breaks.

3) As an assignment, students are asked to create a Word document answering questions about charging their laptop and saving passwords. They should save this to a folder on their network drive.Lesson2

Lesson2total

Ěý

The document provides instructions for using Studywiz, an online learning platform. It explains how to log in, access personal folders like the e-locker for file storage, and find lesson resources. It details uploading homework assignments to the e-locker for teachers to review. For homework, students must create a guide to Studywiz for peers to explain how to use the program.

Podcasting_Educational _Essentials - Vol_1Andreas Auwärter

Ěý

How to recieve Podcasts - Additional şÝşÝߣs to the Screencast3D-DRESD ASIDA

3D-DRESD ASIDAMarco Santambrogio

Ěý

The document discusses audio signal improvement techniques for a D740 architecture, including:

1. Spectral subtraction is proposed to remove background noise from audio signals.

2. A simple microphone preamplifier design is presented that provides amplification but has limitations in distortion performance and power consumption.

3. Future work is proposed combining spectral subtraction with direction of arrival techniques using a microphone array to further improve noise reduction.

3D-DRESD AC

3D-DRESD ACMarco Santambrogio

Ěý

This document proposes a novel system-on-chip (SoC) design methodology that combines adaptive software and reconfigurable hardware. It aims to reduce the performance gap between hardware and software. The methodology characterizes tasks based on their relationship to hardware and software. It uses adaptive computing techniques and reconfiguration to move software tasks to hardware when beneficial. This improves overall system throughput by exploiting the self-adjusting properties of adaptive computing. The methodology is demonstrated on a case study of edge detection in digital images, showing adaptive computing on software is faster than hardware after initial setup.Project

Projectweihsun

Ěý

Coccidiosis is an intestinal infection caused by protozoan parasites of the genus Isospora. Isospora felis commonly infects cats, especially kittens. The life cycle involves the ingestion of sporulated oocysts, which release sporozoites that infect intestinal cells. This causes cell death and leads to symptoms like diarrhea. Most cats will be infected with coccidia at some point. While symptoms are usually mild, kittens and immunocompromised cats can experience more severe disease.

Similar to 3D-DRESD DRC (20)

Open Source Parallel Computing ltcsp

Open Source Parallel Computing ltcspLaura Camellini

Ěý

Old graduation work by an engineer for engineering sans frontier BolognaHigh Level Synthesis Using Esterel

High Level Synthesis Using EsterelAlberto Minetti

Ěý

Very little workshop on HLS:

Mention of Synthesizing hardware using high level language, in particular C-like languages. Analysis of existent old language since 1980 to 2000: Cones, HardwareC, Transmogrifier C, SystemC, C2Verilog, Handel-C. Open problems using C-like languages (taken from Stephen Edwards' "The challenges of synthesizing Hardware from C-like languages").

Hardware design and synthesis using Esterel, reactive and synchronous language, ideal to describe a *behavioural* structure of hardware concurrent real-time controller and to test formal correctness. Easiness in creation of VHDL, Verilog, SystemC, Finite State Automata, dataflow design, and implementation on ASIC or FPGA or RePIC (processor architecture supporting direct esterel execution).

Example of a Preudo-Random Bit Sequence using Esterel versus the implementation using OrCAD softwareHa solutions su power i

Ha solutions su power iPRAGMA PROGETTI

Ěý

Presentazione della soluzione di High Availability e Disaster Recovery su Power System - evento 28 settembre Spazio La Stampa TorinoSucco di lampone: come ottimizzare JAVA e PHP su un'architettura Raspberry Pi...

Succo di lampone: come ottimizzare JAVA e PHP su un'architettura Raspberry Pi...Codemotion

Ěý

şÝşÝߣs from Matteo Beccan talk @ codemotion roma 2014Codemotion 2014 : ottimizzare JAVA e PHP su un’architettura Raspberry Pi Cluster

Codemotion 2014 : ottimizzare JAVA e PHP su un’architettura Raspberry Pi ClusterMatteo Baccan

Ěý

Succo di lampone: come ottimizzare JAVA e PHP su

un’architettura Raspberry Pi ClusterSummary of “The Case for Writing Network Drivers in High-Level Programming La...

Summary of “The Case for Writing Network Drivers in High-Level Programming La...LeonardoIurada

Ěý

Summary of “The Case for Writing Network Drivers in High-Level Programming Languages"A short introduction about traffic shaping and K-Shaper tool --- speech at Ha...

A short introduction about traffic shaping and K-Shaper tool --- speech at Ha...Massimiliano Leone

Ěý

A short introduction about linux and iptables architecture as well as traffic shaping engines in this environment, and related issues.

A solution is provided by k-shaper, and these slides show a mini how-to.

This is part of my academic training, and it was introduced at HackMeeting in Naples, in 2005.

K-Shaper code is available at: https://github.com/k0smik0/k-shaperMay 2010 - Infinispan

May 2010 - InfinispanJBug Italy

Ěý

Infinispan - Sanne Grinovero

29/05/2010 - Jug Sardegna - JBoss User Group Roma Glusterfs: un filesystem altamente versatile

Glusterfs: un filesystem altamente versatileIvan Rossi

Ěý

Una presentazione introduttiva su Glusterfs, presentata al LinuxDay 2013 organizzato dal FerraraLUG

Glusterfs: un filesystem altamente versatile

Glusterfs: un filesystem altamente versatileBioDec

Ěý

Presentazione introduttiva a GlusterFS fatta al LinuxDay 2013 a FerraraRedis Cluster by S. Sanfilippo

Redis Cluster by S. SanfilippoCorley S.r.l.

Ěý

şÝşÝߣs of speech by Salvatore Sanfilippo at Cloud Conference 2014A short introduction about traffic shaping and K-Shaper tool --- speech at Ha...

A short introduction about traffic shaping and K-Shaper tool --- speech at Ha...Massimiliano Leone

Ěý

More from Marco Santambrogio (20)

RCIM 2008 - - hArtes Atmel

RCIM 2008 - - hArtes AtmelMarco Santambrogio

Ěý

1. The document discusses Diopsis940, a microcontroller product from Atmel that features an ARM9 processor and floating point DSP for consumer applications.

2. It provides details on target applications including hands-free phones, high-end car audio, and sound processors. The microcontroller supports complex audio processing algorithms.

3. hArtes, an Atmel division, aims to reduce application development time through tools that streamline the process from conceptual design to implementation using their microcontroller products.RCIM 2008 - - UniCal

RCIM 2008 - - UniCalMarco Santambrogio

Ěý

The document proposes a coarse-grain reconfigurable array (CGRA) for accelerating digital signal processing. The CGRA aims to provide an intermediate tradeoff between flexibility and performance compared to FPGAs and ASICs. It consists of an array of processing elements and distributed memory interconnected via programmable switches. Evaluation shows the CGRA achieves 4.8-8X speedup, 24-58% improved energy efficiency, and up to 40% reduced area compared to a Xilinx Virtex-4 FPGA for applications like color space conversion, FIR filtering, and DCT.RCIM 2008 - - ALTERA

RCIM 2008 - - ALTERAMarco Santambrogio

Ěý

This document discusses Altera's FPGA strategy for reconfigurable hardware in industry applications. It defines reconfigurable hardware as an architecture that does not require on-the-fly timing analysis because product qualification is extensively done through temperature and cycle testing without hardware architecture changes. It then shows how programmable solutions have evolved from single CPU and DSP cores to multi-core processors and coarse-grained arrays with FPGAs moving to fine-grained, massively parallel arrays with embedded hard IP blocks. Future trends include challenges of scaling CPUs due to physical limits and the benefits of parallelism through hardware reconfiguration.DHow2 - L6 VHDL

DHow2 - L6 VHDLMarco Santambrogio

Ěý

The document describes processes in VHDL. It defines a process as a concurrent statement that contains sequential logic. Processes run in parallel and can be conditioned by a sensitivity list or wait statement. Local variables retain their values between executions. It provides an example of a process with a sensitivity list and one with a wait statement. It also summarizes the general structure of a VHDL program and describes different types of process control including if-then-else, case statements, and decoders. Additional topics covered include flip-flops, counters, and finite state machines.RCIM 2008 - - ALaRI

RCIM 2008 - - ALaRIMarco Santambrogio

Ěý

The document discusses requirements for enabling self-adaptivity at both the software and hardware levels. It proposes a layered model with controllers at the application, run-time environment, and hardware levels. A component-based approach is suggested to allow adaptations such as replacing or modifying components. Simulation results demonstrate how controllers at each level can coordinate to meet goals like high throughput while minimizing power usage. Reconfigurable computing platforms need to allow hardware components to be instantiated and interconnected to enable self-adaptation across software and hardware.RCIM 2008 - Modello Scheduling

RCIM 2008 - Modello SchedulingMarco Santambrogio

Ěý

The document summarizes research on task scheduling techniques for dynamically reconfigurable systems. It presents (1) an integer linear programming model to formally define the scheduling problem, (2) the Napoleon heuristic scheduler to solve the problem in reasonable time based on the ILP model, and (3) experimental results validating that Napoleon obtains an average 18.6% better schedule length than other algorithms. Future work is outlined to integrate Napoleon into a general design framework and scheduling-aware partitioning flow.RCIM 2008 - HLR

RCIM 2008 - HLRMarco Santambrogio

Ěý

The document summarizes key topics in reconfigurable computing, including motivations for reconfigurable systems, types of flexibility they provide, and challenges in reconfiguration. It discusses design flows to reduce complexity, maximizing reuse of reconfigurable modules to reduce latency, hiding reconfiguration times, and using relocation to further optimize schedules. Areas of reconfiguration and possible implementation scenarios involving relocation are illustrated.RCIM 2008 - Modello Generale

RCIM 2008 - Modello GeneraleMarco Santambrogio

Ěý

The document discusses an approach for identifying cores for reconfigurable systems driven by specification self-similarity. It involves partitioning a specification graph into subsets of operations that can be mapped to reusable configurable modules. The approach identifies recurrent subgraphs in the specification that are good candidates for these cores. It works in two phases: first identifying isomorphic subgraph templates, and then selecting templates for implementation as reconfigurable modules based on metrics like largest size, most frequent usage, or minimizing communication. Experimental results on encryption benchmarks show the approach can cover a large portion of the specification with a small set of identified templates.RCIM 2008 - Allocation Relocation

RCIM 2008 - Allocation RelocationMarco Santambrogio

Ěý

This document summarizes techniques for core allocation and relocation management in self-dynamically reconfigurable architectures. It introduces basic concepts like cores, IP cores, and reconfigurable regions. It then describes proposed 1D and 2D relocation solutions like BiRF and BiRF Square that allow runtime relocation with low overhead. A core allocation manager is introduced to choose core placements optimizing criteria like rejection rate and completion time with low management costs. Evaluation shows the techniques improve metrics like rejection rate and routing costs compared to other approaches.RCIM 2008 - - hArtes_Ferrara

RCIM 2008 - - hArtes_FerraraMarco Santambrogio

Ěý

The document discusses an hardware application platform developed for the hArtes project. It provides heterogeneous computing resources like DSPs, CPUs and FPGAs. Demonstrator applications focus on advanced audio processing for car infotainment and teleconferencing. The platform supports these applications by integrating different components, scaling computational power, and accommodating future additions. It also provides adequate I/O channels for audio signal processing.RCIM 2008 - Janus

RCIM 2008 - JanusMarco Santambrogio

Ěý

The document describes the Janus system, an FPGA-based approach for simulating spin glass systems using Monte Carlo algorithms. The key aspects are:

1) Spin glass systems are computationally challenging to simulate due to the huge number of possible configurations.

2) The Janus system uses FPGAs to implement a large number of parallel update engines that can flip spins and accept/reject changes according to a Metropolis algorithm.

3) Each FPGA processor grid contains 4x4 processors that can communicate with neighbors. This allows simulations to be massively parallelized across the FPGA network.RCIM 2008 - Intro

RCIM 2008 - IntroMarco Santambrogio

Ěý

The document outlines the agenda for the Reconfigurable Computing Italian Meeting held on December 19, 2008 at Politecnico di Milano in Milan, Italy. The agenda included four sessions on trends in reconfigurable computing, the hArtes European project, applicative scenarios, and the High Level Reconfiguration project. Each session included 3-4 presentations on technical topics within the session theme, such as FPGA strategies, multi-core signal processing, evolvable hardware, and runtime core relocation management. The meeting concluded with wishes for a merry Christmas and a happy new year.RCW@DEI - ADL

RCW@DEI - ADLMarco Santambrogio

Ěý

This document provides an overview of architectural description languages (ADLs). It discusses that ADLs capture the structure and behavior of processor architectures to enable high-level modeling, analysis, and automatic prototype generation. ADLs can be classified as structural, behavioral, or mixed. Structural ADLs focus on low-level hardware details while behavioral ADLs model instruction sets for compiler generation. The document outlines different ADL types and their applications.RCW@DEI - Design Flow 4 SoPc

RCW@DEI - Design Flow 4 SoPcMarco Santambrogio

Ěý

The document discusses design flows for partially reconfigurable systems on FPGAs. It provides an overview of Xilinx FPGA technology and configuration memory organization. It then summarizes several of Xilinx's design flows for partial reconfiguration (difference-based, module-based, EAPR). It outlines challenges with existing design flows and introduces the DRESD methodology and tools (INCA, Caronte) which aim to address these challenges by providing a more comprehensive framework for implementing dynamic reconfigurable embedded systems.3D-DRESD DRC

- 1. DRC DRESD Reconfiguration Controller

- 2. Sommario ICAP ICAP DRESD OPB HWICAP Problemi e Limiti Soluzione Proposta - DRC Occupazione Area Analisi Temporale Conclusioni e Sviluppi Futuri

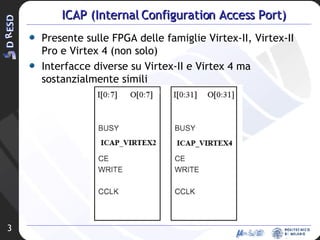

- 3. ICAP (Internal Configuration Access Port) Presente sulle FPGA delle famiglie Virtex-II, Virtex-II Pro e Virtex 4 (non solo) Interfacce diverse su Virtex-II e Virtex 4 ma sostanzialmente simili

- 4. ICAP DRESD Controller di riconfigurabilità verso porta ICAP sviluppato all’interno del gruppo D.R.E.S.D. Interfaccia su PLB con funzionamento a 8 bit Nessuna presenza di cache Driver Semplici da usare

- 5. OPB HWICAP Controllo sviluppato da Xilinx Interfacciato su OPB con funzionamento a 32 bit Presenza di una cache fissa che utilizza le BRAM della FPGA Driver non di facile utilizzo

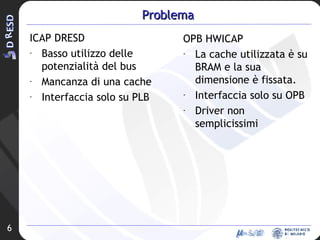

- 6. Problema ICAP DRESD Basso utilizzo delle potenzialità del bus Mancanza di una cache Interfaccia solo su PLB OPB HWICAP La cache utilizzata è su BRAM e la sua dimensione è fissata. Interfaccia solo su OPB Driver non semplicissimi

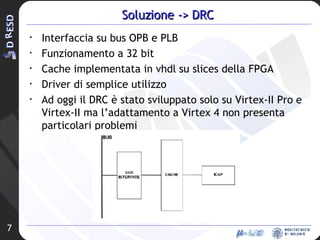

- 7. Soluzione -> DRC Interfaccia su bus OPB e PLB Funzionamento a 32 bit Cache implementata in vhdl su slices della FPGA Driver di semplice utilizzo Ad oggi il DRC è stato sviluppato solo su Virtex-II Pro e Virtex-II ma l’adattamento a Virtex 4 non presenta particolari problemi

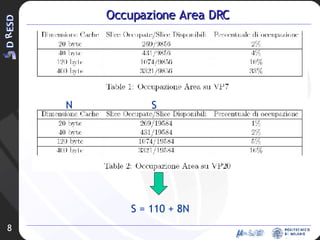

- 8. Occupazione Area DRC S = 110 + 8N S N

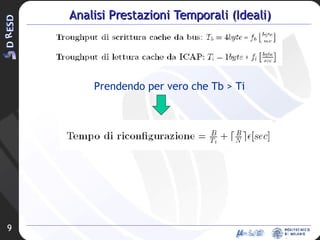

- 9. Analisi Prestazioni Temporali (Ideali) Prendendo per vero che Tb > Ti

- 10. Conclusioni e Sviluppi Futuri Il DRC si pone come controllore di riconfigurabilità definitivo ma presenta dei limiti: La premessa sul throughput fatta in precedenza non è rispettata in realtà L’occupazione di area non ha tenuto conto di tutte quelle slices libere ma non utilizzabili in quanto non raggiungibili Tutti i controller presentati sono Slave su Bus Possibile introduzione di un meccanismo DMA con canale diretto verso le memorie dove si trovano i Bitstreams