assembler_full_slides.ppt

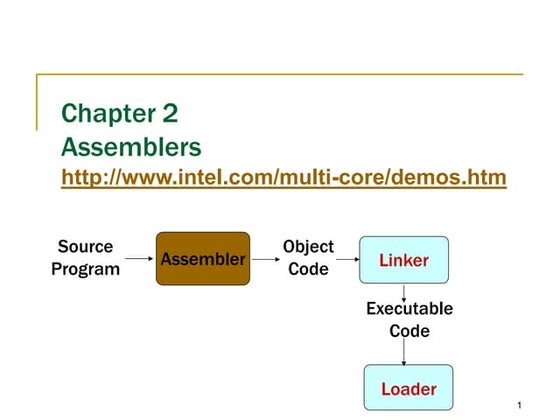

- 2. ASSEMBLERS

- 3. OUTLINE ï 2.1 Basic Assembler Functions âĶ A simple SIC assembler âĶ Assembler tables and logic ï 2.2 Machine-Dependent Assembler Features âĶ Instruction formats and addressing modes âĶ Program relocation ï 2.3 Machine-Independent Assembler Features ï 2.4 Assembler Design Options âĶ Two-pass âĶ One-pass âĶ Multi-pass

- 4. 2.1 BASIC ASSEMBLER FUNCTIONS ï Figure 2.1 shows an assembler language program for SIC. âĶ The line numbers are for reference only. âĶ Indexing addressing is indicated by adding the modifier â,Xâ âĶ Lines beginning with â.âcontain comments only. âĶ Reads records from input device (code F1) âĶ Copies them to output device (code 05) âĶ At the end of the file, writes EOF on the output device, then RSUB to the operating system

- 8. 2.1 BASIC ASSEMBLER FUNCTIONS ï Assembler directives (pseudo- instructions) âĶ START, END, BYTE, WORD, RESB, RESW. âĶ These statements are not translated into machine instructions. âĶ Instead, they provide instructions to the assembler itself.

- 9. 2.1 BASIC ASSEMBLER FUNCTIONS ï Data transfer (RD, WD) âĶ A buffer is used to store record âĶ Buffering is necessary for different I/O rates âĶ The end of each record is marked with a null character (0016) âĶ Buffer length is 4096 Bytes âĶ The end of the file is indicated by a zero-length record âĶ When the end of file is detected, the program writes EOF on the output device and terminates by RSUB. ï Subroutines (JSUB, RSUB) âĶ RDREC, WRREC âĶ Save link (L) register first before nested jump

- 10. 2.1.1 A SIMPLE SIC ASSEMBLER ï Figure 2.2 shows the generated object code for each statement. âĶ Loc gives the machine address in Hex. âĶ Assume the program starting at address 1000. ï Translation functions âĶ Translate STL to 14. âĶ Translate RETADR to 1033. âĶ Build the machine instructions in the proper format (,X). âĶ Translate EOF to 454F46. âĶ Write the object program and assembly listing

- 12. Forward reference problem ïŪ Reference to a label that is defined later in the program.

- 13. ï A forward reference âĶ In line number10 1000 FIRST STL RETADR 141033 âĶ A reference to a label (RETADR) that is defined later in the program âĶ Most assemblers make two passes over the source program ï Most assemblers make two passes over source program. âĶ Pass 1 scans the source for label definitions and assigns address (Loc). âĶ Pass 2 performs most of the actual translation.

- 14. ï Assemblerâs Functions âĶ Convert mnemonic operation codes to their machine language equivalents ï STL to 14 âĶ Convert symbolic operands (referred label) to their equivalent machine addresses ï RETADR to 1033 âĶ Build the machine instructions in the proper format âĶ Convert the data constants to internal machine representations âĶ Write the object program and the assembly listing

- 15. The functions of the two passes assembler. ï Pass 1 (define symbol) âĶ Assign addresses to all statements (generate LOC). âĶ Check the correctness of Instruction (check with OP table). âĶ Save the values (address) assigned to all labels into SYMBOL table for Pass 2. âĶ Perform some processing of assembler directives. ï Pass 2 âĶ Assemble instructions (op code from OP table, address from SYMBOL table). âĶ Generate data values defined by BYTE, WORD. âĶ Perform processing of assembler directives not done during Pass 1. âĶ Write the OP (Fig. 2.3) and the assembly listing (Fig. 2.2).

- 16. 2.1.2 DATA STRUCTURES in ASSEMBLER ï Our simple assembler uses two internal tables: The OPTAB and SYMTAB. âĶ OPTAB is used to look up mnemonic operation codes and translate them to their machine language equivalents. ï LDAâ00, STLâ14, âĶ âĶ SYMTAB is used to store values (addresses) assigned to labels. ï COPYâ1000, FIRSTâ1000 âĶ ï Location Counter LOCCTR âĶ LOCCTR is a variable for assignment addresses. âĶ LOCCTR is initialized to address specified in START. âĶ When reach a label, the current value of LOCCTR gives the address to be associated with that label.

- 17. 2.1.2 ASSEMBLER TABLES AND LOGIC ï The Operation Code Table (OPTAB) âĶ Contain the mnemonic operation & its machine language equivalents (at least). âĶ Contain instruction format& length. âĶ Pass 1, OPTAB is used to look up and validate operation codes. âĶ Pass 2, OPTAB is used to translate the operation codes to machine language. âĶ In SIC/XE, assembler search OPTAB in Pass 1 to find the instruction length for incrementing LOCCTR. âĶ Organize as a hash table (static table).

- 18. 2.1.2 ASSEMBLER TABLES AND LOGIC ï The Symbol Table (SYMTAB) âĶ Include the name and value (address) for each label. âĶ Include flags to indicate error conditions âĶ Contain type, length. âĶ Pass 1, labels are entered into SYMTAB, along with assigned addresses (from LOCCTR). âĶ Pass 2, symbols used as operands are look up in SYMTAB to obtain the addresses. âĶ Organize as a hash table (static table). âĶ The entries are rarely deleted from table.

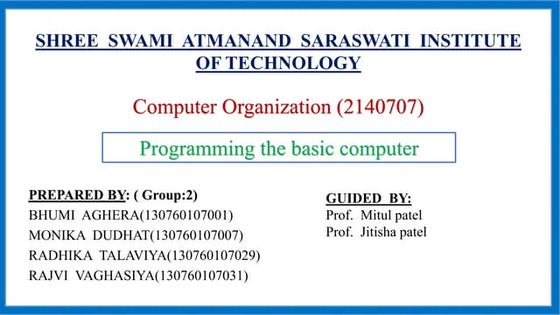

- 19. 2.1.2 ASSEMBLER TABLES AND LOGIC ï Pass 1 usually writes an intermediate file. âĶ Contain source statement together with its assigned address, error indicators. âĶ This file is used as input to Pass 2. ï Figure 2.4 shows the two passes of assembler. âĶ Format with fields LABEL, OPCODE, and OPERAND. âĶ Denote numeric value with the prefix#. #[OPERAND]

- 20. Pass 1

- 22. Pass 2

- 24. 2.2 MACHINE-DEPENDENT ASSEMBLER FEATURES ï Indirect addressing âĶ Adding the prefix @ to operand (line 70). ï Immediate operands âĶ Adding the prefix # to operand (lines 12, 25, 55, 133). ï Extended format âĶ Adding the prefix + to OP code (lines 15, 35, 65). ï The use of register-register instructions. âĶ Faster and donât require another memory reference.

- 27. Figure 2.5: WRREC Figure 2.5: Example of SIC/XE Program

- 28. 2.2 MACHINE-DEPENDENT ASSEMBLER FEATURES ï SIC/XE âĶ PC-relative/Base-relative addressing op m âĶ Indirect addressing op @m âĶ Immediate addressing op #c âĶ Extended format +op m âĶ Index addressing op m, X âĶ register-to-register instructions COMPR âĶ larger memory âmulti-programming (program allocation)

- 29. 2.2 MACHINE-DEPENDENT ASSEMBLER FEATURES ï Register translation âĶ register name (A, X, L, B, S, T, F, PC, SW) and their values (0, 1, 2, 3, 4, 5, 6, 8, 9) âĶ preloaded in SYMTAB ï Address translation âĶ Most register-memory instructions use program counter relative or base relative addressing âĶ Format 3: 12-bit disp (address) field ï PC-relative: -2048~2047 ï Base-relative: 0~4095 âĶ Format 4: 20-bit address field (absolute addressing)

- 30. 2.2.1 INSTRUCTION FORMATS & ADDRESSING MODES ï The START statement âĶ Specifies a beginning address of 0. ï Register-register instructions âĶ CLEAR & TIXR, COMPR ï Register-memory instructions are using âĶ Program-counter (PC) relative addressing âĶ The program counter is advanced after each instruction is fetched and before it is executed. âĶ PC will contain the address of the next instruction. 10 0000 FIRST STL RETADR 17202D TA -(PC) = disp= 30H â3H= 2D

- 33. Figure 2.6 Program from fig 2.5 with object code

- 35. 2.2.1 INSTRUCTION FORMATS & ADDRESSING MODES 40 0017 J CLOOP 3F2FEC 0006 - 001A= disp= -14 ï Base (B), LDB #LENGTH, BASE LENGTH 160 104E STCH BUFFER, X 57C003 TA-(B) = 0036 -(B) = disp= 0036-0033 = 0003 ï Extended instruction 15 0006 CLOOP +JSUB RDREC 4B101036 ï Immediate instruction 55 0020 LDA #3 010003 133 103C +LDT #4096 75101000 ï PC relative + indirect addressing (line 70)

- 36. 2.2.2 Program Relocation ï Absolute program, relocatable program

- 37. 2.2.2 PROGRAM RELOCATION ï Note that no matter where the program is loaded, RDREC is always is 1036 bytes past the starting address of the program. This means that we can solve the relocation problem in the following way, 1. When the assembler generates the object code for the JSUB instruction we are considering it will insert the address of RDREC relative to the start of the program. This is the reason we initialized the location counter to 0 for the assembly 2. The assembler will also produce the command for the loader, instructing it to add the beginning address of the program to address the field in the JSUB instruction at the load time.

- 38. 2.2.2 PROGRAM RELOCATION ï Modification record (direct addressing) âĶ 1 M âĶ 2-7 Starting location of the address field to be modified, relative to the beginning of the program. âĶ 8-9 Length of the address field to be modified, in half bytes. M^000007^05

- 39. 2.3 MACHINE-INDEPENDENT ASSEMBLER FEATURES ï Write the value of a constant operand as a part of the instruction that uses it (Fig. 2.9). ï A literal is identified with the prefix = 45 001AENDFIL LDA=CâEOFâ 032010 âĶ Specifies a 3-byte operand whose value is the character string EOF. 215 1062 WLOOP TD =Xâ05â E32011 âĶ Specifies a 1-byte literal with the hexadecimal value 05

- 41. RDREC

- 42. WRRE C Figure 2.9 Program demonstrating additional assembler features

- 43. 2.3.1 LITERALS ï The difference between literal operands and immediate operands âĶ =, # âĶ Immediate addressing, the operand value is assembled as part of the machine instruction, no memory reference. âĶ With a literal, the assembler generates the specified value as a constant at some other memory location. The address of this generated constant is used as the TA for the machine instruction, using PC-relative or base-relative addressing with memory reference. ï Literal pools âĶ At the end of the program (Fig. 2.10). âĶ Assembler directive LTORG, it creates a literal pool that contains all of the literal operands used since the previous LTORG.

- 45. RDREC

- 46. WRRE C Figure 2.10 Program from figure 2.9 with object code

- 47. 2.3.1 Literals ï When to use LTORG âĶ The literal operand would be placed too far away from the instruction referencing. âĶ Cannot use PC-relative addressing or Base- relative addressing to generate Object Program. ï Most assemblers recognize duplicate literals. âĶ By comparison of the character strings defining them. âĶ =CâEOFâ and =Xâ454F46â

- 48. 2.3.1 LITERALS ï Allow literals that refer to the current value of the location counter. âĶ Such literals are sometimes useful for loading base registers. LDB =* ; register B=beginning address of statement=current LOCBASE* ; for base relative addressing ï If a literal =*appeared on line 13 or 55 âĶ Specify an operand with value 0003 (Loc) or 0020 (Loc).

- 49. 2.3.1 LITERALS ï Literal table (LITTAB) âĶ Contains the literal name (=CâEOFâ), the operand value (454F46) and length (3), and the address (002D). âĶ Organized as a hash table. âĶ Pass 1, the assembler creates or searches LITTAB for the specified literal name. âĶ Pass 1 encounters a LTORG statement or the end of the program, the assembler makes a scan of the literal table. âĶ Pass 2, the operand address for use in generating OC is obtained by searching LITTAB.

- 50. 2.3.2 SYMBOL-DEFINING STATEMENTS ï Allow the programmer to define symbols and specify their values. âĶ Assembler directive EQU. âĶ Improved readability in place of numeric values. +LDT #4096 MAXLEN EQU BUFEND-BUFFER (4096) +LDT #MAXLEN ï Use EQU in defining mnemonic names for registers. âĶ Registers A, X, L can be used by numbers 0, 1, 2.

- 51. 2.3.2 SYMBOL-DEFINING STATEMENTS ï The standard names reflect the usage of the registers. BASE EQUR1 COUNT EQUR2 INDEX EQUR3 ï Assembler directive ORG âĶ Use to indirectly assign values to symbols. ORG value âĶ The assembler resets its LOCCTR to the specified value. âĶ ORG can be useful in label definition.

- 52. 2.3.2 SYMBOL-DEFINING STATEMENTS ï The location counter is used to control assignment of storage in the object program âĶ In most cases, altering its value would result in an incorrect assembly. ï ORG is used http://home.educities.edu.tw/wanker742126 /index.html âĶ SYMBOL is 6-byte, VALUE is 3-byte, and FLAGS is 2-byte.

- 53. 2.3.2 SYMBOL-DEFINING STATEMENTS ï STAB SYMBOL VALUE FLAGS (100 entries) 6 3 2 LOC 1000 STAB RESB 1100 1000 SYMBOL EQU STAB +0 1006 VALUE EQU STAB +6 1009 FLAGS EQU STAB +9 ï Use LDA VALUE, X to fetch the VALUE field form the table entry indicated by the contents of register X.

- 54. 2.3.2 SYMBOL-DEFINING STATEMENTS ï STAB SYMBOL VALUE FLAGS (100 entries) 6 3 2 1000 STAB RESB 1100 ORG STAB 1000 SYMBOL RESB 6 1006 VALUE RESW 1 1009 FLAGS RESB 2 ORGSTAB+ 1100

- 55. 2.3.2 SYMBOL-DEFINING STATEMENTS ï All terms used to specify the value of the new symbol ---must have been defined previously in the program. ... BETA EQUALPHA ALPHA RESW 1 ... Need 2 passes

- 56. 2.3.2 SYMBOL-DEFINING STATEMENTS ï All symbols used to specify new location counter value must have been previously defined. ORG ALPHA BYTE1 RESB 1 BYTE2 RESB 1 BYTE3 RESB 1 ORG ALPHA RESW 1 ï Forward reference ALPHA EQU BETA BETA EQU DELTA DELTA RESW 1 Need 3 passes

- 57. 2.3.3 EXPRESSIONS ï Allow arithmetic expressions formed âĶ Using the operators +, -, Ã, /. âĶ Division is usually defined to produce an integer result. âĶ Expression may be constants, user-defined symbols, or special terms. 106 1036 BUFEND EQU * âĶ Gives BUFEND a value that is the address of the next byte after the buffer area. ï Absolute expressions or relative expressions âĶ A relative term or expression represents some value (S+r), S: starting address, r: the relative value.

- 58. 2.3.3 EXPRESSIONS 107 1000 MAXLEN EQU BUFEND-BUFFER âĶ Both BUFEND and BUFFER are relative terms. âĶ The expression represents absolute value: the difference between the two addresses. âĶ Loc =1000 (Hex) âĶ The value that is associated with the symbol that appears in the source statement. âĶ BUFEND+BUFFER, 100-BUFFER, 3*BUFFER represent neither absolute values nor locations. ï Symbol tables entries

- 59. 2.3.4 PROGRAM BLOCKS ï The source program logically contained main, subroutines, data areas. âĶ In a single block of object code. ï More flexible (Different blocks) âĶ Generate machine instructions (codes) and data in a different order from the corresponding source statements. ï Program blocks âĶ Refer to segments of code that are rearranged within a single object program unit. ï Control sections âĶ Refer to segments of code that are translated into independent object program units.

- 60. 2.3.4 PROGRAM BLOCKS ï Three blocks, Figure 2.11 âĶ Default (USE), CDATA (USE CDATA), CBLKS (USE CBLKS). ï Assembler directive USE âĶ Indicates which portions of the source program blocks. âĶ At the beginning of the program, statements are assumed to be part of the default block. âĶ Lines 92, 103, 123, 183, 208, 252. ï Each program block may contain several separate segments. âĶ The assembler will rearrange these segments to gather together the pieces of each block.

- 61. Main

- 62. RDREC

- 63. WRRE C Figure 2.11 Example of the Program with Multiple Program blocks

- 64. 2.3.4 PROGRAM BLOCKS ï Pass 1, Figure 2.12 âĶ The block number is started form 0. âĶ A separate location counter for each program block. âĶ The location counter for a block is initialized to 0 when the block is first begun. âĶ Assign each block a starting address in the object program (location 0). âĶ Labels, block name or block number, relative addr. âĶ Working table is generated Block name Block number Address End Length Default 0 0000 0065 0066(0~0065) CDATA 1 0066 0070 000B (0~000A) CBLKS 2 0071 1070 1000 (0~0FFF)

- 67. Figure 2.12 Program from figure 2.11 with object code

- 68. 2.3.4 PROGRAM BLOCKS ï Pass 2, Figure 2.12 ï The assembler needs the address for each symbol relative to the start of the object program. ï Loc shows the relative address and block number. ï Notice that the value of the symbol MAXLEN (line 70) is shown without a block number. 20 0006 0 LDA LENGTH 032060 0003(CDATA) +0066 =0069 =TA using program-counter relative addressing TA -(PC) =0069-0009 =0060 =disp

- 69. 2.3.4 PROGRAM BLOCKS ï Separation of the program into blocks. âĶ Because the large buffer (CBLKS) is moved to the end of the object program. âĶ No longer need extended format, base register, simply a LTORG statement. âĶ No need Modification records. âĶ Improve program readability. ï Figure 2.13 âĶ Reflect the starting address of the block as well as the relative location of the code within the block. ï Figure 2.14 âĶ Loader simply loads the object code from each record at the dictated. âĶ CDATA(1) & CBLKS(1) are not actually present in OP.

- 70. 2.3.4 PROGRAM BLOCKS Figure 2.13 Object Program corresponding to figure 2.11

- 71. Figure 2.14 Program blocks from fig 2.11 traced through the assembly and loading processes

- 72. 2.3.5 CONTROL SECTIONS & PROGRAM LINKING ï Control section âĶ Handling of programs that consist of multiple control sections. âĶ Each control section is a part of the program. âĶ Can be assembled, loaded and relocated independently. âĶ Different control sections are most often used for subroutines or other logical subdivisions of a program. âĶ The programmer can assemble, load, and manipulate each of these control sections separately. âĶ More Flexibility then the previous. âĶ Linking control sections together.

- 73. 2.3.5 CONTROL SECTIONS & PROGRAM LINKING ï External references (external symbol references) âĶ Instructions in one control section might need to refer to instructions or data located in another section. ï Figure 2.15, multiple control sections. âĶ Three sections, main COPY, RDREC, WRREC. âĶ Assembler directive CSECT. âĶ Assembler directives EXTDEF and EXTREF for external symbols. âĶ The order of symbols is not significant. COPY START 0 EXTDEF BUFFER, BUFEND, LENGTH EXTREF RDREC, WRREC (symbol name)

- 76. Figure 2.15 Illustrations of Program linking and control sections

- 77. 2.3.5 CONTROL SECTIONS & PROGRAM LINKING ï Figure 2.16, the generated object code. 15 0003 CLOOP +JSUB RDREC 4B100000 160 0017 +STCH BUFFER,X 57900000 ï The LOC of all control section is started form 0 ï RDREC is an external reference. ï The assembler has no idea where the control section containing RDREC will be loaded, so it cannot assemble the address. ï The proper address to be inserted at load time. ï Must use extended format instruction for external reference (M records are needed). 190 0028 MAXLEN WORD BUFEND- BUFFER ï An expression involving two external references.

- 80. Figure 2.16 Program from fig 2.15 with object code.

- 81. 2.3.5 CONTROL SECTIONS & PROGRAM LINKING âĶ The loader will add to this data area with the address of BUFEND and subtract from it the address of BUFFER. (COPY and RDREC for MAXLEN) âĶ Line 190 and 107, in 107, the symbols BUFEND and BUFFER are defined in the same section. âĶ The assembler must remember in which control section a symbol is defined. âĶ The assembler allows the same symbol to be used in different control sections, lines 107 and 190. ï Figure 2.17, two new records. âĶ Defined record for EXTDEF, relative address. âĶ Refer record for EXTREF.

- 83. 2.3.5 CONTROL SECTIONS & PROGRAM LINKING ï Modification record âĶ M âĶ Starting address of the field to be modified, relative to the beginning of the control section (Hex). âĶ Length of the field to be modified, in half-bytes. âĶ Modification flag(+ or -). âĶ External symbol. M^000004^05+RDREC M^000028^06+BUFEND M^000028^06-BUFFER ï Use Figure 2.8 for program relocation.

- 85. Figure 2.17 Object Program corresponding to fig 2.15

- 86. 2.4 ASSEMBLER DESIGN OPTIONS 2.4.1 TWO-PASS ASSEMBLER ï Most assemblers âĶ Processing the source program into two passes. âĶ The internal tables and subroutines that are used only during Pass 1. âĶ The SYMTAB, LITTAB, and OPTAB are used by both passes. ï The main problems to assemble a program in one pass involves forward references.

- 87. 2.4.2 ONE-PASS ASSEMBLERS ï Eliminate forward references âĶ Data items are defined before they are referenced. âĶ But, forward references to labels on instructions cannot be eliminated as easily. âĶ Prohibit forward references to labels. ï Two types of one-pass assembler. (Fig. 2.18) âĶ One type produces object code directly in memory for immediate execution. âĶ The other type produces the usual kind of object program for later execution.

- 90. Figure 2.18 Sample Program for a one Pass assembler.

- 91. 2.4.2 ONE-PASS ASSEMBLERS ï Load-and-go one-pass assembler âĶ The assembler avoids the overhead of writing the object program out and reading it back in. âĶ The object program is produced in memory, the handling of forward references becomes less difficult. âĶ Figure 2.19(a), shows the SYMTAB after scanning line 40 of the program in Figure 2.18. âĶ Since RDREC was not yet defined, the instruction was assembled with no value assigned as the operand address (denote by ----).

- 92. Figure 2.19(a) Object code in memory and symbol table entries for the program in fig 2.18 after scanning line 40

- 93. Figure 2.19(b) Object code in memory and symbol table entries for the program in fig 2.18 after scanning line 150

- 94. 2.4.2 ONE-PASS ASSEMBLERS ï Load-and-go one-pass assembler âĶ RDREC was then entered into SYMTAB as an undefined symbol, the address of the operand field of the instruction (2013) was inserted. âĶ Figure 2.19(b), when the symbol ENDFIL was defined (line 45), the assembler placed its value in the SYMTAB entry; it then inserted this value into the instruction operand field (201C). âĶ At the end of the program, all symbols must be defined without any * in SYMTAB. âĶ For a load-and-go assembler, the actual address must be known at .

- 95. 2.4.2 ONE-PASS ASSEMBLERS ï Another one-pass assembler by generating OP âĶ Generate another Text record with correct operand address. âĶ When the program is loaded, this address will be inserted into the instruction by the action of the loader. âĶ Figure 2.20, the operand addresses for the instructions on lines 15, 30, and 35 have been generated as 0000. âĶ When the definition of ENDFIL is encountered on line 45, the third Text record is generated, the value 2024 is to be loaded at location 201C. âĶ The loader completes forward references.

- 96. Figure 2.20 Object Program for one-pass assembler for Program in fig 2.18

- 97. 2.4.2 ONE-PASS ASSEMBLERS ï In this section, simple one-pass assemblers handled absolute programs (SIC example).

- 98. 2.4.3 MULTI-PASS ASSEMBLERS ï Use EQU, any symbol used on the RHS be defined previously in the source. LOC Pass1 2 3 1000 LDA #0 1000 1000 1000 1003 ALPHA EQU BETA ???? ???? 1003 1003 BETA EQU DELTA ???? 1003 1003 1003 DELTA RESW1 1003 1003 1003 âĶ Need 3 passes! ï Figure 2.21, multi-pass assembler (a)

![2.1.2 ASSEMBLER TABLES AND LOGIC

ï Pass 1 usually writes an intermediate file.

âĶ Contain source statement together with

its assigned address, error indicators.

âĶ This file is used as input to Pass 2.

ï Figure 2.4 shows the two passes of

assembler.

âĶ Format with fields LABEL, OPCODE,

and OPERAND.

âĶ Denote numeric value with the prefix#.

#[OPERAND]](https://image.slidesharecdn.com/assemblerfullslides-230307180654-8253576b/85/assembler_full_slides-ppt-19-320.jpg)