Ch01

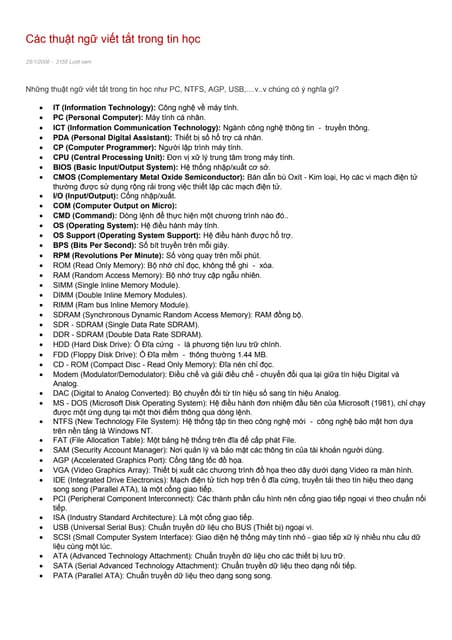

- 1. Ch.1 Kiášŋn trÚc háŧ VXL â MT ï§ Kiášŋn trÚc thiášŋt báŧ háŧ kinh Äiáŧn, cÃĄc háŧ nhÚng ï§ Kiášŋn trÚc háŧ mÃĄy tÃnh âHi Performanceâ - desktop ï§ Hoᚥt Äáŧng cáŧ§a háŧ tháŧng. P&I-Ch1:Architecture 1 1.1. Kiášŋn trÚc Háŧ VXL, MÃĄy tÃnh kinh Äiáŧn â Embedded systems 1.1.1. SÆĄ Äáŧ: 3 phᚧn: - CS, - Ngoᚥi vi & - Interface P&I-Ch1:Architecture 2 1

- 2. 1.1.1. a. Central Sub System â CS: + CPU: Central Processing Unit: âĒ KhÃĄi niáŧm: Là báŧ Äiáŧu khiáŧn trung tÃĒm, tháŧąc hiáŧn cÃīng viáŧc ÄÆ°áŧĢc giao Äáš·t trong báŧ nháŧ chÆ°ÆĄng trÃŽnh bášąng cÃĄch tháŧąc hiáŧn cÃĄc phÃĐp xáŧ lÃ― lÊn cÃĄc biášŋn nháŧ phÃĒn và Äiáŧu khiáŧn thiášŋt báŧ ngoᚥi vi. âĒ CÃīng viáŧc bao gáŧm: â TÃŽm láŧnh, giášĢi mÃĢ láŧnh, [tÃŽm toÃĄn hᚥng, xáŧ lÃ― và cášĨt kášŋt quášĢ], â In/Out váŧi cÃĄc port kiáŧu Interrupt và DMA Äáŧ Äiáŧu khiáŧn thiášŋt báŧ ngoᚥi vi. P&I-Ch1:Architecture 3 ïÄáš·c trÆ°ng â Specifications: âĒ KÃch thÆ°áŧc toÃĄn hᚥng (bit): 4, 8, 12, 16, 32, 64... âĒ Táŧc Äáŧ xáŧ lÃ―: Mips/Gips, clock multiplier, âĒ Kiášŋn trÚc: â RISC (Reduced Instruction Set Computer)vs CISC (Complex Instruction Set Computer), â DSP â Digital Signal Processor, â Micro Controller (Micro Computer One Chip - All in one): âĒ Atmel: ATmega nnn (8bit, RISC), AT91SAMnnn (ARM core) âĒ MicroChip, PICxxx âĒ Cypress: PSoC... âĒ Pinning/Signalling (Data/Address - Mux, Control bus, IRQ, HRQ, RD/WR...), âĒ Register set, âĒ Instruction set â Addressing Modes, âĒ Power Modes: Slow/ sleep/ power down modes, Mips/Wattage âĒ ... P&I-Ch1:Architecture 4 2

- 3. + Memories (Semiconductor): K/n & ROM: KhÃĄi niáŧm: âĒ LÆ°u thÃīng tin (ch/tr và sáŧ liáŧu) dᚥng nháŧ phÃĒn, âĒ Dung lÆ°áŧĢng láŧn (upto 100s Mega bit), táŧc Äáŧ truy nhášp nhanh (downto ns access time). â Physically: tÃnh chášĨt vášt lÃ― nhÆ° thášŋ nà o? âĒ ROMs: Mask ROM, PROM, EPROM, EAROM, OTROM, NonVolatile mem, ... âĒ Là báŧ nháŧ cháŧ Äáŧc, vášŦn lÆ°u thÃīng tin khi mášĨt Äiáŧn, âĒ Package : byte âĒ Access time:100..120ns âĒ Ghi/nᚥp náŧi dung: T/báŧ chuyÊn dÃđng (ROM Burner /Programmator) âĒ Shadow ROM?: copy náŧi dung táŧŦ ROM sang DRAM máŧi khi kháŧi P&I-Ch1:Architecture 5 Äáŧng Memories (Semiconductor): SRAM LÆ°u thÃīng tin tᚥm tháŧi, khÃīng lÆ°u ÄÆ°áŧĢc khi mášĨt Äiáŧn, Äáŧc và ghi ÄÆ°áŧĢc, [Read/Write Mem], - Static RAM: nhanh (80..3 ns), byte/nibble package, mášt Äáŧ byte/chip nháŧ (upto 64/256 KB/ chip), ÄášŊt, tiÊu tháŧĨ cÃīng suášĨt nhiáŧu, - CMOS RAM: chášm và tiÊu tháŧĨ cáŧąc Ãt, less ïW. VdáŧĨ: MC 146818 RealTimeClock-CMOS RAM âĒ DÃđng trong cÃĄc háŧ nháŧ, cache memory. âĒ P&I-Ch1:Architecture 6 3

- 4. Memories (Semiconductor): DRAM Dynamic RAM - DRAM: ï§ Táŧc Äáŧ/Access time (50-70ns), [10..20ns] Pre-fetched ï§ Mášt Äáŧ: bit/chip >> (1 Gbit/chip â 1996, Korea), ï§ bit package => DRAM bank, ï§ TiÊu tháŧĨ W, cÃīng suášĨt nháŧ. ï§ ThÃīng tin cháŧ lÆ°u ÄÆ°áŧĢc 10ms => refreshing DRAM váŧi chu kÃ― @ 7,5ms => pháŧĐc tᚥp. ï§ DÃđng trong cÃĄc háŧ cÃģ dung lÆ°áŧĢng nháŧ láŧn: desktop, laptop, serverâĶ P&I-Ch1:Architecture 7 Memories (Semiconductor): FLASH & Others Flash memory: - EAROM typed, Äáŧc ÄÆ°áŧĢc, xoÃĄ táŧŦng bank, ghi lᚥi ÄÆ°áŧĢc táŧŦng byte. - ThÃīng tin lÆ°u ÄÆ°áŧĢc 20 nÄm, dÃđng nhiáŧu hiáŧn tᚥi và tÆ°ÆĄng lai: BIOS, diskchip, USB stick Mem, uC... - Serial EAROM/FLASH: dÃđng Äáŧ lÆ°u configuration, dÃđng bus I2C (Philips). Và dáŧĨ áŧĐng dáŧĨng : thášŧ vi mᚥch, TV, ... Dual [Quad] Ported RAM: Switching Sys., PGA âĒ RAM-DAC: VGA, VoiceChip âĒ PCMCIA âĒ .... P&I-Ch1:Architecture 8 4

- 5. Memories (Semiconductor): Logically: Báŧ nháŧ chÆ°a thÃīng tin gÃŽ? ï§ Program memory: ï§ CháŧĐa ch/tr Äang tháŧąc hiáŧn ï§ Data memory: ï§ CÃĄc biášŋn ngášŦu nhiÊn, cÃĄc biášŋn cÃģ cášĨu trÚc, ï§ cÃĄc sáŧ liáŧu cÃģ kiáŧu truy nhášp Äáš·c biáŧt (FIFO, LIFOâĶ) P&I-Ch1:Architecture 9 Controllers: [Optional], vi mᚥch, nÃĒng hiáŧu nang (performance) háŧ tháŧng, bao gáŧm: + - Báŧ Äiáŧu khiáŧn Æ°u tiÊn ngášŊt PIC â Priority Interrupt Controller, Intel 8259A - Báŧ Äiáŧu khiáŧn truy nhášp tráŧąc tiášŋp báŧ nháŧ DMAC â Direct memory Access Controller, Intel 8237A. - Timer: mᚥch tᚥo cÃĄc khoášĢng tháŧi gian, PITProgrammable Interval Timer, Intel 8254. - Mᚥch quášĢn tráŧ nháŧ: MMU- Memory Management Unit, sau nà y, thÆ°áŧng ÄÆ°áŧĢc built on chip váŧi CPU. Bus controller/Arbitor P&I-Ch1:Architecture 10 5

- 6. System Bus: K/n âĒ PCB (Printed Circuit Board)/ Cable (Twisted pairs, flat..), slot, connector... dÃđng Äáŧ chuyáŧn thong tin và nÄng lÆ°áŧĢng. âĒ Náŧi hÆĄn 1 slave/master device, time sharing (dÃđng chung) âĒ ThÃīng tin: Address, data, control, status, Power Supply âĒ Chiáŧu (dir), 3 state (Hi Z), Loading âĒ ADDRESS BUS: â TáŧŦ cÃĄc BusMaster (CPU, DMAC, PCI host Controller) Äášŋn SlaveDevices (Mem, Ports) Äáŧ cháŧn/ cháŧ táŧŦng IO/ Mem location trong táŧŦng chu káŧģ bus â n Addr bit ïĻ 2n Mem Locations & 2m IO Locations, m<n. CÃĄc CPU 32bit, Addr và Data sharing - multiplexed P&I-Ch1:Architecture 11 System Bus : Data bus DATA BUS: Sáŧ bit (thÆ°áŧng) phÃđ háŧĢp váŧi kÃch thÆ°áŧc ALU (8/16/32/64 bit) Chuyáŧn Op-code (mÃĢ láŧnh) trong chu káŧģ mÃĄy M1, - CPU <= Program Memory, trong cÃĄc bus cycle M1 Vášn chuyáŧn data: - CPU <=> Data memory, - CPU <=> IO Ports và - Data Memory <=> IO Ports, DMA P&I-Ch1:Architecture 12 6

- 7. System Bus : CONTROL/STATUS BUS: gáŧm cÃĄc tÃn hiáŧu â control bus: Control/ Response: CPU to Others (MEMR, MEMW, IOR, IOW, INTA, HLDA, BHE...), from CPU Status/Request to CPU: IRQ, HRQ, Ready, ... to CPU P&I-Ch1:Architecture 13 System Bus: Power Supply: +5V ïą5%, 10 Äášŋn 20 Amp, cášĨp cho cÃĄc Vi mᚥch sáŧ, RedWire. (3.3V and less) Ground, Gnd, 0V, signal reference ground, chassis, BlackWire. +12V ïą10%, 1Amp, cášĨp cho cÃĄc mᚥch analog, motors, RS232, YellowWire. -12V ïą 10%, 1Amp, (nhÆ° trÊn), BlueWire. - 5 Vïą5%, 0.5 Amp, analog circuitries, WhiteWire. Power good: OrangeWire - MicroControlled Power Supply P&I-Ch1:Architecture 14 7

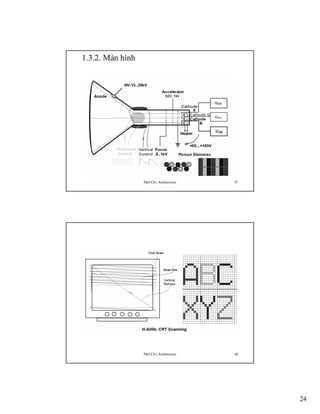

- 8. 1.1.1.B. THIášūT Báŧ NGOáš I VI: Input, Output và dada Storage devices Data Input Devices: - Key board/ Key pad, Touch SCR: sáŧ phÃm, cÃīng ngháŧ phÃm, kiáŧu dÃē phÃm, output code, ghÃĐp náŧi CS - Mouse, track ball - Scanner, Camera, Camcoder Optical Mouse, BarCode reader: Colors, resolution, f, cÃīng ngháŧ CCD - Charge Couple Device, graphics file bit map - bmp. - Digitizer, nhášp graphics file vector - bášĢn Äáŧ - Light Pen, Joy stick (Games) - Demodulator (MODEM): GiášĢi Äiáŧu chášŋ Kiáŧu Äiáŧu chášŋ, táŧc Äáŧ bps, kiáŧu nÃĐn - Microphone, - Reader: RFID Radio Frequency Identification, Finger print - Laser/ LED - Sensor, Transducers, Transmitters: Vášt liáŧu, thiášŋt báŧ,.. biášŋn Äáŧi cÃĄc Äᚥi lÆ°áŧĢng vášt lÃ― - khÃīng Äiáŧn, thà nh tin shiáŧu Äiáŧn Äáŧ nhášy, Äáŧ tuyášŋn P&I-Ch1:Architecture 15 tÃnh, dášĢi Äo... 1.1.1.B. T/Báŧ NGOáš I VI: Data Output Devices: - Displays: Kiáŧu hiáŧn tháŧ: Point/ 7Seg/ Text/ Graphics; Mono Chrome/Color (color numbers); Size, indoor/outdoor, Resolution, Rate of Refreshing... - CÃīng ngháŧ: - LED (Light Emitting Diodes): point, 7(16), Segment, Matrix character box (Bill Board), - Outdoor LED Screen... - Organic LED, - LCD (Liquid Crystal Display): single color, color, active, TFT (thin film transistor - CRT (Cathode Ray Tube). P&I-Ch1:Architecture 16 8

- 9. 1.1.1.B. T/Báŧ NGOáš I VI: Data Output Devices: PRINTERS: Spec: Text-Graphics, Mono-Color, Resolution, ppm â page per minute, Size, Line-PostScript, media... : Pin Printer, Jet Printer, Laser Printer, Thermal Transfer Printer, barcode Printer. High Speed Text Printer, ... P&I-Ch1:Architecture 17 1.1.1.B. T/Báŧ NGOáš I VI: Data Output Devices: Others - Plotter, jet Modulator (MODEM) â Äiáŧu chášŋ Speaker Actuator: Motor (dc/ac, Step), Relay, Valve, P&I-Ch1:Architecture 18 9

- 10. 1.1.1.b. T/báŧ Ngoᚥi vi: Massive Storages: - Magnetic devices: FDD, HDD, RAID, Tape backup drive... - Optical devices: CD [Writer] Drives, Magnetic Optic disk drive... - Semiconductor devices: FlashChip, PCMCIA Card... - Táŧc Äáŧ truy nhášp và dung lÆ°áŧĢng láŧn P&I-Ch1:Architecture 19 1.1.1.c. Interface: âĒ LÃ― do cᚧn interface: khÃĄc nhau giÆ°a CS và wide world: â MáŧĐc tÃn hiáŧu (dÃēng, ÃĄp, analog ... ), kiáŧu biáŧu diáŧ n tin táŧĐc (nhiáŧt Äáŧ, ÃĄp suášĨt, level... ïģ bit) â Táŧc Äáŧ là m viáŧc/táŧc Äáŧ trao Äáŧi sáŧ liáŧu, â KhÃīng Äáŧng báŧ... â NÊn cᚧn cÃģ mᚥch Äiáŧn táŧ Äáŧ thÃch áŧĐng (Adapting - ports) và ch/tr Äiáŧu khiáŧn, gáŧm: â Thiášŋt báŧ (Hardware Circuitries - Adaptors): cáŧng IO: âĒ Input/Output Ports: (Parallel/Serial): ghep náŧi váŧi Computerized devices PPP (KB, Printer, Mouse, Scanner, Modem, camera,... dÃđng VXL Äa nang), character typed devices âĒ Controllers: tháŧąc chášĨt là nhÆ°ng háŧ VXL chuyÊn dÃđng - Äáŧ ghÃĐp náŧi váŧi nhung thiášŋt báŧ chuyÊn dÃđng FDC, HDC (IDE, EIDE), CRTC (EGA, VGA, SVGA...), block typed devices âĒ Converter: Äáŧ chuyáŧn Äáŧi tÃn hiáŧu sáŧ thà nh tÆ°ÆĄng táŧą và ngÆ°áŧĢc lᚥi: ADC, DAC, và dáŧĨ sound card, CMOS sensor... P&I-Ch1:Architecture 20 10

- 11. IO buses: âĒ Expansion bus, IO bus, IO system, ... âĒ ISA, EISA, MC, PCI, USB, IEEE 1394, SSA, IEEE 488, SATA ... P&I-Ch1:Architecture 21 1.1.1.C. INTERFACE: Ch/tr Äiáŧu khiáŧn â Device Driver: - K/n: Hardware or Software? + Software: sášĢn phášĐm cáŧ§a NN lášp trinh + Hardware: luÃīn gan liáŧn váŧi IO hardware LiÊn kášŋt System Programs and/or Application Programs váŧi IO hardware (SPIs và APIs). CÃĄc hà m cáŧ§a thiášŋt báŧ, BIOS, OS hoáš·c theo áŧĐng dáŧĨng: SLLs, DLLs, DRVs, ... Hiáŧn 1 xÃĒu kÃ― táŧą: â â â â mov ah,9 mov dx,offset xau int 21h mov ah,0 int 16h ; BIOS same mov ah,1 int 21h P&I-Ch1:Architecture 22 11

- 12. Case study PC layers Fig. 1b: PCâs Layers (IBM PC Institute) a P&I-Ch1:Architecture 23 1.1.2. KIášūN TRÃC MÃY TÃNH HIáŧU NÄNG CAO - HI PERFORMANCE ARCHITECTURE (SERVER, DESKTOP, LAPTOP) P&I-Ch1:Architecture 24 12

- 13. 1.1.2. HI-PER. ARCHITECTURE:1.1.2.a. Local Buses: Và dáŧĨ VESA VL-Bus 2.0 [late 1993], Memory [1985]. Also called system/host/processor bus. Cháŧ liÊn kášŋt CPU, MMU (gáŧm Cache, DRAM, shadowed ROM ) và PCI Host [Bridge], Ãt, gᚧn, unbuffered (direct connected to Processor); 33, 66, 100, 133, 200, 400, 800 MHz... clock. 32 bit A/D (16 bit support also), burst mode, max 132 MBps, Addr D0 D1 D2 (data 4 byte) D3 D4 H.1.3. Và dáŧĨ burst mode: P&I-Ch1:Architecture 25 1.1.2. HI-PER ARCHITECTURE:1.1.2.b. Hi Speed Bus: Peripheral Component Interconnect - PCI - 5/1993, Intel Ver. 2.0, Open Standard, - Local bus, máŧĐc trung gian giáŧŊa Local và cÃĄc bus chuášĐn khÃĄc (ISA, MC, EISA) thÃīng qua PIC Bridge/Controller. - CÃģ kiáŧm tra parity cho Addr và Data - Auto configuration of all PCI devices, share the same IRQ. - Disabling IRQ => cášĨm toà n báŧ PCI devices. - No DMA, device on PCI bus là bus master (Táŧt cho viáŧc dÃđng MultiTasking OS). - Burst mode: 32 bit @33MHz --> 96..132MBps, tuáŧģ thuáŧc sáŧ byte (táŧŦ 32 byte Äášŋn 4KB). Option 64bit @33MHz --> 264MBps - Most Platforms use:Intel, DEC Alpha, PowerPC, Spark - Modern OS: âBlock Typed Devicesâ: tᚧn suášĨt vášn chuyáŧn cao, nhanh, data block P&I-Ch1:Architecture 26 13

- 14. 1.1.2. HI-PER ARCHITECTURE:1.1.2.c. Expansion Bus: - So called: standard buses, expansion bus, slots, IO bus, IO system, channel bus): ISA, EISA, MC... - MC bus: 32 bit, 10MHz, 20..40MBps, 15 BusMaster, Auto config, 1987, IBM - EISA bus: 32 bit, 8,33 MHz, 33MBps, 4 BMs, AutoConfig (EISA card only), 1989, Compaq - ISA (Industry Small Architecture), AT bus: - Spec. 8/16 bit (data), 8MHz..11MHz, 5..5 MBps max, 1 Bus Master, no PnP, 1984, IBM. - RášĨt pháŧ biášŋn, cÃēn táŧn tᚥi lÃĒu, Espec. @ iPC, - Hᚥn chášŋ sáŧ IRQs, 4 DRQs, - DÃđng DIP switch/jumper Äáŧ config. - No data integrity features (no party checking) - Modern OS: âCharacter Typed Devicesâ P&I-Ch1:Architecture 27 1.2. HOáš T ÄáŧNG CáŧĶA Háŧ THáŧNG: ï§ ï§ ï§ ï§ ï§ Reset, Opcode fetch and Execute, Interrupt, DMA - halt & Ready (wait state - ws) P&I-Ch1:Architecture 28 14

- 15. 1.2. HOáš T ÄáŧNG:1.2.1. LÆ°u Äáŧ táŧng quÃĄt: reset ProgCounter = ResetAddr/vector DMA? n y IRQ? Machine On Halt y y n y OpCode Fetch DMA? n y MaskOn n PC = Intr. Vector OpCodeDecode Execute HÃŽnh 1.3. LÆ°u Äáŧ táŧng quÃĄt cáŧ§a VXL (Motorola), Training courses P&I-Ch1:Architecture 29 1.2. HOáš T ÄáŧNG: 1.2.2. Reset : Cold Start: BášĨm nÚt reset/Power-On =>XoÃĄ trᚥng thÃĄi hiáŧn hà nh, cášĨm ngášŊt, DMA. CPU ÄÆ°áŧĢc kháŧi tᚥo (PC-Program Counter (hoáš·c CS:IP), Flags và SP...). CÃĄc thiášŋt báŧ trong háŧ cÃđng ÄÆ°áŧĢc reset. (Sau khi reset, CPU sáš― tim và t/h láŧnh â váŧi cÃĄc tháŧ§ táŧĨc sau) Warm Start: do láŧnh gáŧi, (Int 19h, Ctrl_Alt_Del) POST (Power On Self Test - ch/tr monitor/ BIOS) Äáŧ kiáŧm tra máŧi thiášŋt báŧ theo nguyÊn tášŊc ghi và Äáŧc lᚥi (Registers, RAM) hoáš·c Äáŧc và kiáŧm tra Check Sum (ROM). Initializing - kháŧi tᚥo: Äáš·t cÃĄc tham sáŧ => configuring. [MÃĄy tÃnh - Nᚥp háŧ Äiáŧu hà nh ]. P&I-Ch1:Architecture 30 15

- 16. 1.2.3. DMA: (Xem Ch. 3.2.) 1.2.4. Interrupt: (Xem Ch. 3.3.) P&I-Ch1:Architecture 31 1.2. HOáš T ÄáŧNG: 1.2.5. TÃŽm và tháŧąc hiáŧn láŧnh : - Diáŧ n ra cháŧ§ yášŋu trong tháŧi gian hoᚥt Äáŧng, ngoᚥi tráŧŦ láŧnh HLT. - Ch/tr ngÃīn ngáŧŊ mÃĄy: tášp háŧĢp cÃĄc láŧnh cÃģ cášĨu trÚc, cÃģ nghÄĐa, tháŧąc hiáŧn 1 thuášt toÃĄn. - Chu káŧģ láŧnh (Instruction Cycle): KhoášĢng tháŧi gian CPU tháŧąc hiáŧn xong 1 láŧnh, gáŧm: tÃŽm láŧnh, giášĢi mÃĢ láŧnh, [tÃŽm toÃĄn hᚥng và tháŧąc hiáŧn láŧnh (tháŧąc hiáŧn cÃĄc phÃĐp xáŧ lÃ― hoáš·c và o-ra)]. áŧ dà i láŧnh: (CISC)1 hay nhiáŧu byte, Tháŧi gian t/h:(CISC)1/nhiáŧu chu káŧģ mÃĄy (chu káŧģ bus). Chu káŧģ mÃĄy (Bus/Machine Cycle): tháŧi gian BusMaster tháŧąc hiáŧn thao tÃĄc trÊn bus: Äáŧc/ghi Ãī nháŧ hay IO port Clock cycle: Chu káŧģ mÃĄy: 4..12 chu káŧģ clock, tuáŧģ CPU. P&I-Ch1:Architecture 32 16

- 17. 1.2. HOáš T ÄáŧNG: 1.2.5. TÃŽm và tháŧąc hiáŧn láŧnh : - Diáŧ n ra cháŧ§ yášŋu trong tháŧi gian hoᚥt Äáŧng, ngoᚥi tráŧŦ láŧnh HLT. - Ch/tr ngÃīn ngáŧŊ mÃĄy: tášp háŧĢp cÃĄc láŧnh cÃģ cášĨu trÚc, cÃģ nghÄĐa, tháŧąc hiáŧn 1 thuášt toÃĄn. - Chu káŧģ láŧnh (Instruction Cycle): KhoášĢng tháŧi gian CPU tháŧąc hiáŧn xong 1 láŧnh, gáŧm: tÃŽm láŧnh, giášĢi mÃĢ láŧnh, [tÃŽm toÃĄn hᚥng và tháŧąc hiáŧn láŧnh (tháŧąc hiáŧn cÃĄc phÃĐp xáŧ lÃ― hoáš·c và o-ra)]. áŧ dà i láŧnh: (CISC)1 hay nhiáŧu byte, Tháŧi gian t/h:(CISC)1/nhiáŧu chu káŧģ mÃĄy (chu káŧģ bus). Chu káŧģ mÃĄy (Bus/Machine Cycle): tháŧi gian BusMaster tháŧąc hiáŧn thao tÃĄc trÊn bus: Äáŧc/ghi Ãī nháŧ hay IO port Clock cycle: Chu káŧģ mÃĄy: 4..12 chu káŧģ clock, tuáŧģ CPU. P&I-Ch1:Architecture 33 1.2. HOáš T ÄáŧNG: 1.2.5. TÃŽm và tháŧąc hiáŧn láŧnh : - Diáŧ n ra cháŧ§ yášŋu trong tháŧi gian hoᚥt Äáŧng, ngoᚥi tráŧŦ láŧnh HLT. - Ch/tr ngÃīn ngáŧŊ mÃĄy: tášp háŧĢp cÃĄc láŧnh cÃģ cášĨu trÚc, cÃģ nghÄĐa, tháŧąc hiáŧn 1 thuášt toÃĄn. - Chu káŧģ láŧnh (Instruction Cycle): KhoášĢng tháŧi gian CPU tháŧąc hiáŧn xong 1 láŧnh, gáŧm: tÃŽm láŧnh, giášĢi mÃĢ láŧnh, [tÃŽm toÃĄn hᚥng và tháŧąc hiáŧn láŧnh (tháŧąc hiáŧn cÃĄc phÃĐp xáŧ lÃ― hoáš·c và o-ra)]. Äáŧ dà i láŧnh: (CISC)1 hay nhiáŧu byte, Tháŧi gian t/h:(CISC)1/nhiáŧu chu káŧģ mÃĄy (chu káŧģ bus). Chu káŧģ mÃĄy (Bus/Machine Cycle): tháŧi gian BusMaster tháŧąc hiáŧn thao tÃĄc trÊn bus: Äáŧc/ghi Ãī nháŧ hay IO port Clock cycle: Chu káŧģ mÃĄy: 4..12 chu káŧģ clock, tuáŧģ CPU. P&I-Ch1:Architecture 34 17

- 18. 1.2. HOáš T ÄáŧNG: 8 CPUâs + DMA Bus cycles: - M1, opcode fetching, Addr =>Program mem, -MEMR - Data mem Reading, Addr=>Data mem, -MEMR - Data mem Writing, Addr=>Data mem, -MEMW - Input Port Reading, Addr=> IO space, -IOR - Out Port Writing, Addr => IO space, -IOW - Interrupt Acknowledge, -INTA, - Halt, waiting for Ext. Intr. hoáš·c reset - Bus Idle ThÊm 2 chu káŧģ bus cáŧ§a DMAC: - IOR-MemW DMA bus cycle và - MemR-IOW DMA bus cycle. P&I-Ch1:Architecture 35 1.2. HOáš T ÄáŧNG: 1.2.6. Wait State (Ready): - ThÆ°áŧng dÃđng Äáŧ ghÃĐp náŧi: báŧ nháŧ, ngoᚥi vi táŧc Äáŧ chášm. - Hoᚥt Äáŧng Khi BusMaster phÃĄt Äáŧa cháŧ & tÃn hiáŧu Äáŧc/ghi (thÊm cÃĄc tÃn hiáŧu khÃĄc) Äáŧ tháŧąc hiáŧn 1 chu káŧģ bus, MMU/IO port [Controller] cháŧ§ Äáŧng phÃĄt ra tÃn hiáŧu Ready=0 (not Ready) Äáŧ yÊu cᚧu BusMaster giáŧŊ nguyÊn trᚥng thÃĄi bus thÊm 1 [và i] nháŧp clock. P&I-Ch1:Architecture 36 18

- 19. Case Study: IOW bus cycles w/o and w 1 wait state: P&I-Ch1:Architecture 37 1.3. Thiášŋt báŧ ngoᚥi vi: 1.3.1. Key boards: âĒ KhÃĄi niáŧm: â Thiášŋt báŧ nhášp sáŧ liáŧu và ra láŧnh cho mÃĄy â PhÃĒn loᚥi theo cÃīng ngháŧ: âĒ Contact keys âĒ Non contact keys: Cap/Ind â Ãt dÃđng âĒ Membrane keys: contact key â Technical Problems: âĒ Key bouncing: âĒ key debouced Tech â RS FF (cáŧ), delay âĒ Ghost keys: Nhiáŧu phÃm bášĨm Äáŧng tháŧi â Bà n phiams ÄÆ°áŧĢc táŧ cháŧĐc thà nh ma trášn nxm. â GiášĢi phÃĄp: khÃīng Äáŧc, Äáŧc bášĨm trÆ°áŧc/nhášĢ sau P&I-Ch1:Architecture 38 19

- 20. âĒ Key organization: matrix âĒ Key polling: Là KT xÃĄc Äáŧnh hà ng/cáŧt â Line reversal technique: (Fig. 1.5) â Scan (Fig.) P&I-Ch1:Architecture 39 P&I-Ch1:Architecture 40 20

- 23. Scan procedure (Fig 904a) âĒ PC keyboard: 15 col â 8 row 1. i=0 2. Col (i) =0 only, delay(1) 3. If Rows <> 1111 1111 then (5) 4. Inc (i), if i>15 then goto (1) 5. Delay for debouncing. Read Row code, Read Col code, encode Col-Row. 6. Convert R-C => KB Scanned code 7. Sending to PC bit by bit. 8. Polling for key releasing and delay for debouncing 9. Goto (2) P&I-Ch1:Architecture 45 P&I-Ch1:Architecture 46 23

- 25. Bà i tášp chÆ°ÆĄng 1 âĒ TÃŽm hiáŧu bus ISA (Ch4), thiášŋt kášŋ mᚥch logic Äáŧ chÃĻn cÃĄc ws cho ISA slot khi CPU Äáŧc/ ghi 1 Äáŧa cháŧ cáŧng âĒ Tᚥo mᚥch kiáŧm tra parity - 74HC280 P&I-Ch1:Architecture 49 25

![1.1.1. a. Central Sub System â CS:

+ CPU: Central Processing Unit:

âĒ KhÃĄi niáŧm: LÃ báŧ Äiáŧu khiáŧn trung tÃĒm, tháŧąc hiáŧn

cÃīng viáŧc ÄÆ°áŧĢc giao Äáš·t trong báŧ nháŧ chÆ°ÆĄng trÃŽnh

bášąng cÃĄch tháŧąc hiáŧn cÃĄc phÃĐp xáŧ lÃ― lÊn cÃĄc biášŋn nháŧ

phÃĒn và Äiáŧu khiáŧn thiášŋt báŧ ngoᚥi vi.

âĒ CÃīng viáŧc bao gáŧm:

â TÃŽm láŧnh, giášĢi mÃĢ láŧnh, [tÃŽm toÃĄn hᚥng, xáŧ lÃ― và cášĨt kášŋt

quášĢ],

â In/Out váŧi cÃĄc port kiáŧu Interrupt và DMA Äáŧ Äiáŧu khiáŧn

thiášŋt báŧ ngoᚥi vi.

P&I-Ch1:Architecture

3

ïÄáš·c trÆ°ng â Specifications:

âĒ KÃch thÆ°áŧc toÃĄn hᚥng (bit): 4, 8, 12, 16, 32, 64...

âĒ Táŧc Äáŧ xáŧ lÃ―: Mips/Gips, clock multiplier,

âĒ Kiášŋn trÚc:

â RISC (Reduced Instruction Set Computer)vs CISC (Complex

Instruction Set Computer),

â DSP â Digital Signal Processor,

â Micro Controller (Micro Computer One Chip - All in one):

âĒ Atmel: ATmega nnn (8bit, RISC), AT91SAMnnn (ARM core)

âĒ MicroChip, PICxxx

âĒ Cypress: PSoC...

âĒ Pinning/Signalling (Data/Address - Mux, Control bus, IRQ, HRQ,

RD/WR...),

âĒ Register set,

âĒ Instruction set â Addressing Modes,

âĒ Power Modes: Slow/ sleep/ power down modes, Mips/Wattage

âĒ ...

P&I-Ch1:Architecture

4

2](https://image.slidesharecdn.com/ch01-131127033145-phpapp02/85/Ch01-2-320.jpg)

![+ Memories (Semiconductor): K/n & ROM:

KhÃĄi niáŧm:

âĒ LÆ°u thÃīng tin (ch/tr và sáŧ liáŧu) dᚥng nháŧ phÃĒn,

âĒ Dung lÆ°áŧĢng láŧn (upto 100s Mega bit), táŧc Äáŧ truy

nhášp nhanh (downto ns access time).

â Physically: tÃnh chášĨt vášt lÃ― nhÆ° thášŋ nà o?

âĒ ROMs: Mask ROM, PROM, EPROM, EAROM, OTROM,

NonVolatile mem, ...

âĒ LÃ báŧ nháŧ cháŧ Äáŧc, vášŦn lÆ°u thÃīng tin khi mášĨt Äiáŧn,

âĒ Package : byte

âĒ Access time:100..120ns

âĒ Ghi/nᚥp náŧi dung: T/báŧ chuyÊn dÃđng (ROM Burner

/Programmator)

âĒ Shadow ROM?: copy náŧi dung táŧŦ ROM sang DRAM máŧi khi kháŧi

P&I-Ch1:Architecture

5

Äáŧng

Memories (Semiconductor): SRAM

LÆ°u thÃīng tin tᚥm tháŧi, khÃīng lÆ°u ÄÆ°áŧĢc khi mášĨt Äiáŧn,

Äáŧc và ghi ÄÆ°áŧĢc, [Read/Write Mem],

- Static RAM:

nhanh (80..3 ns),

byte/nibble package,

mášt Äáŧ byte/chip nháŧ (upto 64/256 KB/ chip),

ÄášŊt, tiÊu tháŧĨ cÃīng suášĨt nhiáŧu,

- CMOS RAM: chášm và tiÊu tháŧĨ cáŧąc Ãt, less ïW.

VdáŧĨ: MC 146818 RealTimeClock-CMOS RAM

âĒ DÃđng trong cÃĄc háŧ nháŧ, cache memory.

âĒ

P&I-Ch1:Architecture

6

3](https://image.slidesharecdn.com/ch01-131127033145-phpapp02/85/Ch01-3-320.jpg)

![Memories (Semiconductor): DRAM

Dynamic RAM - DRAM:

ï§ Táŧc Äáŧ/Access time (50-70ns), [10..20ns] Pre-fetched

ï§ Mášt Äáŧ: bit/chip >> (1 Gbit/chip â 1996, Korea),

ï§ bit package => DRAM bank,

ï§ TiÊu tháŧĨ W, cÃīng suášĨt nháŧ.

ï§ ThÃīng tin cháŧ lÆ°u ÄÆ°áŧĢc 10ms => refreshing DRAM váŧi chu

kÃ― @ 7,5ms => pháŧĐc tᚥp.

ï§ DÃđng trong cÃĄc háŧ cÃģ dung lÆ°áŧĢng nháŧ láŧn: desktop, laptop,

serverâĶ

P&I-Ch1:Architecture

7

Memories (Semiconductor): FLASH & Others

Flash memory:

- EAROM typed, Äáŧc ÄÆ°áŧĢc, xoÃĄ táŧŦng bank, ghi lᚥi ÄÆ°áŧĢc táŧŦng byte.

- ThÃīng tin lÆ°u ÄÆ°áŧĢc 20 nÄm, dÃđng nhiáŧu hiáŧn tᚥi và tÆ°ÆĄng lai:

BIOS, diskchip, USB stick Mem, uC...

- Serial EAROM/FLASH: dÃđng Äáŧ lÆ°u configuration, dÃđng bus

I2C (Philips). Và dáŧĨ áŧĐng dáŧĨng : thášŧ vi mᚥch, TV, ...

Dual [Quad] Ported RAM: Switching Sys., PGA

âĒ RAM-DAC: VGA, VoiceChip

âĒ PCMCIA

âĒ ....

P&I-Ch1:Architecture

8

4](https://image.slidesharecdn.com/ch01-131127033145-phpapp02/85/Ch01-4-320.jpg)

![Memories (Semiconductor): Logically:

Báŧ nháŧ chÆ°a thÃīng tin gÃŽ?

ï§ Program memory:

ï§ CháŧĐa ch/tr Äang tháŧąc hiáŧn

ï§ Data memory:

ï§ CÃĄc biášŋn ngášŦu nhiÊn, cÃĄc biášŋn cÃģ cášĨu trÚc,

ï§ cÃĄc sáŧ liáŧu cÃģ kiáŧu truy nhášp Äáš·c biáŧt (FIFO, LIFOâĶ)

P&I-Ch1:Architecture

9

Controllers: [Optional], vi mᚥch, nÃĒng hiáŧu nang

(performance) háŧ tháŧng, bao gáŧm:

+

- Báŧ Äiáŧu khiáŧn Æ°u tiÊn ngášŊt PIC â Priority Interrupt

Controller, Intel 8259A

- Báŧ Äiáŧu khiáŧn truy nhášp tráŧąc tiášŋp báŧ nháŧ DMAC â

Direct memory Access Controller, Intel 8237A.

- Timer: mᚥch tᚥo cÃĄc khoášĢng tháŧi gian, PITProgrammable Interval Timer, Intel 8254.

- Mᚥch quášĢn tráŧ nháŧ: MMU- Memory Management

Unit, sau nà y, thÆ°áŧng ÄÆ°áŧĢc built on chip váŧi CPU.

Bus controller/Arbitor

P&I-Ch1:Architecture

10

5](https://image.slidesharecdn.com/ch01-131127033145-phpapp02/85/Ch01-5-320.jpg)

![1.1.1.b. T/báŧ Ngoᚥi vi: Massive Storages:

- Magnetic devices: FDD, HDD, RAID, Tape backup

drive...

- Optical devices: CD [Writer] Drives, Magnetic Optic disk

drive...

- Semiconductor devices: FlashChip, PCMCIA Card...

- Táŧc Äáŧ truy nhášp và dung lÆ°áŧĢng láŧn

P&I-Ch1:Architecture

19

1.1.1.c. Interface:

âĒ LÃ― do cᚧn interface: khÃĄc nhau giÆ°a CS và wide world:

â MáŧĐc tÃn hiáŧu (dÃēng, ÃĄp, analog ... ), kiáŧu biáŧu diáŧ

n tin táŧĐc

(nhiáŧt Äáŧ, ÃĄp suášĨt, level... ïģ bit)

â Táŧc Äáŧ là m viáŧc/táŧc Äáŧ trao Äáŧi sáŧ liáŧu,

â KhÃīng Äáŧng báŧ...

â NÊn cᚧn cÃģ mᚥch Äiáŧn táŧ Äáŧ thÃch áŧĐng (Adapting - ports) vÃ

ch/tr Äiáŧu khiáŧn, gáŧm:

â Thiášŋt báŧ (Hardware Circuitries - Adaptors): cáŧng IO:

âĒ Input/Output Ports: (Parallel/Serial): ghep náŧi váŧi Computerized

devices PPP (KB, Printer, Mouse, Scanner, Modem, camera,... dÃđng

VXL Äa nang), character typed devices

âĒ Controllers: tháŧąc chášĨt là nhÆ°ng háŧ VXL chuyÊn dÃđng - Äáŧ ghÃĐp náŧi váŧi

nhung thiášŋt báŧ chuyÊn dÃđng FDC, HDC (IDE, EIDE), CRTC (EGA,

VGA, SVGA...), block typed devices

âĒ Converter: Äáŧ chuyáŧn Äáŧi tÃn hiáŧu sáŧ thà nh tÆ°ÆĄng táŧą và ngÆ°áŧĢc lᚥi:

ADC, DAC, và dáŧĨ sound card, CMOS sensor...

P&I-Ch1:Architecture

20

10](https://image.slidesharecdn.com/ch01-131127033145-phpapp02/85/Ch01-10-320.jpg)

![1.1.2. HI-PER. ARCHITECTURE:1.1.2.a. Local Buses:

VÃ dáŧĨ VESA VL-Bus 2.0 [late 1993], Memory [1985].

Also called system/host/processor bus.

Cháŧ liÊn kášŋt CPU, MMU (gáŧm Cache, DRAM, shadowed ROM )

và PCI Host [Bridge],

Ãt, gᚧn, unbuffered (direct connected to Processor);

33, 66, 100, 133, 200, 400, 800 MHz... clock.

32 bit A/D (16 bit support also), burst mode, max 132 MBps,

Addr

D0

D1

D2

(data 4 byte)

D3

D4

H.1.3. VÃ dáŧĨ burst mode:

P&I-Ch1:Architecture

25

1.1.2. HI-PER ARCHITECTURE:1.1.2.b. Hi Speed Bus:

Peripheral Component Interconnect - PCI

- 5/1993, Intel Ver. 2.0, Open Standard,

- Local bus, máŧĐc trung gian giáŧŊa Local và cÃĄc bus chuášĐn

khÃĄc (ISA, MC, EISA) thÃīng qua PIC Bridge/Controller.

- CÃģ kiáŧm tra parity cho Addr và Data

- Auto configuration of all PCI devices, share the same IRQ.

- Disabling IRQ => cášĨm toà n báŧ PCI devices.

- No DMA, device on PCI bus là bus master (Táŧt cho viáŧc

dÃđng MultiTasking OS).

- Burst mode: 32 bit @33MHz --> 96..132MBps, tuáŧģ

thuáŧc sáŧ

byte (táŧŦ 32 byte Äášŋn 4KB). Option 64bit @33MHz -->

264MBps

- Most Platforms use:Intel, DEC Alpha, PowerPC, Spark

- Modern OS: âBlock Typed Devicesâ: tᚧn suášĨt vášn chuyáŧn

cao, nhanh, data block

P&I-Ch1:Architecture

26

13](https://image.slidesharecdn.com/ch01-131127033145-phpapp02/85/Ch01-13-320.jpg)

![1.2. HOáš T ÄáŧNG:1.2.1. LÆ°u Äáŧ táŧng quÃĄt:

reset

ProgCounter = ResetAddr/vector

DMA?

n

y

IRQ?

Machine

On Halt

y

y

n

y

OpCode Fetch

DMA?

n

y

MaskOn

n

PC = Intr. Vector

OpCodeDecode

Execute

HÃŽnh 1.3. LÆ°u Äáŧ táŧng quÃĄt cáŧ§a VXL (Motorola),

Training courses

P&I-Ch1:Architecture

29

1.2. HOáš T ÄáŧNG: 1.2.2. Reset :

Cold Start: BášĨm nÚt reset/Power-On =>XoÃĄ trᚥng thÃĄi hiáŧn hà nh,

cášĨm ngášŊt, DMA. CPU ÄÆ°áŧĢc kháŧi tᚥo (PC-Program Counter (hoáš·c

CS:IP), Flags và SP...). CÃĄc thiášŋt báŧ trong háŧ cÃđng ÄÆ°áŧĢc reset.

(Sau khi reset, CPU sáš― tim và t/h láŧnh â váŧi cÃĄc tháŧ§ táŧĨc sau)

Warm Start: do láŧnh gáŧi, (Int 19h, Ctrl_Alt_Del)

POST (Power On Self Test - ch/tr monitor/ BIOS) Äáŧ kiáŧm tra máŧi

thiášŋt báŧ theo nguyÊn tášŊc ghi và Äáŧc lᚥi (Registers, RAM) hoáš·c Äáŧc

và kiáŧm tra Check Sum (ROM).

Initializing - kháŧi tᚥo: Äáš·t cÃĄc tham sáŧ => configuring.

[MÃĄy tÃnh - Nᚥp háŧ Äiáŧu hà nh ].

P&I-Ch1:Architecture

30

15](https://image.slidesharecdn.com/ch01-131127033145-phpapp02/85/Ch01-15-320.jpg)

![1.2.3. DMA: (Xem Ch. 3.2.)

1.2.4. Interrupt: (Xem Ch. 3.3.)

P&I-Ch1:Architecture

31

1.2. HOáš T ÄáŧNG:

1.2.5. TÃŽm và tháŧąc hiáŧn láŧnh :

- Diáŧ

n ra cháŧ§ yášŋu trong tháŧi gian hoᚥt Äáŧng, ngoᚥi tráŧŦ láŧnh HLT.

- Ch/tr ngÃīn ngáŧŊ mÃĄy: tášp háŧĢp cÃĄc láŧnh cÃģ cášĨu trÚc, cÃģ nghÄĐa, tháŧąc

hiáŧn 1 thuášt toÃĄn.

- Chu káŧģ láŧnh (Instruction Cycle): KhoášĢng tháŧi gian CPU tháŧąc

hiáŧn xong 1 láŧnh, gáŧm: tÃŽm láŧnh, giášĢi mÃĢ láŧnh, [tÃŽm toÃĄn hᚥng vÃ

tháŧąc hiáŧn láŧnh (tháŧąc hiáŧn cÃĄc phÃĐp xáŧ lÃ― hoáš·c và o-ra)].

áŧ dà i láŧnh: (CISC)1 hay nhiáŧu byte,

Tháŧi gian t/h:(CISC)1/nhiáŧu chu káŧģ mÃĄy (chu káŧģ bus).

Chu káŧģ mÃĄy (Bus/Machine Cycle): tháŧi gian BusMaster

tháŧąc hiáŧn thao tÃĄc trÊn bus: Äáŧc/ghi Ãī nháŧ hay IO port

Clock cycle: Chu káŧģ mÃĄy: 4..12 chu káŧģ clock, tuáŧģ CPU.

P&I-Ch1:Architecture

32

16](https://image.slidesharecdn.com/ch01-131127033145-phpapp02/85/Ch01-16-320.jpg)

![1.2. HOáš T ÄáŧNG:

1.2.5. TÃŽm và tháŧąc hiáŧn láŧnh :

- Diáŧ

n ra cháŧ§ yášŋu trong tháŧi gian hoᚥt Äáŧng, ngoᚥi tráŧŦ láŧnh HLT.

- Ch/tr ngÃīn ngáŧŊ mÃĄy: tášp háŧĢp cÃĄc láŧnh cÃģ cášĨu trÚc, cÃģ nghÄĐa, tháŧąc

hiáŧn 1 thuášt toÃĄn.

- Chu káŧģ láŧnh (Instruction Cycle): KhoášĢng tháŧi gian CPU tháŧąc

hiáŧn xong 1 láŧnh, gáŧm: tÃŽm láŧnh, giášĢi mÃĢ láŧnh, [tÃŽm toÃĄn hᚥng vÃ

tháŧąc hiáŧn láŧnh (tháŧąc hiáŧn cÃĄc phÃĐp xáŧ lÃ― hoáš·c và o-ra)].

áŧ dà i láŧnh: (CISC)1 hay nhiáŧu byte,

Tháŧi gian t/h:(CISC)1/nhiáŧu chu káŧģ mÃĄy (chu káŧģ bus).

Chu káŧģ mÃĄy (Bus/Machine Cycle): tháŧi gian BusMaster

tháŧąc hiáŧn thao tÃĄc trÊn bus: Äáŧc/ghi Ãī nháŧ hay IO port

Clock cycle: Chu káŧģ mÃĄy: 4..12 chu káŧģ clock, tuáŧģ CPU.

P&I-Ch1:Architecture

33

1.2. HOáš T ÄáŧNG:

1.2.5. TÃŽm và tháŧąc hiáŧn láŧnh :

- Diáŧ

n ra cháŧ§ yášŋu trong tháŧi gian hoᚥt Äáŧng, ngoᚥi tráŧŦ láŧnh HLT.

- Ch/tr ngÃīn ngáŧŊ mÃĄy: tášp háŧĢp cÃĄc láŧnh cÃģ cášĨu trÚc, cÃģ nghÄĐa, tháŧąc

hiáŧn 1 thuášt toÃĄn.

- Chu káŧģ láŧnh (Instruction Cycle): KhoášĢng tháŧi gian CPU tháŧąc

hiáŧn xong 1 láŧnh, gáŧm: tÃŽm láŧnh, giášĢi mÃĢ láŧnh, [tÃŽm toÃĄn hᚥng vÃ

tháŧąc hiáŧn láŧnh (tháŧąc hiáŧn cÃĄc phÃĐp xáŧ lÃ― hoáš·c và o-ra)].

Äáŧ dà i láŧnh: (CISC)1 hay nhiáŧu byte,

Tháŧi gian t/h:(CISC)1/nhiáŧu chu káŧģ mÃĄy (chu káŧģ bus).

Chu káŧģ mÃĄy (Bus/Machine Cycle): tháŧi gian BusMaster

tháŧąc hiáŧn thao tÃĄc trÊn bus: Äáŧc/ghi Ãī nháŧ hay IO port

Clock cycle: Chu káŧģ mÃĄy: 4..12 chu káŧģ clock, tuáŧģ CPU.

P&I-Ch1:Architecture

34

17](https://image.slidesharecdn.com/ch01-131127033145-phpapp02/85/Ch01-17-320.jpg)

![1.2. HOáš T ÄáŧNG: 8 CPUâs + DMA Bus cycles:

- M1, opcode fetching, Addr =>Program mem, -MEMR

- Data mem Reading, Addr=>Data mem, -MEMR

- Data mem Writing, Addr=>Data mem, -MEMW

- Input Port Reading, Addr=> IO space, -IOR

- Out Port Writing, Addr => IO space, -IOW

- Interrupt Acknowledge, -INTA,

- Halt, waiting for Ext. Intr. hoáš·c reset

- Bus Idle

ThÊm 2 chu káŧģ bus cáŧ§a DMAC:

- IOR-MemW DMA bus cycle vÃ

- MemR-IOW DMA bus cycle.

P&I-Ch1:Architecture

35

1.2. HOáš T ÄáŧNG: 1.2.6. Wait State (Ready):

- ThÆ°áŧng

dÃđng Äáŧ ghÃĐp náŧi: báŧ nháŧ, ngoᚥi vi táŧc

Äáŧ chášm.

- Hoᚥt Äáŧng Khi BusMaster phÃĄt Äáŧa cháŧ & tÃn

hiáŧu Äáŧc/ghi (thÊm cÃĄc tÃn hiáŧu khÃĄc) Äáŧ tháŧąc

hiáŧn 1 chu káŧģ bus, MMU/IO port [Controller]

cháŧ§ Äáŧng phÃĄt ra tÃn hiáŧu Ready=0 (not

Ready) Äáŧ yÊu cᚧu BusMaster giáŧŊ nguyÊn

trᚥng thÃĄi bus thÊm 1 [và i] nháŧp clock.

P&I-Ch1:Architecture

36

18](https://image.slidesharecdn.com/ch01-131127033145-phpapp02/85/Ch01-18-320.jpg)