Delays in verilog

- 1. DELAYS IN VERILOG Delays in Verilog Presented BY: Jitu Mistry At eiTRA centre

- 2. Why delays and timing so important ? ïĻ They allow a degree of realism to be incorporated into the modeling process. ïĻ The time taken for changes to propagate through a module may lead to race conditions in other modules. ïĻ Some designs, such as high speed microprocessors, may have very tight timing requirements that must be met. 7/30/2013 2

- 3. Types of Delays. ïĻ Depending on the design approach, ïž Gate-level Modeling ïž Dataflow Modeling ïž Behavioral Modeling 7/19/2013 3

- 4. Gate level modelling ïĻ Propagation delay : through the gate, and the time taken for the output to actually change state, according to input. ïĻ Gate level modelling delay described below as:- ïž Rise ïž Fall Min/Typ/Max values ïž Turn-off 7/19/2013 4

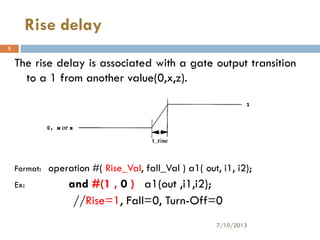

- 5. The rise delay is associated with a gate output transition to a 1 from another value(0,x,z). Format: operation #( Rise_Val, fall_Val ) a1( out, i1, i2); Ex: and #(1 , 0 ) a1(out ,i1,i2); //Rise=1, Fall=0, Turn-Off=0 7/19/2013 5 Rise delay

- 6. 7/19/2013 6 ïĻ buf #(2,0) (out,in);

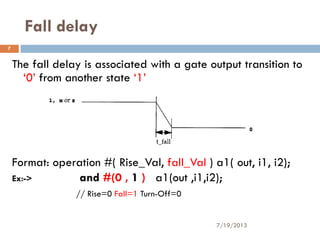

- 7. Fall delay The fall delay is associated with a gate output transition to â0â from another state â1â Format: operation #( Rise_Val, fall_Val ) a1( out, i1, i2); Ex:-> and #(0 , 1 ) a1(out ,i1,i2); // Rise=0 Fall=1 Turn-Off=0 7/19/2013 7

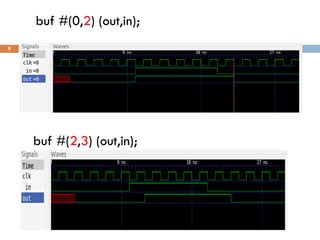

- 8. 7/19/2013 8 buf #(0,2) (out,in); buf #(2,3) (out,in);

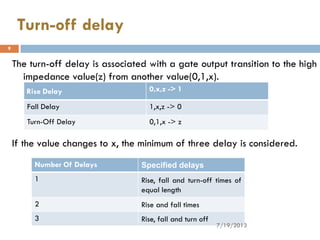

- 9. The turn-off delay is associated with a gate output transition to the high impedance value(z) from another value(0,1,x). If the value changes to x, the minimum of three delay is considered. Rise Delay 0,x,z -> 1 Fall Delay 1,x,z -> 0 Turn-Off Delay 0,1,x -> z Number Of Delays Specified delays 1 Rise, fall and turn-off times of equal length 2 Rise and fall times 3 Rise, fall and turn off 7/19/2013 9 Turn-off delay

- 10. ï For each type of delay, there are three values, min,typ and max can be specified. ï Any one value can be chosen at the start of the simulation Because of IC fabrication process variations. Ex: And #( 2:3:4, 3:4:5, 4:5:6) a ( out, i1, i2 ); 7/19/2013 10 Min, typ or max values

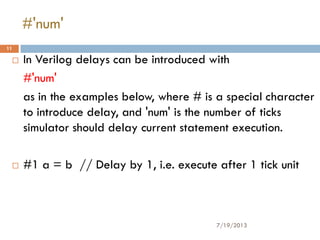

- 11. ïĻ In Verilog delays can be introduced with #'num' as in the examples below, where # is a special character to introduce delay, and 'num' is the number of ticks simulator should delay current statement execution. ïĻ #1 a = b // Delay by 1, i.e. execute after 1 tick unit 7/19/2013 11 #'num'

- 12. ïĻ We can provide num value of different way by variable or/and parameter ïĪ Parameter delata= 10; #delta out = in1& in2 Note: # There is no way we could synthesize delays, but of course we can add delay to particular signals by adding buffers. 7/19/2013 12 #'num'

- 13. #5 y = x + z; // line will execute after 5 unit delay And Y = #5 x + z; // assignment to y after the 5 unit delay 7/19/2013 13 #'num'

- 14. Dataflow Modelling ïĻ As dataflow modelling use the concept of signals or values ïĻ The delays are associated with the Net (e.g. a Wire) along which the value is transmitted ïĻ Delays values control the time between the change in a right hand side operand and when the new value is assigned to the left hand side. #5 a = b; means a ï ï ï b 7/19/2013 14

- 15. Dataflow Modelling ïĻ Since values can be assigned to a net in a number of ways, there are corresponding methods of specifying the appropriate delays. 1. Regular Assignment Delay 2. Net Declaration Delay 3. Implicit Continuous Assignment 7/19/2013 15

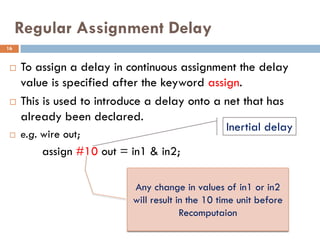

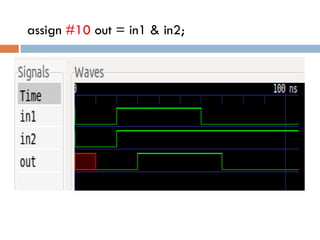

- 16. Regular Assignment Delay ïĻ To assign a delay in continuous assignment the delay value is specified after the keyword assign. ïĻ This is used to introduce a delay onto a net that has already been declared. ïĻ e.g. wire out; assign #10 out = in1 & in2; 7/19/2013 16 Any change in values of in1 or in2 will result in the 10 time unit before Recomputaion Inertial delay

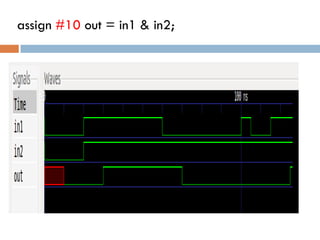

- 17. Net Declaration Delay ïĻ The Delay to be attributed to a Net can be associated when the Net is declared. ïĻ e.g. // net delays wire #10 out; assign out = in1 & in2; // the same effect as the following, generally preferable wire out; assign #10 out = in1 & in2; 7/19/2013 17

- 18. assign #10 out = in1 & in2;

- 19. assign #10 out = in1 & in2;

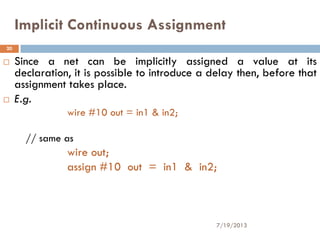

- 20. Implicit Continuous Assignment ïĻ Since a net can be implicitly assigned a value at its declaration, it is possible to introduce a delay then, before that assignment takes place. ïĻ E.g. wire #10 out = in1 & in2; // same as wire out; assign #10 out = in1 & in2; 7/19/2013 20

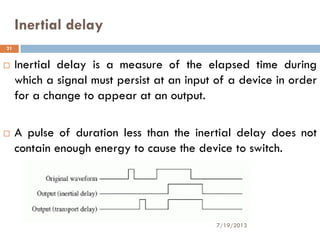

- 21. Inertial delay ïĻ Inertial delay is a measure of the elapsed time during which a signal must persist at an input of a device in order for a change to appear at an output. ïĻ A pulse of duration less than the inertial delay does not contain enough energy to cause the device to switch. 7/19/2013 21

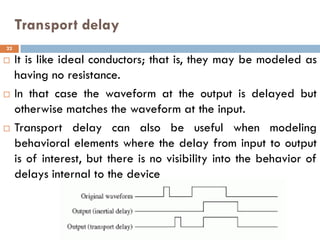

- 22. Transport delay ïĻ It is like ideal conductors; that is, they may be modeled as having no resistance. ïĻ In that case the waveform at the output is delayed but otherwise matches the waveform at the input. ïĻ Transport delay can also be useful when modeling behavioral elements where the delay from input to output is of interest, but there is no visibility into the behavior of delays internal to the device 7/19/2013 22

- 23. DELAYS IN BEHAVIOURAL MODELLING 7/19/2013 23 There are following method ïą Delay-based timing control ïžRegular ïžIntra- assignment ïžZero delay

- 24. REGULAR DELAY CONTROL ïĻ Regular delay control is used when a non âzero delay is specified to the left of a procedural assignment ïĻ This is sometimes also referred to as inter- assignment delay control ïĻ Example:#10 q = x+y; ïĻ It simply waits for the appropriate number of timesteps before executing the command. 7/19/2013 24

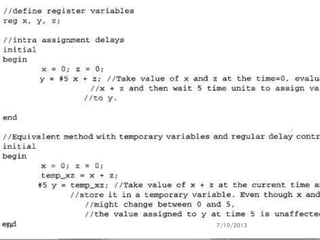

- 25. INTRA ASSIGNMENT DELAY ïĻ Instead of specifying delay control to the left of tha assignment, it is possible to assign a delay to the right of the assignment operator. ïĻ Example: q = #10 x+y; ïĻ With this kind of delay ,the value of x+y is stored at the time that the assignment is executed, but this value is not assigned to q until after the delay period. 7/19/2013 25

- 26. 7/19/201326

- 28. ZERO DELAY ïĻ Zero delay is a method to ensure that a statement is executed last,after all other statements in that simulation time are execcuted. ïĻ This is to to elminate race arround conditions. ïĻ However if there are multiple zero delay statements,the order between them is nondeterministic. ïĻ EX:#0 x=1 7/19/2013 28

- 29. SEQENTIAL BLOCKS ïĻ The keywords begin and end are used to group statements into seqential blocks. ïĻ A statement is executed only after its preceeding statement completes execution. 7/19/2013 29

- 30. 7/19/201330

- 31. PARALLEL BLOCKS ïĻ Parallel blocks, specified by keywords fork and join,provide intresting simulation features. ïĻ Statements in a parallel block are executed concurrently. ïĻ Ordering of statements is controlled by delay or event control assigned to each statement. 7/19/2013 31

- 32. 7/19/201332

- 33. Setup and Holdtime ïĻ Very important in sequential logic. ïĻ $setup(data_line, clk_line, limit); ïĻ $hold(clk_line, data_line, limit); 7/19/2013 33