Lezione1 - MIPS & SPIM Unicam

- 1. MIPS & SPIM MIPS & SPIM Modulo del Corso di Architettura degli Elaboratori Nicola Paoletti Universit` di Camerino a Scuola di Scienze e Tecnologie 29 Marzo 2011 AA 2010/2011

- 2. MIPS & SPIM Informazioni utili (1/2) Email: nicola.paoletti@unicam.it Orario: Marted` 16:00-17:00 ı, Pagina web del corso: . . . Pagina Facebook del corso: http://www.facebook.com/#!/pages/Mips-Spim-Unicam/164156776971007

- 3. MIPS & SPIM Informazioni utili (2/2) Modalit` dâesame: Progetto + Relazione a Materiale didattico e dâapprofondimento: reperibile sulla pagina web del corso (non appena pronta)

- 4. MIPS & SPIM Obiettivi del corso Architettura HW del processore MIPS32 Set di istruzioni del processore MIPS32 Il tool SPIM, un simulatore MIPS32

- 5. MIPS & SPIM Introduzione Riepilogo 1 Introduzione

- 6. MIPS & SPIM Introduzione Concetti fondamentali (1/2) Linguaggio macchina Il linguaggio basato su valori numerici utilizzato dai computer per memorizzare ed eseguire programmi. Alfabeto: {0, 1}. Linguaggio assembly Rappresentazione simbolica del linguaggio macchina; utilizza simboli invece di numeri per rappresentare istruzioni, registri e dati. Pi` leggibile rispetto al linguaggio macchina. u Linguaggio ad alto livello Astrae i dettagli hardware; si avvicina al linguaggio naturale.

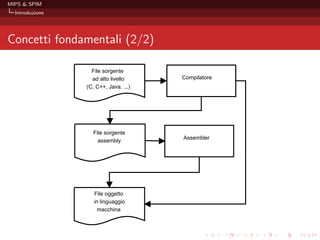

- 7. MIPS & SPIM Introduzione Concetti fondamentali (2/2) File sorgente ad alto livello Compilatore (C, C++, Java, ...) File sorgente Assembler assembly File oggetto in linguaggio macchina

- 8. MIPS & SPIM Introduzione Linguaggio assembly (1/2) Solleva il programmatore dal lavorare direttamente con sequenze di bit. Associa ad ogni comando nel linguaggio macchina (codice operativo) una sequenza di caratteri (forma mnemonica) Le locazioni di memoria e i registri possono essere indirizzati con identiïŹcatori testuali, anzich` attraverso i loro indirizzi e binari.

- 9. MIPS & SPIM Introduzione Linguaggio assembly (2/2) Dipende direttamente dallâhardware â ogni CPU o famiglia di â CPU ha un suo proprio assembly Pro: eïŹcienza; controllo completo sullâhw. Contro: scarsa portabilit`; scrittura del codice lenta e a costosa.

- 10. MIPS & SPIM Introduzione Architetture RISC (1/2) RISC (Reduced Instruction Set Computer) ` una strategia di e progettazione per microprocessori caratterizzata da operazioni semplici eseguibili in tempi rapidi e uniformi; tanti registri per memorizzare risultati intermedi. ` E opposto alla ïŹlosoïŹa CISC (Complex Instruction Set Computer), in cui si hanno istruzioni pi` complesse con tempi di esecuzione u diversi.

- 11. MIPS & SPIM Introduzione Cenni storici (1/2) Anni â70 Memorie costose e compilatori ineïŹcienti â costruzione di chip in grado di eseguire in hardware istruzioni â anche molto complesse â architetture CISC â La pi` celebre CISC ISA (Instruction Set Architecture) ` lâIntel x86, u e che copre tutta la gamma dei processori Intel dagli anni â70 ïŹno ad oggi (Intel Pentium, Core Duo, Core Quad, Core Extreme, . . . )

- 12. MIPS & SPIM Introduzione Cenni storici (2/2) Anni â80 Memorie pi` economiche e compilatori pi` eïŹcienti u u Divario tra velocit` CPU e velocit` memorie a a Il 90% del tempo, il processore utilizza sempre un sottoinsieme ristretto di istruzioni Esecuzione diretta solo di queste poche istruzioni, lasciando al compilatore lâonere di spezzettare le istruzioni pi` complesse u Limitare gli accessi in memoria centrale con poche e semplici modalit` di accesso (load/store) e aumentando il numero di a registri nel processore. â â architetture RISC

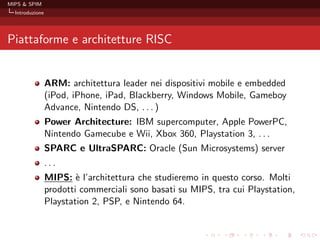

- 13. MIPS & SPIM Introduzione Piattaforme e architetture RISC ARM: architettura leader nei dispositivi mobile e embedded (iPod, iPhone, iPad, Blackberry, Windows Mobile, Gameboy Advance, Nintendo DS, . . . ) Power Architecture: IBM supercomputer, Apple PowerPC, Nintendo Gamecube e Wii, Xbox 360, Playstation 3, . . . SPARC e UltraSPARC: Oracle (Sun Microsystems) server ... MIPS: ` lâarchitettura che studieremo in questo corso. Molti e prodotti commerciali sono basati su MIPS, tra cui Playstation, Playstation 2, PSP, e Nintendo 64.

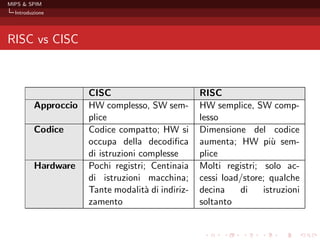

- 14. MIPS & SPIM Introduzione RISC vs CISC CISC RISC Approccio HW complesso, SW sem- HW semplice, SW comp- plice lesso Codice Codice compatto; HW si Dimensione del codice occupa della decodiïŹca aumenta; HW pi` sem- u di istruzioni complesse plice Hardware Pochi registri; Centinaia Molti registri; solo ac- di istruzioni macchina; cessi load/store; qualche Tante modalit` di indiriz- a decina di istruzioni zamento soltanto