Sequential circuits

Download as PPT, PDF8 likes4,767 views

This document discusses sequential circuits and their analysis. It defines sequential logic as circuits whose outputs depend not only on current inputs but also past inputs, requiring some type of memory. There are two types of sequential circuits: synchronous use a clock for synchronization, while asynchronous can change output at any time. Analysis of sequential circuits involves obtaining a description of the input-output-state sequence over time using techniques like logic diagrams, state tables, characteristic tables, and state diagrams. Various flip-flop designs are presented, including the SR latch, D latch using transmission gates, and master-slave flip-flop. Timing considerations like clock period and setup time are also covered.

1 of 22

Downloaded 110 times

Recommended

Latches and flip flop

Latches and flip flopShuaib Hotak

Ã˝

This document discusses latches and flip flops, which are types of sequential logic circuits. It describes the basic components and functioning of latches like SR latches, D latches, and gated latches. For flip flops, it covers SR flip flops, D flip flops, JK flip flops, and master-slave flip flops. The key differences between latches and flip flops are that latches do not have a clock input while flip flops are edge-triggered by a clock signal. Latches and flip flops are used as basic storage elements in more complex sequential circuits and in computer components like registers and RAM.Combinational Circuits & Sequential Circuits

Combinational Circuits & Sequential Circuitsgourav kottawar

Ã˝

This document discusses and compares combinational and sequential circuits. It provides examples of common combinational circuits like half adders, full adders, decoders, and multiplexers. It also discusses sequential circuits elements like flip flops and shift registers. The document then focuses on adders in more detail, explaining half adders, full adders, and ripple carry adders through diagrams and examples.Counters

CountersKetaki_Pattani

Ã˝

This document discusses different types of counters used in digital circuits. It defines a counter as a sequential circuit that cycles through a sequence of states in response to clock pulses. Binary counters count in binary and can count from 0 to 2n-1 with n flip-flops. Asynchronous counters have flip-flops that are not triggered simultaneously by a clock, while synchronous counters use a common clock for all flip-flops. Other counter types include ring counters, Johnson counters, and decade counters. The document provides examples of binary, asynchronous, and synchronous counters and discusses their applications in areas like timing sequences and addressing memory.Latches and flip flops

Latches and flip flopsmubashir farooq

Ã˝

This document discusses latches and flip-flops. It begins by explaining the difference between latches and flip-flops, noting that latches do not have a clock signal while flip-flops do. It then discusses several types of flip-flops - RS, Clocked RS, D, JK, and T - providing the definition, explanation, circuit diagram, and truth table for each. It also discusses several types of latches - SR, Gated SR, and D - providing the definition, explanation, and circuit diagram for each. The document aims to explain the key characteristics and workings of various latches and flip-flops.Flipflop

Flipflopsohamdodia27

Ã˝

Flip-flops are basic memory circuits that have two stable states and can store one bit of information. There are several types of flip-flops including SR, JK, D, and T. The SR flip-flop has two inputs called set and reset that determine its output state, while the JK flip-flop's J and K inputs can toggle its output. Flip-flops like the D and JK can be constructed from more basic flip-flops. For sequential circuits, flip-flops are made synchronous using a clock input so their state only changes at the clock edge.sequential circuits

sequential circuitsUnsa Shakir

Ã˝

Sequential circuits have outputs determined by both the current inputs and previous outputs due to the inclusion of memory elements. Combinational circuits only have outputs determined by the current inputs. Sequential circuits contain logic gates arranged in parallel and feedback loops allowing the circuit to store past states, while combinational circuits only depend on the current input combination. There are different types of sequential circuits including those controlled by a clock signal from a clock generator that produces periodic pulses defining the circuit timing.Shift Registers

Shift RegistersAbhilash Nair

Ã˝

Shift registers are digital circuits composed of flip-flops that can shift data from one stage to the next. They can be configured for serial-in serial-out, serial-in parallel-out, parallel-in serial-out, or parallel-in parallel-out data movement. Common applications include converting between serial and parallel data, temporary data storage, and implementing counters. MSI shift registers like the 74LS164 and 74LS166 provide 8-bit shift register functionality.Sequential circuits

Sequential circuitsDrSonali Vyas

Ã˝

The document discusses sequential circuits and different types of flip flops and counters. It describes how sequential circuits have memory and their output depends on current and past inputs. There are two main types of sequential circuits - asynchronous which can change state at any time and synchronous which use a clock signal to control when the output can change state. Common types of flip flops described include SR, JK, D and T flip flops. Counters can be asynchronous with the clock signal rippling through or synchronous where all flip flops share the same clock.Sequential Logic Circuit

Sequential Logic CircuitRamasubbu .P

Ã˝

Sequential circuits consist of combinational logic and memory elements like latches and flip-flops. There are different types of latches and flip-flops that differ in their trigger mechanisms and outputs, including SR latches, D latches, and edge-triggered flip-flops like SR, D, and JK flip-flops. Asynchronous inputs can directly set or reset flip-flop outputs independent of the clock signal.Counters

CountersRevathi Subramaniam

Ã˝

Counters ,its types, modulo counters, design of synchronous and asynchronous counters are given a detailed viewSequential circuits in Digital Electronics

Sequential circuits in Digital ElectronicsVinoth Loganathan

Ã˝

The document explains about the concepts of sequential circuits in Digital electronics.

This will be helpful for the beginners in VLSI and electronics students.Counters

CountersAbhilash Nair

Ã˝

This document provides information about different types of counters, including asynchronous counters, synchronous counters, MSI counters, and specific counter integrated circuits. It defines counters and describes their basic characteristics. It discusses asynchronous ripple counters and their timing. It provides examples of decade and binary counters. It describes synchronous counters and MSI counters like the 74LS163 4-bit synchronous counter. Finally, it provides truth tables, logic diagrams, and application information for common counter ICs like the 7490, 7492, 7493, and 74LS163.Logic families

Logic familiesSARITHA REDDY

Ã˝

This document discusses different logic families including Resistor Transistor Logic (RTL), Diode Transistor Logic (DTL), Transistor-Transistor Logic (TTL), and Emitter Coupled Logic (ECL). It provides circuit diagrams and explanations of the working principles for each logic family. Key characteristics like fan-in, fan-out, propagation delay, noise immunity, and power dissipation are compared for each logic family.Introduction to Counters

Introduction to CountersISMT College

Ã˝

The document discusses synchronous and asynchronous counters. It defines a counter as a digital circuit that counts input pulses. Asynchronous counters have flip-flops that change state at different times since they do not share a common clock. Synchronous counters have all flip-flops change simultaneously due to a shared global clock, allowing them to operate at higher frequencies. The document provides examples of 2-bit, 3-bit, and 4-bit synchronous binary counters as well as a 4-bit synchronous decade counter along with their operations and timing diagrams.Race around and master slave flip flop

Race around and master slave flip flopShubham Singh

Ã˝

The Reason Why we use master slave JK flip flop instead of simple level triggered flip flop is Racing condition which can be successfully avoided using two SR latches fed with inverted clocks.SHIFT REGISTERS

SHIFT REGISTERSkumari36

Ã˝

Shift registers are constructed using flip-flops connected in a way to store and transfer digital data. Data is stored at the Q output of D flip-flops during a clock pulse. Shift registers allow data to be transferred between flip-flops upon a clock edge. There are four types of data movement: serial in serial out, serial in parallel out, parallel in serial out, and parallel in parallel out. Shift registers can be loaded serially or in parallel and are used in applications like pseudo random pattern generators, ring counters, and Johnson counters.Programmable logic devices

Programmable logic devicesISMT College

Ã˝

This document discusses programmable logic devices (PLDs), including their basic components and types. PLDs are integrated circuits that can be configured by the user to perform different logic functions. They contain programmable AND and OR gates that allow the user to define the logic function by programming the connections between the gates. Common types of PLDs include PROM, PAL, and PLA, which differ in whether their AND gates and/or OR gates are programmable. The document provides examples and diagrams to illustrate how basic logic functions can be implemented using each type of PLD.Multiplexers & Demultiplexers

Multiplexers & DemultiplexersJayanshu Gundaniya

Ã˝

Multiplexers and demultiplexers allow digital information from multiple sources to be routed through a single line. A multiplexer has multiple data inputs, select lines to choose an input, and a single output. A demultiplexer has a single input, select lines to choose an output, and multiple outputs. Bigger multiplexers and demultiplexers can be built by cascading smaller ones. Multiplexers can implement logic functions by using the select lines as variables and routing the input lines to the output.Flip-Flop || Digital Electronics

Flip-Flop || Digital ElectronicsMd Sadequl Islam

Ã˝

The document discusses flip-flops, which are basic electronic circuits that have two stable states and can serve as one bit of digital memory. It defines what a flip-flop is and describes several common types of flip-flops, including SR, JK, T, D, and master-slave edge-triggered flip-flops. The document provides brief explanations of how each flip-flop type works and is implemented using logic gates.J - K & MASTERSLAVE FLIPFLOPS

J - K & MASTERSLAVE FLIPFLOPSKrishma Parekh

Ã˝

JK & MASTER SLAVE FLIP-FLOP

The document discusses the JK flip-flop, which removes invalid states that occur in other flip-flops. The JK flip-flop has inputs for J, K, preset, clear, and clock, and outputs of Q and Q'. It operates in four modes - hold, set, reset, toggle - based on the states of J and K. A master-slave JK flip-flop uses two JK flip-flops connected by an inverter to avoid race-around conditions, with the master capturing the input on the rising clock edge and the slave outputting it on the falling edge.Latch and flip flop

Latch and flip flopGargiKhanna1

Ã˝

Latch and flip flop circuits are used to store digital information. A latch can store a bit as long as power is applied, while a flip flop uses feedback to store a bit even after inputs change. There are different types of flip flops like SR, JK, D and T flip flops that store bits based on their input conditions and clock signal. Flip flops are edge triggered which means they change state only on rising or falling edge of the clock signal. This provides synchronization between logic and memory in digital circuits.Combinational circuit

Combinational circuitSatya P. Joshi

Ã˝

Combinational circuit, Half Adder,Full Adder, Half Subtractor, Full Subtractor, Multiplexers

, Demultiplexer

, Decoder

, Encoder

Latches and flip flops

Latches and flip flopssheheryar ahmed

Ã˝

This document discusses latches and flip-flops. It describes the SR latch, gated SR latch, D latch, and gated D latch. It also covers edge-triggered flip-flops including the SR, D, and JK flip-flops. The key uses of flip-flops are for data storage, data transfer, counting, and frequency division in digital circuits and sequential logic.Finite state machines

Finite state machinesdennis gookyi

Ã˝

This document discusses finite state machines (FSMs), specifically Moore and Mealy machines. It defines FSMs as circuits with a combinational block and memory block that can exist in multiple states, transitioning between states based on inputs. Moore machines output depends solely on the current state, while Mealy machines output depends on both the current state and inputs. Moore machines are safer since output only changes at clock edges, while Mealy machines are faster since output relies on inputs. Choosing between them depends on factors like whether synchronous/asynchronous operation is needed and whether speed or safety is a higher priority.MASTER SLAVE JK FLIP FLOP & T FLIP FLOP

MASTER SLAVE JK FLIP FLOP & T FLIP FLOPSmit Shah

Ã˝

Sequential logic circuits use a clock signal to control the timing of state changes in memory elements like flip-flops. A master-slave JK flip-flop allows both the J and K inputs to be simultaneously 1, toggling the output. When this occurs, the master section is reset if the clock is 1, and set if the clock is 0, preventing unstable oscillations between circuits. multiplexers and demultiplexers

multiplexers and demultiplexersUnsa Shakir

Ã˝

This document discusses multiplexers and demultiplexers. It defines them as devices that allow digital information from several sources to be routed onto a single line (multiplexers) or distributed to multiple output lines (demultiplexers). The key properties of multiplexers and demultiplexers are described, including the relationship between the number of inputs, outputs, and selection lines. Examples of implementing multiplexers and demultiplexers using logic gates are provided.Register in Digital Logic

Register in Digital LogicISMT College

Ã˝

A register is a group of flip-flops that can store multiple bits of data. There are four types of shift registers: serial-in serial-out (SISO), serial-in parallel-out (SIPO), parallel-in serial-out (PISO), and parallel-in parallel-out (PIPO). Shift registers allow data to move between flip-flops on each clock pulse. Ring counters and Johnson counters are examples of shift register counters that produce repeating output sequences.Types of flip flops ppt

Types of flip flops pptViraj Shah

Ã˝

This document discusses different types of flip-flops including edge-triggered flip-flops like the S-R, D, and J-K flip-flops. It describes their characteristics such as how their output changes depending on the input and clock signal. The S-R flip-flop can be set or reset. The D flip-flop copies its input to the output on the clock edge. The J-K flip-flop can toggle its output. The T flip-flop is a single-input version of the J-K flip-flop that toggles its output. Flip-flops have applications in data transfer and frequency division.DIGITAL ELECTRONICS PPT 1.ppt

DIGITAL ELECTRONICS PPT 1.pptAmitpaswan23

Ã˝

This document discusses sequential circuits and flip-flops. It defines sequential logic as logic where the output depends not only on the current input but also past input values. It introduces flip-flops as a type of sequential circuit that can respond, or update, only at specific times controlled by a clock signal. The document provides details on SR latches and SR flip-flops, including their characteristic tables that define the logical properties and output based on the current state and inputs.Sequential Circuit

Sequential CircuitHeman Pathak

Ã˝

This document discusses various types of flip-flops including RS, D, JK, T flip-flops. It describes their characteristic tables and excitation tables. It also covers sequential circuits, state tables, state diagrams, state equations, and the design of counters using flip-flops. Key topics include the use of flip-flops as memory elements, master-slave configurations to prevent race-around conditions, and how to analyze and design sequential circuits and counters.More Related Content

What's hot (20)

Sequential Logic Circuit

Sequential Logic CircuitRamasubbu .P

Ã˝

Sequential circuits consist of combinational logic and memory elements like latches and flip-flops. There are different types of latches and flip-flops that differ in their trigger mechanisms and outputs, including SR latches, D latches, and edge-triggered flip-flops like SR, D, and JK flip-flops. Asynchronous inputs can directly set or reset flip-flop outputs independent of the clock signal.Counters

CountersRevathi Subramaniam

Ã˝

Counters ,its types, modulo counters, design of synchronous and asynchronous counters are given a detailed viewSequential circuits in Digital Electronics

Sequential circuits in Digital ElectronicsVinoth Loganathan

Ã˝

The document explains about the concepts of sequential circuits in Digital electronics.

This will be helpful for the beginners in VLSI and electronics students.Counters

CountersAbhilash Nair

Ã˝

This document provides information about different types of counters, including asynchronous counters, synchronous counters, MSI counters, and specific counter integrated circuits. It defines counters and describes their basic characteristics. It discusses asynchronous ripple counters and their timing. It provides examples of decade and binary counters. It describes synchronous counters and MSI counters like the 74LS163 4-bit synchronous counter. Finally, it provides truth tables, logic diagrams, and application information for common counter ICs like the 7490, 7492, 7493, and 74LS163.Logic families

Logic familiesSARITHA REDDY

Ã˝

This document discusses different logic families including Resistor Transistor Logic (RTL), Diode Transistor Logic (DTL), Transistor-Transistor Logic (TTL), and Emitter Coupled Logic (ECL). It provides circuit diagrams and explanations of the working principles for each logic family. Key characteristics like fan-in, fan-out, propagation delay, noise immunity, and power dissipation are compared for each logic family.Introduction to Counters

Introduction to CountersISMT College

Ã˝

The document discusses synchronous and asynchronous counters. It defines a counter as a digital circuit that counts input pulses. Asynchronous counters have flip-flops that change state at different times since they do not share a common clock. Synchronous counters have all flip-flops change simultaneously due to a shared global clock, allowing them to operate at higher frequencies. The document provides examples of 2-bit, 3-bit, and 4-bit synchronous binary counters as well as a 4-bit synchronous decade counter along with their operations and timing diagrams.Race around and master slave flip flop

Race around and master slave flip flopShubham Singh

Ã˝

The Reason Why we use master slave JK flip flop instead of simple level triggered flip flop is Racing condition which can be successfully avoided using two SR latches fed with inverted clocks.SHIFT REGISTERS

SHIFT REGISTERSkumari36

Ã˝

Shift registers are constructed using flip-flops connected in a way to store and transfer digital data. Data is stored at the Q output of D flip-flops during a clock pulse. Shift registers allow data to be transferred between flip-flops upon a clock edge. There are four types of data movement: serial in serial out, serial in parallel out, parallel in serial out, and parallel in parallel out. Shift registers can be loaded serially or in parallel and are used in applications like pseudo random pattern generators, ring counters, and Johnson counters.Programmable logic devices

Programmable logic devicesISMT College

Ã˝

This document discusses programmable logic devices (PLDs), including their basic components and types. PLDs are integrated circuits that can be configured by the user to perform different logic functions. They contain programmable AND and OR gates that allow the user to define the logic function by programming the connections between the gates. Common types of PLDs include PROM, PAL, and PLA, which differ in whether their AND gates and/or OR gates are programmable. The document provides examples and diagrams to illustrate how basic logic functions can be implemented using each type of PLD.Multiplexers & Demultiplexers

Multiplexers & DemultiplexersJayanshu Gundaniya

Ã˝

Multiplexers and demultiplexers allow digital information from multiple sources to be routed through a single line. A multiplexer has multiple data inputs, select lines to choose an input, and a single output. A demultiplexer has a single input, select lines to choose an output, and multiple outputs. Bigger multiplexers and demultiplexers can be built by cascading smaller ones. Multiplexers can implement logic functions by using the select lines as variables and routing the input lines to the output.Flip-Flop || Digital Electronics

Flip-Flop || Digital ElectronicsMd Sadequl Islam

Ã˝

The document discusses flip-flops, which are basic electronic circuits that have two stable states and can serve as one bit of digital memory. It defines what a flip-flop is and describes several common types of flip-flops, including SR, JK, T, D, and master-slave edge-triggered flip-flops. The document provides brief explanations of how each flip-flop type works and is implemented using logic gates.J - K & MASTERSLAVE FLIPFLOPS

J - K & MASTERSLAVE FLIPFLOPSKrishma Parekh

Ã˝

JK & MASTER SLAVE FLIP-FLOP

The document discusses the JK flip-flop, which removes invalid states that occur in other flip-flops. The JK flip-flop has inputs for J, K, preset, clear, and clock, and outputs of Q and Q'. It operates in four modes - hold, set, reset, toggle - based on the states of J and K. A master-slave JK flip-flop uses two JK flip-flops connected by an inverter to avoid race-around conditions, with the master capturing the input on the rising clock edge and the slave outputting it on the falling edge.Latch and flip flop

Latch and flip flopGargiKhanna1

Ã˝

Latch and flip flop circuits are used to store digital information. A latch can store a bit as long as power is applied, while a flip flop uses feedback to store a bit even after inputs change. There are different types of flip flops like SR, JK, D and T flip flops that store bits based on their input conditions and clock signal. Flip flops are edge triggered which means they change state only on rising or falling edge of the clock signal. This provides synchronization between logic and memory in digital circuits.Combinational circuit

Combinational circuitSatya P. Joshi

Ã˝

Combinational circuit, Half Adder,Full Adder, Half Subtractor, Full Subtractor, Multiplexers

, Demultiplexer

, Decoder

, Encoder

Latches and flip flops

Latches and flip flopssheheryar ahmed

Ã˝

This document discusses latches and flip-flops. It describes the SR latch, gated SR latch, D latch, and gated D latch. It also covers edge-triggered flip-flops including the SR, D, and JK flip-flops. The key uses of flip-flops are for data storage, data transfer, counting, and frequency division in digital circuits and sequential logic.Finite state machines

Finite state machinesdennis gookyi

Ã˝

This document discusses finite state machines (FSMs), specifically Moore and Mealy machines. It defines FSMs as circuits with a combinational block and memory block that can exist in multiple states, transitioning between states based on inputs. Moore machines output depends solely on the current state, while Mealy machines output depends on both the current state and inputs. Moore machines are safer since output only changes at clock edges, while Mealy machines are faster since output relies on inputs. Choosing between them depends on factors like whether synchronous/asynchronous operation is needed and whether speed or safety is a higher priority.MASTER SLAVE JK FLIP FLOP & T FLIP FLOP

MASTER SLAVE JK FLIP FLOP & T FLIP FLOPSmit Shah

Ã˝

Sequential logic circuits use a clock signal to control the timing of state changes in memory elements like flip-flops. A master-slave JK flip-flop allows both the J and K inputs to be simultaneously 1, toggling the output. When this occurs, the master section is reset if the clock is 1, and set if the clock is 0, preventing unstable oscillations between circuits. multiplexers and demultiplexers

multiplexers and demultiplexersUnsa Shakir

Ã˝

This document discusses multiplexers and demultiplexers. It defines them as devices that allow digital information from several sources to be routed onto a single line (multiplexers) or distributed to multiple output lines (demultiplexers). The key properties of multiplexers and demultiplexers are described, including the relationship between the number of inputs, outputs, and selection lines. Examples of implementing multiplexers and demultiplexers using logic gates are provided.Register in Digital Logic

Register in Digital LogicISMT College

Ã˝

A register is a group of flip-flops that can store multiple bits of data. There are four types of shift registers: serial-in serial-out (SISO), serial-in parallel-out (SIPO), parallel-in serial-out (PISO), and parallel-in parallel-out (PIPO). Shift registers allow data to move between flip-flops on each clock pulse. Ring counters and Johnson counters are examples of shift register counters that produce repeating output sequences.Types of flip flops ppt

Types of flip flops pptViraj Shah

Ã˝

This document discusses different types of flip-flops including edge-triggered flip-flops like the S-R, D, and J-K flip-flops. It describes their characteristics such as how their output changes depending on the input and clock signal. The S-R flip-flop can be set or reset. The D flip-flop copies its input to the output on the clock edge. The J-K flip-flop can toggle its output. The T flip-flop is a single-input version of the J-K flip-flop that toggles its output. Flip-flops have applications in data transfer and frequency division.Similar to Sequential circuits (20)

DIGITAL ELECTRONICS PPT 1.ppt

DIGITAL ELECTRONICS PPT 1.pptAmitpaswan23

Ã˝

This document discusses sequential circuits and flip-flops. It defines sequential logic as logic where the output depends not only on the current input but also past input values. It introduces flip-flops as a type of sequential circuit that can respond, or update, only at specific times controlled by a clock signal. The document provides details on SR latches and SR flip-flops, including their characteristic tables that define the logical properties and output based on the current state and inputs.Sequential Circuit

Sequential CircuitHeman Pathak

Ã˝

This document discusses various types of flip-flops including RS, D, JK, T flip-flops. It describes their characteristic tables and excitation tables. It also covers sequential circuits, state tables, state diagrams, state equations, and the design of counters using flip-flops. Key topics include the use of flip-flops as memory elements, master-slave configurations to prevent race-around conditions, and how to analyze and design sequential circuits and counters.PPT 2nd unit course file.ppt

PPT 2nd unit course file.pptSILAMBARASANAECEKIOT

Ã˝

This document provides an overview of sequential circuits. It defines sequential circuits as circuits whose outputs depend on current and past input values, unlike combinational circuits whose outputs only depend on current inputs. It describes the main types of sequential circuits as synchronous (controlled by a clock) and asynchronous. Common memory elements for sequential circuits called flip-flops are introduced, including SR, D, J-K, and T flip-flops. The use of state tables and state diagrams to analyze sequential circuits is covered. Procedures for reducing states, assigning binary codes to states, and designing sequential circuits using flip-flops are also outlined. An example of designing a circuit to detect three or more consecutive 1s in an input bit stringLec9

Lec9SouravRoyElectronics

Ã˝

This document discusses sequential circuits and their analysis and design. It begins by defining sequential circuits and their basic components like latches and flip-flops. It then covers analyzing synchronous sequential circuits using their output functions, state equations, and state tables. The document concludes by outlining the steps for designing a synchronous sequential circuit from its specification.Analysis sequential circuits

Analysis sequential circuitsG Subramaniamg

Ã˝

This document discusses sequential logic circuits and their analysis. It defines combinational and sequential logic, and synchronous and asynchronous circuits. There are two main types of sequential logic models - Moore and Mealy machines. Analysis of sequential circuits involves deriving their state tables and state diagrams from the circuit description. Examples show how to analyze circuits using D flip-flops, JK flip-flops, and a serial adder circuit. Multiple input state machines have state tables where the next state depends on all present inputs.SEQUENTIAL CIRCUITS -Module 5 (1).pptx

SEQUENTIAL CIRCUITS -Module 5 (1).pptxThanmayiKumar

Ã˝

This document provides an introduction to sequential circuits and various types of flip-flops. It discusses the differences between combinational and sequential circuits, and describes SR, D, JK, T, and JK flip-flops. Their block diagrams, truth tables, characteristic tables, and excitation tables are presented. Applications of flip-flops such as counters, frequency dividers, shift registers, and data storage are also covered briefly. Finally, the document discusses various types of shift registers including serial-in serial-out, serial-in parallel-out, parallel-in serial-out, and parallel-in parallel-out.Sequential Circuitsdddddddddddddddddsssssssssss-ppt.pptx

Sequential Circuitsdddddddddddddddddsssssssssss-ppt.pptxAhmedAlAfandi5

Ã˝

Digital circuits Electronics Digital circuits Electronics Digital circuits Electronics Digital circuits Electronics Digital circuits Electronics Digital circuits Electronics Digital circuits Electronics Digital circuits Electronics Digital circuits Electronics Digital circuits Electronics Digital circuits Electronics Digital circuits Electronics Digital circuits Electronics Digital circuits Electronics Digital circuits Electronics Digital circuits Electronics Digital circuits Electronics Digital circuits Electronics Digital circuits Electronics Digital circuits Electronics Digital circuits Electronics Digital circuits Electronics Digital circuits Electronics Digital circuits Electronics Digital circuits Electronics Digital circuits Electronics Digital circuits Electronics Digital circuits Electronics Digital circuits Electronics Digital circuits Electronics Digital circuits Electronics Digital circuits Electronics Digital circuits Electronics Digital circuits Electronics Digital circuits Electronics Digital circuits Electronics Digital circuits Electronics Digital circuits Electronics Digital circuits Electronics Digital circuits Electronics Digital circuits Electronics Digital circuits Electronics Digital circuits Electronics Digital circuits Electronics Digital circuits Electronics Digital circuits Electronics Digital circuits Electronics Digital circuits Electronics Digital circuits Electronics Digital circuits Electronics Digital circuits Electronics Digital circuits Electronics Digital circuits Electronics Digital circuits Electronics Digital circuits Electronics Digital circuits Electronics Digital circuits Electronics Digital circuits Electronics Digital circuits Electronics Digital circuits Electronics Digital circuits Electronics Digital circuits Electronics Digital circuits Electronics Digital circuits Electronics Digital circuits Electronics Digital circuits Electronics Digital circuits Electronics Digital circuits Electronics Digital circuits Electronics Digital circuits Electronics Digital circuits Electronics Digital circuits Electronics Digital circuits Electronics Digital circuits Electronics Digital circuits Electronics Digital circuits Electronics Digital circuits Electronics Digital circuits Electronics Digital circuits Electronics Digital circuits Electronics Digital circuits Electronics Digital circuits Electronics Digital circuits Electronics Digital circuits Electronics Digital circuits Electronics Digital circuits Electronics Digital circuits Electronics Digital circuits Electronics Digital circuits Electronics Digital circuits Electronics Digital circuits Electronics Digital circuits Electronics Digital circuits Electronics Digital circuits Electronics Digital circuits Electronics Digital circuits Electronics Digital circuits Electronics Digital circuits Electronics Digital circuits Electronics Digital circuits Electronics Digital circuits Electronics Digital circuits Electronics Digital circuits Electronics Digital circSequential Circuits-ppt_2.pdf

Sequential Circuits-ppt_2.pdfimadshaheen2

Ã˝

1. The document discusses sequential circuits and various types of latches and flip-flops used in sequential logic, including SR latches, D latches, edge-triggered flip-flops, JK flip-flops and T flip-flops.

2. It describes how to analyze sequential circuits using state tables, state equations, state diagrams and flip-flop input equations.

3. As an example, it shows the analysis of a 2-bit up counter sequential circuit using D flip-flops, including deriving the next state equations and constructing the state table and state diagram.Sequential Logic

Sequential LogicSchool of Design Engineering Fashion & Technology (DEFT), University of Wales, Newport

Ã˝

The following presentation is a part of the level 4 module -- Digital Logic and Signal Principles. This resources is a part of the 2009/2010 Engineering (foundation degree, BEng and HN) courses from University of Wales Newport (course codes H101, H691, H620, HH37 and 001H). This resource is a part of the core modules for the full time 1st year undergraduate programme.

The BEng & Foundation Degrees and HNC/D in Engineering are designed to meet the needs of employers by placing the emphasis on the theoretical, practical and vocational aspects of engineering within the workplace and beyond. Engineering is becoming more high profile, and therefore more in demand as a skill set, in today’s high-tech world. This course has been designed to provide you with knowledge, skills and practical experience encountered in everyday engineering environments. lec7.ppt

lec7.pptSalmanHameed26

Ã˝

This document summarizes a lecture on sequential networks and flip-flops. It discusses:

1) What defines a sequential circuit as one whose output depends on current inputs and past outputs, giving it memory.

2) The basic mechanisms of memory involve feedback loops using capacitive loads or inverters, allowing a circuit to store a bit through different states.

3) Common types of flip-flops like SR, D, JK, and T are described, along with their characteristic equations and how they can be used as basic memory components.

4) Sequential networks are implemented using finite state machines and excitation tables to specify and realize the desired sequential function. Proper timing is crucial to separate presentLecture 3

Lecture 3MunasarAbdirahman

Ã˝

This document summarizes sequential circuits and finite state machines. It discusses:

- Representing state using state equations, state tables, and state diagrams

- Analyzing sequential circuits using D, JK, and T flip-flops

- The difference between Mealy and Moore machines and examples of each

- Design procedures for state machines including state diagrams, next state tables, excitation tables, K-maps, and circuit implementationChapter 3

Chapter 3EasyStudy3

Ã˝

The document discusses sequential circuits and their components. It begins with an overview of sequential circuits and finite state machines. It then covers different types of flip-flops like D flip-flops and their usage. Counters and sequencers are presented as examples of sequential circuits. Details about designing a 3-bit up counter like its state table and logic equations are provided. Finally, registers are discussed including an example of a 4-bit register with parallel load.Lecture 12.pptx

Lecture 12.pptxTimePresents

Ã˝

The document describes building a finite state machine (FSM) combination lock with a reset button, two number buttons (0 and 1), and an unlock output, where the combination is 01011. It provides steps to design the lock FSM by creating a block diagram and state transition diagram, and then writing Verilog modules for the FSM. The document also provides examples of level-to-pulse converters and discusses Moore and Mealy FSMs.Lec16 Intro to Computer Engineering by Hsien-Hsin Sean Lee Georgia Tech -- Fi...

Lec16 Intro to Computer Engineering by Hsien-Hsin Sean Lee Georgia Tech -- Fi...Hsien-Hsin Sean Lee, Ph.D.

Ã˝

This document discusses finite state machines (FSMs) including Mealy and Moore machines. It provides examples of state diagrams for Mealy and Moore machines and describes how to design the logic circuits for an FSM from its state table. Key steps include generating Boolean functions for outputs and next states, simplifying the functions, and creating logic gates for the outputs, next state logic, and current state registers. An example of a vending machine FSM is also presented with its state diagram and logic circuit design.Sequential logic circuit

Sequential logic circuitAswiniT3

Ã˝

1) The document discusses sequential logic circuits and covers topics like latches, flip-flops, their analysis and modeling in hardware description languages.

2) It describes various types of latches and flip-flops like SR, D, JK, T flip-flops and compares their operations.

3) Guidelines are provided for designing synchronous sequential circuits which include deriving a state diagram and table, reducing states, assigning codes, deriving equations and drawing the logic diagram.Unit 4 sequential circuits

Unit 4 sequential circuitsAmrutaMehata

Ã˝

This document provides information about sequential logic circuits. It begins by defining sequential logic circuits as consisting of a combinational circuit with storage elements that provide feedback, causing the output to depend on the sequence of inputs. It describes the main types of sequential circuits as synchronous and asynchronous. It also discusses different types of storage elements including latches and flip-flops. Latches are level sensitive while flip-flops are edge triggered. Specific latch and flip-flop circuits like the SR latch, D latch, and JK flip-flop are described along with their operations.Lec16 Intro to Computer Engineering by Hsien-Hsin Sean Lee Georgia Tech -- Fi...

Lec16 Intro to Computer Engineering by Hsien-Hsin Sean Lee Georgia Tech -- Fi...Hsien-Hsin Sean Lee, Ph.D.

Ã˝

Recently uploaded (20)

How to Setup WhatsApp in Odoo 17 - Odoo ∫›∫›fl£s

How to Setup WhatsApp in Odoo 17 - Odoo ∫›∫›fl£sCeline George

Ã˝

Integrate WhatsApp into Odoo using the WhatsApp Business API or third-party modules to enhance communication. This integration enables automated messaging and customer interaction management within Odoo 17.N.C. DPI's 2023 Language Diversity Briefing

N.C. DPI's 2023 Language Diversity BriefingMebane Rash

Ã˝

The number of languages spoken in NC public schools.Useful environment methods in Odoo 18 - Odoo ∫›∫›fl£s

Useful environment methods in Odoo 18 - Odoo ∫›∫›fl£sCeline George

Ã˝

In this slide we’ll discuss on the useful environment methods in Odoo 18. In Odoo 18, environment methods play a crucial role in simplifying model interactions and enhancing data processing within the ORM framework.South Hornsey: The Lost Local Authority that Merged with Stoke Newington by T...

South Hornsey: The Lost Local Authority that Merged with Stoke Newington by T...History of Stoke Newington

Ã˝

Presented at the 24th Stoke Newington History Talks event on 27th Feb 2025

https://stokenewingtonhistory.com/stoke-newington-history-talks/FESTIVAL: SINULOG & THINGYAN-LESSON 4.pptx

FESTIVAL: SINULOG & THINGYAN-LESSON 4.pptxDanmarieMuli1

Ã˝

Sinulog Festival of Cebu City, and Thingyan Festival of Myanmar.QuickBooks Desktop to QuickBooks Online How to Make the Move

QuickBooks Desktop to QuickBooks Online How to Make the MoveTechSoup

Ã˝

If you use QuickBooks Desktop and are stressing about moving to QuickBooks Online, in this webinar, get your questions answered and learn tips and tricks to make the process easier for you.

Key Questions:

* When is the best time to make the shift to QuickBooks Online?

* Will my current version of QuickBooks Desktop stop working?

* I have a really old version of QuickBooks. What should I do?

* I run my payroll in QuickBooks Desktop now. How is that affected?

*Does it bring over all my historical data? Are there things that don't come over?

* What are the main differences between QuickBooks Desktop and QuickBooks Online?

* And moreAdventure Activities Final By H R Gohil Sir

Adventure Activities Final By H R Gohil SirGUJARATCOMMERCECOLLE

Ã˝

Adventure Activities Final By H R Gohil SirComputer Application in Business (commerce)

Computer Application in Business (commerce)Sudar Sudar

Ã˝

The main objectives

1. To introduce the concept of computer and its various parts. 2. To explain the concept of data base management system and Management information system.

3. To provide insight about networking and basics of internet

Recall various terms of computer and its part

Understand the meaning of software, operating system, programming language and its features

Comparing Data Vs Information and its management system Understanding about various concepts of management information system

Explain about networking and elements based on internet

1. Recall the various concepts relating to computer and its various parts

2 Understand the meaning of software’s, operating system etc

3 Understanding the meaning and utility of database management system

4 Evaluate the various aspects of management information system

5 Generating more ideas regarding the use of internet for business purpose Year 10 The Senior Phase Session 3 Term 1.pptx

Year 10 The Senior Phase Session 3 Term 1.pptxmansk2

Ã˝

Year 10 The Senior Phase Session 3 Term 1.pptxAPM People Interest Network Conference - Oliver Randall & David Bovis - Own Y...

APM People Interest Network Conference - Oliver Randall & David Bovis - Own Y...Association for Project Management

Ã˝

APM People Interest Network Conference 2025

- Autonomy, Teams and Tension

- Oliver Randall & David Bovis

- Own Your Autonomy

Oliver Randall

Consultant, Tribe365

Oliver is a career project professional since 2011 and started volunteering with APM in 2016 and has since chaired the People Interest Network and the North East Regional Network. Oliver has been consulting in culture, leadership and behaviours since 2019 and co-developed HPTM® an off the shelf high performance framework for teams and organisations and is currently working with SAS (Stellenbosch Academy for Sport) developing the culture, leadership and behaviours framework for future elite sportspeople whilst also holding down work as a project manager in the NHS at North Tees and Hartlepool Foundation Trust.

David Bovis

Consultant, Duxinaroe

A Leadership and Culture Change expert, David is the originator of BTFA‚Ñ¢ and The Dux Model.

With a Masters in Applied Neuroscience from the Institute of Organisational Neuroscience, he is widely regarded as the ‘Go-To’ expert in the field, recognised as an inspiring keynote speaker and change strategist.

He has an industrial engineering background, majoring in TPS / Lean. David worked his way up from his apprenticeship to earn his seat at the C-suite table. His career spans several industries, including Automotive, Aerospace, Defence, Space, Heavy Industries and Elec-Mech / polymer contract manufacture.

Published in London’s Evening Standard quarterly business supplement, James Caan’s ‘Your business’ Magazine, ‘Quality World’, the Lean Management Journal and Cambridge Universities ‘PMA’, he works as comfortably with leaders from FTSE and Fortune 100 companies as he does owner-managers in SME’s. He is passionate about helping leaders understand the neurological root cause of a high-performance culture and sustainable change, in business.

Session | Own Your Autonomy – The Importance of Autonomy in Project Management

#OwnYourAutonomy is aiming to be a global APM initiative to position everyone to take a more conscious role in their decision making process leading to increased outcomes for everyone and contribute to “a world in which all projects succeed”.

We want everyone to join the journey.

#OwnYourAutonomy is the culmination of 3 years of collaborative exploration within the Leadership Focus Group which is part of the APM People Interest Network. The work has been pulled together using the 5 HPTM® Systems and the BTFA neuroscience leadership programme.

https://www.linkedin.com/showcase/apm-people-network/about/Principle and Practices of Animal Breeding || Boby Basnet

Principle and Practices of Animal Breeding || Boby BasnetBoby Basnet

Ã˝

Principle and Practices of Animal Breeding Full Note

|| Assistant Professor Boby Basnet ||IAAS || AFU || PU || FUEng7-Q4-Lesson 1 Part 1 Understanding Discipline-Specific Words, Voice, and T...

Eng7-Q4-Lesson 1 Part 1 Understanding Discipline-Specific Words, Voice, and T...sandynavergas1

Ã˝

Understanding Discipline-Specific Words, Voice, and Technical TermsTLE 7 - 3rd Topic - Hand Tools, Power Tools, Instruments, and Equipment Used ...

TLE 7 - 3rd Topic - Hand Tools, Power Tools, Instruments, and Equipment Used ...RizaBedayo

Ã˝

Hand Tools, Power Tools, and Equipment in Industrial ArtsA PPT Presentation on The Princess and the God: A tale of ancient India by A...

A PPT Presentation on The Princess and the God: A tale of ancient India by A...Beena E S

Ã˝

A PPT Presentation on The Princess and the God: A tale of ancient India by Aaron ShepardSouth Hornsey: The Lost Local Authority that Merged with Stoke Newington by T...

South Hornsey: The Lost Local Authority that Merged with Stoke Newington by T...History of Stoke Newington

Ã˝

APM People Interest Network Conference - Oliver Randall & David Bovis - Own Y...

APM People Interest Network Conference - Oliver Randall & David Bovis - Own Y...Association for Project Management

Ã˝

Sequential circuits

- 1. Government Engineering college,Bhavnagar semester: 3 Branch: Computer (2015) Name:- Paresh Parmar subject: Digital Electronics Enrollment No: 140210107040 Topic: Sequential Circuits

- 2. Combinational Logic ÔÇó Combinational Logic: ÔÇó Output depends only on current input ÔÇó Has no memory 2016/11/8 22

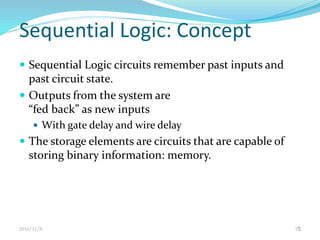

- 3. Sequential Logic ÔÇó Sequential Logic: ÔÇó Output depends not only on current input but also on past input values, e.g., design a counter ÔÇó Need some type of memory to remember the past input values 2016/11/8 33

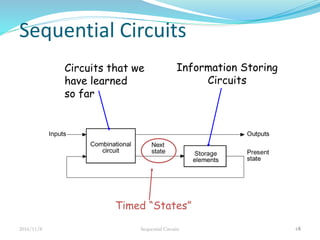

- 4. Sequential Circuits 2016/11/8 Sequential Circuits 44 Circuits that we have learned so far Information Storing Circuits Timed “States”

- 5. Sequential Logic: Concept  Sequential Logic circuits remember past inputs and past circuit state.  Outputs from the system are “fed back” as new inputs  With gate delay and wire delay  The storage elements are circuits that are capable of storing binary information: memory. 2016/11/8 55

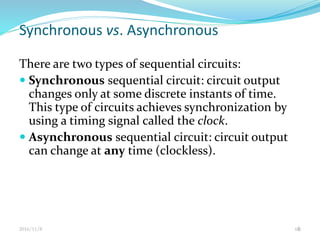

- 6. Synchronous vs. Asynchronous There are two types of sequential circuits: ÔÇó Synchronous sequential circuit: circuit output changes only at some discrete instants of time. This type of circuits achieves synchronization by using a timing signal called the clock. ÔÇó Asynchronous sequential circuit: circuit output can change at any time (clockless). 2016/11/8 66

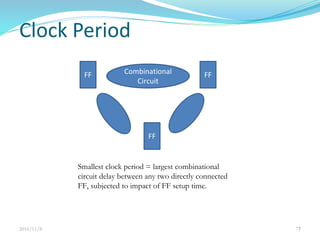

- 7. Clock Period 2016/11/8 77 FF FFCombinational Circuit Smallest clock period = largest combinational circuit delay between any two directly connected FF, subjected to impact of FF setup time. FF

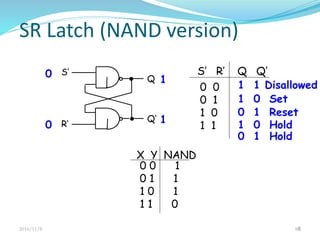

- 8. SR Latch (NAND version) 2016/11/8 88 S’ R’ Q Q’ 0 0 0 1 1 0 1 1 S’ R’ Q Q’0 0 1 1 0 0 1 0 1 1 1 0 1 1 1 0 X Y NAND 0 1 Hold 1 0 Set 0 1 Reset 1 0 Hold 1 1 Disallowed

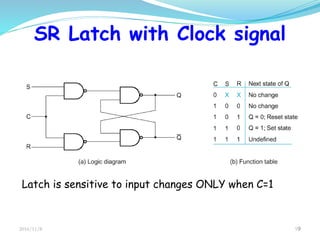

- 9. 2016/11/8 99 SR Latch with Clock signal Latch is sensitive to input changes ONLY when C=1

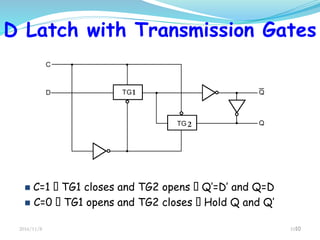

- 10. 2016/11/8 1010 D Latch with Transmission Gates  C=1 TG1 closes and TG2 opens Q’=D’ and Q=D  C=0 TG1 opens and TG2 closes Hold Q and Q’ 2 1

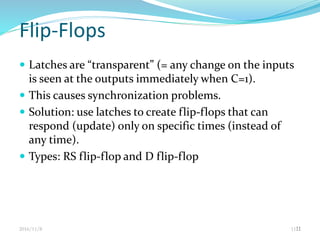

- 11. Flip-Flops  Latches are “transparent” (= any change on the inputs is seen at the outputs immediately when C=1).  This causes synchronization problems.  Solution: use latches to create flip-flops that can respond (update) only on specific times (instead of any time).  Types: RS flip-flop and D flip-flop 2016/11/8 1111

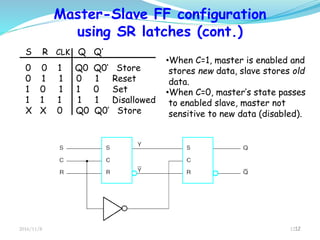

- 12. 2016/11/8 1212 S R CLK Q Q’ 0 0 1 Q0 Q0’ Store 0 1 1 0 1 Reset 1 0 1 1 0 Set 1 1 1 1 1 Disallowed X X 0 Q0 Q0’ Store Master-Slave FF configuration using SR latches (cont.) •When C=1, master is enabled and stores new data, slave stores old data. •When C=0, master’s state passes to enabled slave, master not sensitive to new data (disabled).

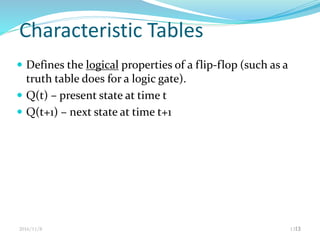

- 13. Characteristic Tables  Defines the logical properties of a flip-flop (such as a truth table does for a logic gate).  Q(t) – present state at time t  Q(t+1) – next state at time t+1 2016/11/8 1313

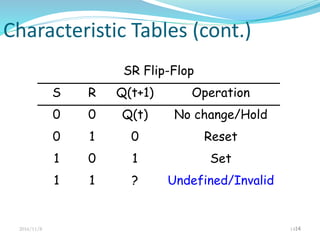

- 14. Characteristic Tables (cont.) SR Flip-Flop S R Q(t+1) Operation 0 0 Q(t) No change/Hold 0 1 0 Reset 1 0 1 Set 1 1 ? Undefined/Invalid 2016/11/8 1414

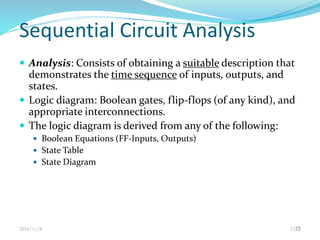

- 15. Sequential Circuit Analysis ÔÇó Analysis: Consists of obtaining a suitable description that demonstrates the time sequence of inputs, outputs, and states. ÔÇó Logic diagram: Boolean gates, flip-flops (of any kind), and appropriate interconnections. ÔÇó The logic diagram is derived from any of the following: ÔÇó Boolean Equations (FF-Inputs, Outputs) ÔÇó State Table ÔÇó State Diagram 2016/11/8 1515

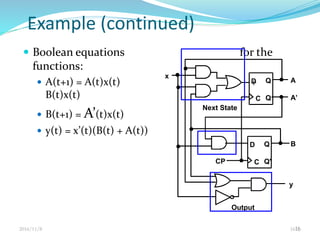

- 16. Example (continued)  Boolean equations for the functions:  A(t+1) = A(t)x(t) + B(t)x(t)  B(t+1) = A’(t)x(t)  y(t) = x’(t)(B(t) + A(t)) 2016/11/8 1616 C D Q Q C D Q Q' y x A A’ B CP Next State Output

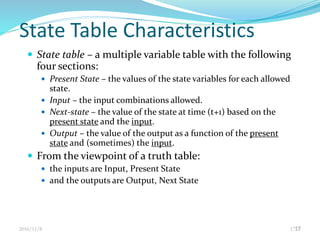

- 17. State Table Characteristics  State table – a multiple variable table with the following four sections:  Present State – the values of the state variables for each allowed state.  Input – the input combinations allowed.  Next-state – the value of the state at time (t+1) based on the present state and the input.  Output – the value of the output as a function of the present state and (sometimes) the input.  From the viewpoint of a truth table:  the inputs are Input, Present State  and the outputs are Output, Next State 2016/11/8 1717

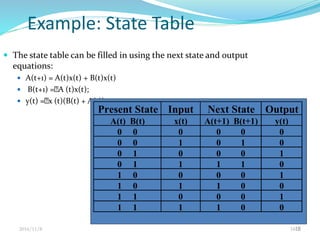

- 18. Example: State Table ÔÇó The state table can be filled in using the next state and output equations: ÔÇó A(t+1) = A(t)x(t) + B(t)x(t) ÔÇó B(t+1) = A (t)x(t); ÔÇó y(t) = x (t)(B(t) + A(t)) 2016/11/8 1818 Present State Input Next State Output A(t) B(t) x(t) A(t+1) B(t+1) y(t) 0 0 0 0 0 0 0 0 1 0 1 0 0 1 0 0 0 1 0 1 1 1 1 0 1 0 0 0 0 1 1 0 1 1 0 0 1 1 0 0 0 1 1 1 1 1 0 0

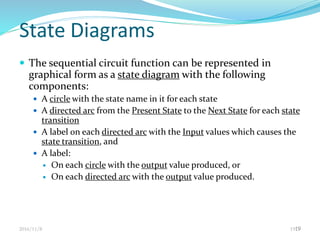

- 19. State Diagrams ÔÇó The sequential circuit function can be represented in graphical form as a state diagram with the following components: ÔÇó A circle with the state name in it for each state ÔÇó A directed arc from the Present State to the Next State for each state transition ÔÇó A label on each directed arc with the Input values which causes the state transition, and ÔÇó A label: ÔÇó On each circle with the output value produced, or ÔÇó On each directed arc with the output value produced. 2016/11/8 1919

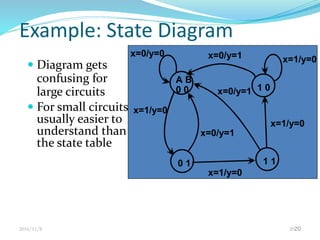

- 20. Example: State Diagram ÔÇó Diagram gets confusing for large circuits ÔÇó For small circuits, usually easier to understand than the state table 2016/11/8 2020 A B 0 0 0 1 1 1 1 0 x=0/y=1 x=1/y=0 x=1/y=0 x=1/y=0 x=0/y=1 x=0/y=1 x=1/y=0 x=0/y=0

- 21. Summary ÔÇó Sequential circuit timing analysis ÔÇó Flip-Flop ÔÇó Transmission gate based flip-flop design ÔÇó Setup time 2016/11/8 2121