Synchronous counters

Download as PPTX, PDF12 likes16,128 views

This document describes different types of synchronous counters that are triggered by a common clock signal. It discusses binary counters that count up in binary, up-down binary counters that can count up or down, BCD counters that count in decimal, and binary counters that can be parallel loaded. The key aspects covered are how the flip-flops are triggered in each counter type and the inputs and functions that control counting direction, clearing, loading, and counting.

1 of 8

Downloaded 693 times

Recommended

Counters

CountersAbhilash Nair

Ėý

This document provides information about different types of counters, including asynchronous counters, synchronous counters, MSI counters, and specific counter integrated circuits. It defines counters and describes their basic characteristics. It discusses asynchronous ripple counters and their timing. It provides examples of decade and binary counters. It describes synchronous counters and MSI counters like the 74LS163 4-bit synchronous counter. Finally, it provides truth tables, logic diagrams, and application information for common counter ICs like the 7490, 7492, 7493, and 74LS163.Synchronous Counter

Synchronous Counter Akhilesh Kushwaha

Ėý

What is synchronous

A four-bit synchronous âUPâ counter

A four-bit synchronous âdownâ counter

How to design synchronous counterRipple counter

Ripple counterchandkec

Ėý

This document discusses ripple counters and their characteristics:

- Ripple counters have a modulus (MOD) which is the number of states the counter cycles through before repeating. The MOD is equal to 2n where n is the number of flip-flops.

- State transition diagrams graphically represent the sequence of states a counter goes through with each clock pulse.

- Common integrated circuits used for ripple counters include the 74LS90, 74LS92, 74LS93 and 74HC390. The 74LS93 and 74HC390 can be configured to count to different MODs by controlling enable inputs.

- The internal logic of the 74LS93 is shown, with the clock pulse applied todigital Counter

digital Countershamshad alam

Ėý

This document discusses counters, which are digital circuits used for counting pulses. It describes asynchronous and synchronous counters, and different types including up/down counters, decade counters, ring counters, and Johnson counters. Examples of counter applications are given such as in kitchen appliances, washing machines, microwaves, and programmable logic controllers. Counters are used for tasks like time measurement, frequency division, and digital signal generation.Shift Registers

Shift RegistersAbhilash Nair

Ėý

Shift registers are digital circuits composed of flip-flops that can shift data from one stage to the next. They can be configured for serial-in serial-out, serial-in parallel-out, parallel-in serial-out, or parallel-in parallel-out data movement. Common applications include converting between serial and parallel data, temporary data storage, and implementing counters. MSI shift registers like the 74LS164 and 74LS166 provide 8-bit shift register functionality.Register in Digital Logic

Register in Digital LogicISMT College

Ėý

A register is a group of flip-flops that can store multiple bits of data. There are four types of shift registers: serial-in serial-out (SISO), serial-in parallel-out (SIPO), parallel-in serial-out (PISO), and parallel-in parallel-out (PIPO). Shift registers allow data to move between flip-flops on each clock pulse. Ring counters and Johnson counters are examples of shift register counters that produce repeating output sequences.Introduction to Counters

Introduction to CountersISMT College

Ėý

The document discusses synchronous and asynchronous counters. It defines a counter as a digital circuit that counts input pulses. Asynchronous counters have flip-flops that change state at different times since they do not share a common clock. Synchronous counters have all flip-flops change simultaneously due to a shared global clock, allowing them to operate at higher frequencies. The document provides examples of 2-bit, 3-bit, and 4-bit synchronous binary counters as well as a 4-bit synchronous decade counter along with their operations and timing diagrams. multiplexers and demultiplexers

multiplexers and demultiplexersUnsa Shakir

Ėý

This document discusses multiplexers and demultiplexers. It defines them as devices that allow digital information from several sources to be routed onto a single line (multiplexers) or distributed to multiple output lines (demultiplexers). The key properties of multiplexers and demultiplexers are described, including the relationship between the number of inputs, outputs, and selection lines. Examples of implementing multiplexers and demultiplexers using logic gates are provided.Johnson counter

Johnson counterMuhammad Anas Sabir

Ėý

A binary counter uses multiple flip-flops depending on the number of bits required. There are two types of counters: synchronous uses a common clock for all flip-flops while asynchronous only clocks the first stage. A twisted ring or Johnson counter is similar to a ring counter but inverts the output of the last stage and feeds it back to the first stage input. This creates a pattern that is twice the length of the shift register and circulates indefinitely. Twisted ring counters are used in applications like walking LED displays and converting square waves to sine waves.Digital Electronics - Counters

Digital Electronics - CountersJayakrishnan J

Ėý

This document discusses counters in digital electronics. It begins by introducing counters as sequential circuits that increment their output value by one each clock cycle, wrapping back to 0 after their maximum count. There are two main types of counters: asynchronous and synchronous. Asynchronous counters have their flip-flops clocked one after another by the previous flip-flop's output, causing a ripple effect. Synchronous counters clock all flip-flops simultaneously with a common clock signal. Examples of 4-bit asynchronous and synchronous counters are also provided with their respective timing diagrams.Ring counter

Ring counterGhufran Hasan

Ėý

A ring counter is a type of shift register where the output of the last flip-flop is connected back to the input of the first flip-flop, creating a circular shift of bits. When a clock signal is applied, the single '1' bit circulates from one stage to the next in a continuous loop. Ring counters are commonly used as frequency dividers and to generate quadrature signals with multiple phases. Their applications include data counting, pattern detection, and producing square waves for timing signals.Counters

CountersKetaki_Pattani

Ėý

This document discusses different types of counters used in digital circuits. It defines a counter as a sequential circuit that cycles through a sequence of states in response to clock pulses. Binary counters count in binary and can count from 0 to 2n-1 with n flip-flops. Asynchronous counters have flip-flops that are not triggered simultaneously by a clock, while synchronous counters use a common clock for all flip-flops. Other counter types include ring counters, Johnson counters, and decade counters. The document provides examples of binary, asynchronous, and synchronous counters and discusses their applications in areas like timing sequences and addressing memory.Counters

CountersRevathi Subramaniam

Ėý

Counters ,its types, modulo counters, design of synchronous and asynchronous counters are given a detailed viewCounters

CountersRandaqra

Ėý

A presentation about counters, for electronics for scientists course.

Physics department

Birzeit university . Registers and counters

Registers and counters Deepak John

Ėý

Registers are groups of flip-flops that store binary data. An n-bit register contains n flip-flops and can store 2^n different states. Registers are used to store and provide digital data to logic circuits. There are different types of registers including shift registers. Shift registers can transfer data in serial-in serial-out, serial-in parallel-out, parallel-in serial-out, and parallel-in parallel-out modes. Counters are registers that increment their stored value on each clock pulse and are used to count events.Basics Counters

Basics Counters Danial Mirza

Ėý

This document discusses different types of counters, including asynchronous and synchronous counters. Asynchronous counters use flip-flops that are not connected to a common clock, resulting in a "ripple" effect. Synchronous counters connect all flip-flops to the same clock and use combinational logic to generate the next state. Counters can be cascaded to achieve higher modulus by connecting the output of one counter to the input of the next. The document also provides an example of designing a synchronous BCD counter and cascading a mod-10 and mod-8 counter.sequential circuits

sequential circuitsUnsa Shakir

Ėý

Sequential circuits have outputs determined by both the current inputs and previous outputs due to the inclusion of memory elements. Combinational circuits only have outputs determined by the current inputs. Sequential circuits contain logic gates arranged in parallel and feedback loops allowing the circuit to store past states, while combinational circuits only depend on the current input combination. There are different types of sequential circuits including those controlled by a clock signal from a clock generator that produces periodic pulses defining the circuit timing.Digital Electronics - Counters

Digital Electronics - CountersJayakrishnanJ11

Ėý

This document discusses counters in digital electronics. It begins by introducing counters as sequential circuits that increment their output value by one each clock cycle, wrapping back to 0 after their maximum count. There are two main types of counters: asynchronous and synchronous. Asynchronous counters have their flip-flops clocked one after another by the previous flip-flop's output, causing a ripple effect. Synchronous counters clock all flip-flops simultaneously using a common clock signal. Examples of 4-bit asynchronous and synchronous counters are also provided with their respective timing diagrams.Latches and flip flop

Latches and flip flopShuaib Hotak

Ėý

This document discusses latches and flip flops, which are types of sequential logic circuits. It describes the basic components and functioning of latches like SR latches, D latches, and gated latches. For flip flops, it covers SR flip flops, D flip flops, JK flip flops, and master-slave flip flops. The key differences between latches and flip flops are that latches do not have a clock input while flip flops are edge-triggered by a clock signal. Latches and flip flops are used as basic storage elements in more complex sequential circuits and in computer components like registers and RAM.Encoder

EncoderMahmudul Hasan

Ėý

This presentation introduces encoders. It discusses that an encoder is a combinational circuit that performs the reverse operation of a decoder, with a maximum of 2n inputs and n outputs. The simplest encoder is a 2n-to-n binary encoder, where one of the 2n inputs is 1 and the output is an n-bit binary number representing the activated input. An example of an 8-to-3 binary encoder is shown, where only one of the 8 inputs can be activated at a time, and the 3 outputs represent the activated input in binary code.Johnson Counter

Johnson CounterJatinder Kumar Chaurasia

Ėý

This document discusses Johnson counters, which are a modification of ring counters. In a Johnson counter, the output from the last flip-flop is inverted and fed back to the input of the first flip-flop, rather than directly connecting the last output to the first input as in a ring counter. This allows a Johnson counter to use half as many flip-flops as a standard ring counter of the same modulus. The document provides the circuit diagram, truth table, and timing diagram of a 4-bit Johnson counter, and lists some example uses and components needed to build a 4-bit Johnson counter.Encoder and decoder

Encoder and decoderThen Murugeshwari

Ėý

Encoders convert decimal input to binary coded decimal (BCD) output, while decoders convert BCD input to decimal output displayed on a 7-segment display. An example encoder converts decimal numbers to their BCD coded form, while an example decoder converts BCD codes into the decimal numbers they represent, which are then shown on a 7-segment LED display. The document provides examples of encodings and decoding between decimal, BCD, and 7-segment display representations and tests the reader with questions about decoding BCD inputs.Flag register 8086 assignment

Flag register 8086 assignmentZia3130

Ėý

The flag register in the 8086 CPU contains 16 bits with each bit corresponding to a flip-flop that indicates the status of instructions. There are 9 active flags that serve different purposes - 6 are status flags reflecting results and 3 are control flags that enable/disable operations. The status flags indicate things like carry, parity, zero, sign, overflow while the control flags control tracing mode, interrupts, and direction of string operations.Code conversion

Code conversionAlapan Banerjee

Ėý

CODE CONVERSION IS A VERY USEFUL TOPIC IN DIGITAL ELECTRONIC. THIS PRESENTATION WILL HELP TO CLEAR THE CONCEPT OF ALL TYPES OF CODE CONVERSIONS. Registers and counters

Registers and countersHeman Pathak

Ėý

1. The document discusses different types of registers, counters, and shift registers including their components, functions, and loading/shifting processes.

2. It also covers synchronous and asynchronous counters as well as ring and Johnson counters.

3. Finally, it discusses integrated circuits and different digital logic families including TTL, ECL, MOS, CMOS, and I2L.Sequential Logic Circuit

Sequential Logic CircuitRamasubbu .P

Ėý

Sequential circuits consist of combinational logic and memory elements like latches and flip-flops. There are different types of latches and flip-flops that differ in their trigger mechanisms and outputs, including SR latches, D latches, and edge-triggered flip-flops like SR, D, and JK flip-flops. Asynchronous inputs can directly set or reset flip-flop outputs independent of the clock signal.(D/A) and (A/D)conversion

(D/A) and (A/D)conversionPraveen Kumar

Ėý

Digital to Analog(D/A) conversion, Binary Weighted Resistor method, Analog to Digital conversion,Successive Approximation method

Sequential circuits

Sequential circuitsParesh Parmar

Ėý

This document discusses sequential circuits and their analysis. It defines sequential logic as circuits whose outputs depend not only on current inputs but also past inputs, requiring some type of memory. There are two types of sequential circuits: synchronous use a clock for synchronization, while asynchronous can change output at any time. Analysis of sequential circuits involves obtaining a description of the input-output-state sequence over time using techniques like logic diagrams, state tables, characteristic tables, and state diagrams. Various flip-flop designs are presented, including the SR latch, D latch using transmission gates, and master-slave flip-flop. Timing considerations like clock period and setup time are also covered.Synschronous counter

Synschronous counterHassan Sardar

Ėý

This document discusses different types of synchronous counters. It describes synchronous counters as counters where clock pulses are applied simultaneously to all flip-flops. A 2-bit and 4-bit synchronous counter example is provided. The document also discusses BCD counters, which count in decimal from 0-9 and then reset to 0, and ring counters where the output of each flip-flop is connected to the input of the next in a loop.B sc cs i bo-de u-iii counters & registers

B sc cs i bo-de u-iii counters & registersRai University

Ėý

The document discusses registers and counters in digital circuits. It explains that counters are used for timing, sequencing, and counting applications. There are two main types of counters: ripple counters where each flip-flop triggers the next in sequence, and synchronous counters where all flip-flops are triggered simultaneously by a common clock. Binary ripple and synchronous 4-bit counters are described in detail through diagrams and explanations of their working principles. Parallel versus serial data transmission is also briefly discussed.More Related Content

What's hot (20)

Johnson counter

Johnson counterMuhammad Anas Sabir

Ėý

A binary counter uses multiple flip-flops depending on the number of bits required. There are two types of counters: synchronous uses a common clock for all flip-flops while asynchronous only clocks the first stage. A twisted ring or Johnson counter is similar to a ring counter but inverts the output of the last stage and feeds it back to the first stage input. This creates a pattern that is twice the length of the shift register and circulates indefinitely. Twisted ring counters are used in applications like walking LED displays and converting square waves to sine waves.Digital Electronics - Counters

Digital Electronics - CountersJayakrishnan J

Ėý

This document discusses counters in digital electronics. It begins by introducing counters as sequential circuits that increment their output value by one each clock cycle, wrapping back to 0 after their maximum count. There are two main types of counters: asynchronous and synchronous. Asynchronous counters have their flip-flops clocked one after another by the previous flip-flop's output, causing a ripple effect. Synchronous counters clock all flip-flops simultaneously with a common clock signal. Examples of 4-bit asynchronous and synchronous counters are also provided with their respective timing diagrams.Ring counter

Ring counterGhufran Hasan

Ėý

A ring counter is a type of shift register where the output of the last flip-flop is connected back to the input of the first flip-flop, creating a circular shift of bits. When a clock signal is applied, the single '1' bit circulates from one stage to the next in a continuous loop. Ring counters are commonly used as frequency dividers and to generate quadrature signals with multiple phases. Their applications include data counting, pattern detection, and producing square waves for timing signals.Counters

CountersKetaki_Pattani

Ėý

This document discusses different types of counters used in digital circuits. It defines a counter as a sequential circuit that cycles through a sequence of states in response to clock pulses. Binary counters count in binary and can count from 0 to 2n-1 with n flip-flops. Asynchronous counters have flip-flops that are not triggered simultaneously by a clock, while synchronous counters use a common clock for all flip-flops. Other counter types include ring counters, Johnson counters, and decade counters. The document provides examples of binary, asynchronous, and synchronous counters and discusses their applications in areas like timing sequences and addressing memory.Counters

CountersRevathi Subramaniam

Ėý

Counters ,its types, modulo counters, design of synchronous and asynchronous counters are given a detailed viewCounters

CountersRandaqra

Ėý

A presentation about counters, for electronics for scientists course.

Physics department

Birzeit university . Registers and counters

Registers and counters Deepak John

Ėý

Registers are groups of flip-flops that store binary data. An n-bit register contains n flip-flops and can store 2^n different states. Registers are used to store and provide digital data to logic circuits. There are different types of registers including shift registers. Shift registers can transfer data in serial-in serial-out, serial-in parallel-out, parallel-in serial-out, and parallel-in parallel-out modes. Counters are registers that increment their stored value on each clock pulse and are used to count events.Basics Counters

Basics Counters Danial Mirza

Ėý

This document discusses different types of counters, including asynchronous and synchronous counters. Asynchronous counters use flip-flops that are not connected to a common clock, resulting in a "ripple" effect. Synchronous counters connect all flip-flops to the same clock and use combinational logic to generate the next state. Counters can be cascaded to achieve higher modulus by connecting the output of one counter to the input of the next. The document also provides an example of designing a synchronous BCD counter and cascading a mod-10 and mod-8 counter.sequential circuits

sequential circuitsUnsa Shakir

Ėý

Sequential circuits have outputs determined by both the current inputs and previous outputs due to the inclusion of memory elements. Combinational circuits only have outputs determined by the current inputs. Sequential circuits contain logic gates arranged in parallel and feedback loops allowing the circuit to store past states, while combinational circuits only depend on the current input combination. There are different types of sequential circuits including those controlled by a clock signal from a clock generator that produces periodic pulses defining the circuit timing.Digital Electronics - Counters

Digital Electronics - CountersJayakrishnanJ11

Ėý

This document discusses counters in digital electronics. It begins by introducing counters as sequential circuits that increment their output value by one each clock cycle, wrapping back to 0 after their maximum count. There are two main types of counters: asynchronous and synchronous. Asynchronous counters have their flip-flops clocked one after another by the previous flip-flop's output, causing a ripple effect. Synchronous counters clock all flip-flops simultaneously using a common clock signal. Examples of 4-bit asynchronous and synchronous counters are also provided with their respective timing diagrams.Latches and flip flop

Latches and flip flopShuaib Hotak

Ėý

This document discusses latches and flip flops, which are types of sequential logic circuits. It describes the basic components and functioning of latches like SR latches, D latches, and gated latches. For flip flops, it covers SR flip flops, D flip flops, JK flip flops, and master-slave flip flops. The key differences between latches and flip flops are that latches do not have a clock input while flip flops are edge-triggered by a clock signal. Latches and flip flops are used as basic storage elements in more complex sequential circuits and in computer components like registers and RAM.Encoder

EncoderMahmudul Hasan

Ėý

This presentation introduces encoders. It discusses that an encoder is a combinational circuit that performs the reverse operation of a decoder, with a maximum of 2n inputs and n outputs. The simplest encoder is a 2n-to-n binary encoder, where one of the 2n inputs is 1 and the output is an n-bit binary number representing the activated input. An example of an 8-to-3 binary encoder is shown, where only one of the 8 inputs can be activated at a time, and the 3 outputs represent the activated input in binary code.Johnson Counter

Johnson CounterJatinder Kumar Chaurasia

Ėý

This document discusses Johnson counters, which are a modification of ring counters. In a Johnson counter, the output from the last flip-flop is inverted and fed back to the input of the first flip-flop, rather than directly connecting the last output to the first input as in a ring counter. This allows a Johnson counter to use half as many flip-flops as a standard ring counter of the same modulus. The document provides the circuit diagram, truth table, and timing diagram of a 4-bit Johnson counter, and lists some example uses and components needed to build a 4-bit Johnson counter.Encoder and decoder

Encoder and decoderThen Murugeshwari

Ėý

Encoders convert decimal input to binary coded decimal (BCD) output, while decoders convert BCD input to decimal output displayed on a 7-segment display. An example encoder converts decimal numbers to their BCD coded form, while an example decoder converts BCD codes into the decimal numbers they represent, which are then shown on a 7-segment LED display. The document provides examples of encodings and decoding between decimal, BCD, and 7-segment display representations and tests the reader with questions about decoding BCD inputs.Flag register 8086 assignment

Flag register 8086 assignmentZia3130

Ėý

The flag register in the 8086 CPU contains 16 bits with each bit corresponding to a flip-flop that indicates the status of instructions. There are 9 active flags that serve different purposes - 6 are status flags reflecting results and 3 are control flags that enable/disable operations. The status flags indicate things like carry, parity, zero, sign, overflow while the control flags control tracing mode, interrupts, and direction of string operations.Code conversion

Code conversionAlapan Banerjee

Ėý

CODE CONVERSION IS A VERY USEFUL TOPIC IN DIGITAL ELECTRONIC. THIS PRESENTATION WILL HELP TO CLEAR THE CONCEPT OF ALL TYPES OF CODE CONVERSIONS. Registers and counters

Registers and countersHeman Pathak

Ėý

1. The document discusses different types of registers, counters, and shift registers including their components, functions, and loading/shifting processes.

2. It also covers synchronous and asynchronous counters as well as ring and Johnson counters.

3. Finally, it discusses integrated circuits and different digital logic families including TTL, ECL, MOS, CMOS, and I2L.Sequential Logic Circuit

Sequential Logic CircuitRamasubbu .P

Ėý

Sequential circuits consist of combinational logic and memory elements like latches and flip-flops. There are different types of latches and flip-flops that differ in their trigger mechanisms and outputs, including SR latches, D latches, and edge-triggered flip-flops like SR, D, and JK flip-flops. Asynchronous inputs can directly set or reset flip-flop outputs independent of the clock signal.(D/A) and (A/D)conversion

(D/A) and (A/D)conversionPraveen Kumar

Ėý

Digital to Analog(D/A) conversion, Binary Weighted Resistor method, Analog to Digital conversion,Successive Approximation method

Sequential circuits

Sequential circuitsParesh Parmar

Ėý

This document discusses sequential circuits and their analysis. It defines sequential logic as circuits whose outputs depend not only on current inputs but also past inputs, requiring some type of memory. There are two types of sequential circuits: synchronous use a clock for synchronization, while asynchronous can change output at any time. Analysis of sequential circuits involves obtaining a description of the input-output-state sequence over time using techniques like logic diagrams, state tables, characteristic tables, and state diagrams. Various flip-flop designs are presented, including the SR latch, D latch using transmission gates, and master-slave flip-flop. Timing considerations like clock period and setup time are also covered.Similar to Synchronous counters (20)

Synschronous counter

Synschronous counterHassan Sardar

Ėý

This document discusses different types of synchronous counters. It describes synchronous counters as counters where clock pulses are applied simultaneously to all flip-flops. A 2-bit and 4-bit synchronous counter example is provided. The document also discusses BCD counters, which count in decimal from 0-9 and then reset to 0, and ring counters where the output of each flip-flop is connected to the input of the next in a loop.B sc cs i bo-de u-iii counters & registers

B sc cs i bo-de u-iii counters & registersRai University

Ėý

The document discusses registers and counters in digital circuits. It explains that counters are used for timing, sequencing, and counting applications. There are two main types of counters: ripple counters where each flip-flop triggers the next in sequence, and synchronous counters where all flip-flops are triggered simultaneously by a common clock. Binary ripple and synchronous 4-bit counters are described in detail through diagrams and explanations of their working principles. Parallel versus serial data transmission is also briefly discussed.COMBINATIONAL CIRCUITS & FLIP FLOPS

COMBINATIONAL CIRCUITS & FLIP FLOPSStarlee Lathong

Ėý

Combinational circuits are arrangements of logic gates with inputs and outputs. Flip-flops can store one bit and have two outputs, one for the stored value and its complement. Common types of flip-flops include SR, D, JK, and T flip-flops. SR flip-flops set or reset their output based on S and R inputs, while D flip-flops set their output based on the D input. Edge-triggered flip-flops change state on either the rising or falling edge of a clock signal.Synchronous Sequential Logic Unit 4

Synchronous Sequential Logic Unit 4Asif Iqbal

Ėý

These slides contain the basic of sequential logic, and includes a detailed and animated description of Flip-Flop and latches, it includes shift registers and counters also. It covers the fourth unit of Digital Logic DesignChapter 7_Counters (EEEg4302).pdf

Chapter 7_Counters (EEEg4302).pdfTamiratDejene1

Ėý

Digital Logic Design (EEEg4302)

Chapter 7 : Counters

This chapter discusses different types of counters, including asynchronous (ripple) counters and synchronous counters. Asynchronous counters use a ripple effect where one flip-flop triggers the next. Synchronous counters use a common clock signal to trigger all flip-flops simultaneously. The chapter also covers up/down counters, which can count up or down based on control signals, and methods for designing synchronous counters through state diagrams and logic expressions.DLD4.pdf

DLD4.pdfShashi738182

Ėý

- A MOS capacitor consists of a metal gate separated from a semiconductor substrate by an insulating layer (oxide). The oxide layer acts as a dielectric, allowing the structure to function as a capacitor.

- An nMOS transistor uses an n-type semiconductor substrate and contains an embedded n-channel. A pMOS transistor uses a p-type substrate and contains an embedded p-channel.

- In a CMOS structure, both nMOS and pMOS transistors are used together. It uses both p-type and n-type substrates which allows for low power consumption and high noise immunity.Multiplication algorithm

Multiplication algorithmGaurav Subham

Ėý

Booth's multiplication algorithm multiplies two signed binary numbers in two's complement notation. It was invented by Andrew Donald Booth in 1950. The algorithm inspects two bits of the multiplier at a time, and either adds, subtracts, or leaves unchanged the partial product depending on whether the bits are 10, 01, or the same. It shifts the partial product and multiplier arithmeticly to the right after each step to inspect the next bits.Digital Electronics Registers and Counters.pptx

Digital Electronics Registers and Counters.pptxnavaneethakrishnanec

Ėý

This document discusses various types of registers and counters used in combinational logic design. It describes parallel and serial registers, shift registers, and different methods for implementing counters including asynchronous ripple counters and synchronous counters. Specific examples are provided of 4-bit registers with parallel load and clear functionality. Modulo counters are also described that use binary counters with clear or parallel load to reset the count at the terminal value.Sequential Circuit

Sequential CircuitHeman Pathak

Ėý

This document discusses various types of flip-flops including RS, D, JK, T flip-flops. It describes their characteristic tables and excitation tables. It also covers sequential circuits, state tables, state diagrams, state equations, and the design of counters using flip-flops. Key topics include the use of flip-flops as memory elements, master-slave configurations to prevent race-around conditions, and how to analyze and design sequential circuits and counters.15CS32 ADE Module 4

15CS32 ADE Module 4RLJIT

Ėý

This document discusses various topics related to flip-flops and shift registers including:

1. Flip-flop timing parameters like setup time, hold time, and propagation delay.

2. The JK master-slave flip-flop configuration which uses two flip-flops to avoid unwanted state changes.

3. Switch contact bounce and how an RS latch can be used in a de-bounce circuit.

4. Different representations of flip-flops like truth tables, characteristic tables, and state diagrams.

5. HDL implementations of different types of flip-flops.

6. Shift register types like serial-in serial-out, serial-in parallel-out, parallel-in serial-Sequential circuits Sequential circuits1

Sequential circuits Sequential circuits1ssuser6feece1

Ėý

Sequential circuits are digital circuits that store and use the previous state information to determine their next state. Unlike combinational circuits, which only depend on the current inputCounter

CounterNaufal Qodari

Ėý

Counters are digital circuits that increment or decrement a stored value in response to a clock or trigger signal. There are two main types: ripple counters where the output of one flip-flop triggers the next, causing a ripple effect; and synchronous counters where all flip-flops change simultaneously according to a clock. Counters are widely used in computers and devices like clocks to keep track of events.Registers and Counters.ppt

Registers and Counters.pptVijay Bhadouria

Ėý

1. A register is a group of flip-flops that can store binary data either in parallel or serially.

2. A 4-bit register is constructed with four D-type flip-flops that store data on the rising edge of a clock signal and have an asynchronous reset input.

3. Parallel registers allow all bits to be loaded simultaneously by a common clock pulse, while serial registers transfer data one bit at a time during shifting.Sequential circuits

Sequential circuitsDrSonali Vyas

Ėý

The document discusses sequential circuits and different types of flip flops and counters. It describes how sequential circuits have memory and their output depends on current and past inputs. There are two main types of sequential circuits - asynchronous which can change state at any time and synchronous which use a clock signal to control when the output can change state. Common types of flip flops described include SR, JK, D and T flip flops. Counters can be asynchronous with the clock signal rippling through or synchronous where all flip flops share the same clock.Sequential circuits in Digital Electronics

Sequential circuits in Digital ElectronicsVinoth Loganathan

Ėý

The document explains about the concepts of sequential circuits in Digital electronics.

This will be helpful for the beginners in VLSI and electronics students.dsd-II-unit-III-registers-counters (1).pptx

dsd-II-unit-III-registers-counters (1).pptxssuser1b2fab

Ėý

Sequential circuits are of two types: synchronous and asynchronous. Synchronous circuits have a common clock for all flip-flops, while asynchronous circuits do not. The document then discusses the design process for synchronous sequential circuits and provides an example of designing a sequence detector circuit to output 1 when the input sequence is 1111 and 0 otherwise. It explains the use of state diagrams and tables to design sequential logic circuits using flip-flops like registers, counters, and shift registers.Recently uploaded (20)

Computational Photography: How Technology is Changing Way We Capture the World

Computational Photography: How Technology is Changing Way We Capture the WorldHusseinMalikMammadli

Ėý

ðļ Computational Photography (Computer Vision/Image): How Technology is Changing the Way We Capture the World

Heç dÞÅÞnmÞsÞnÞzmÞ, mÞasir smartfonlar vÉ kameralar necÉ bu qÉdÉr gÃķzÉl gÃķrÞntÞlÉr yaradÄąr? Bunun sirri Computational FotoqrafiyasÄąnda(Computer Vision/Imaging) gizlidirâÅÉkillÉri çÉkmÉ vÉ emal etmÉ Ãžsulumuzu tÉkmillÉÅdirÉn, kompÞter elmi ilÉ fotoqrafiyanÄąn inqilabi birlÉÅmÉsi.Inside Freshworks' Migration from Cassandra to ScyllaDB by Premkumar Patturaj

Inside Freshworks' Migration from Cassandra to ScyllaDB by Premkumar PatturajScyllaDB

Ėý

Freshworks migrated from Cassandra to ScyllaDB to handle growing audit log data efficiently. Cassandra required frequent scaling, complex repairs, and had non-linear scaling. ScyllaDB reduced costs with fewer machines and improved operations. Using Zero Downtime Migration (ZDM), they bulk-migrated data, performed dual writes, and validated consistency.A Framework for Model-Driven Digital Twin Engineering

A Framework for Model-Driven Digital Twin EngineeringDaniel Lehner

Ėý

šÝšÝßĢs from my PhD Defense at Johannes Kepler University, held on Janurary 10, 2025.

The full thesis is available here: https://epub.jku.at/urn/urn:nbn:at:at-ubl:1-8389630B Images and Counting: Scaling Canva's Content-Understanding Pipelines by K...

30B Images and Counting: Scaling Canva's Content-Understanding Pipelines by K...ScyllaDB

Ėý

Scaling content understanding for billions of images is no easy feat. This talk dives into building extreme label classification models, balancing accuracy & speed, and optimizing ML pipelines for scale. You'll learn new ways to tackle real-time performance challenges in massive data environments.World Information Architecture Day 2025 - UX at a Crossroads

World Information Architecture Day 2025 - UX at a CrossroadsJoshua Randall

Ėý

User Experience stands at a crossroads: will we live up to our potential to design a better world? or will we be co-opted by âproduct managementâ or another business buzzword?

Looking backwards, this talk will show how UX has repeatedly failed to create a better world, drawing on industry data from Nielsen Norman Group, Baymard, MeasuringU, WebAIM, and others.

Looking forwards, this talk will argue that UX must resist hype, say no more often and collaborate less often (you read that right), and become a true profession â in order to be able to design a better world.Endpoint Backup: 3 Reasons MSPs Ignore It

Endpoint Backup: 3 Reasons MSPs Ignore ItMSP360

Ėý

Many MSPs overlook endpoint backup, missing out on additional profit and leaving a gap that puts client data at risk.

Join our webinar as we break down the top challenges of endpoint backupâand how to overcome them.MIND Revenue Release Quarter 4 2024 - Finacial Presentation

MIND Revenue Release Quarter 4 2024 - Finacial PresentationMIND CTI

Ėý

MIND Revenue Release Quarter 4 2024 - Finacial PresentationTransform Your Future with Front-End Development Training

Transform Your Future with Front-End Development TrainingVtechlabs

Ėý

Kickstart your career in web development with our front-end web development course in Vadodara. Learn HTML, CSS, JavaScript, React, and more through hands-on projects and expert mentorship. Our front-end development course with placement includes real-world training, mock interviews, and job assistance to help you secure top roles like Front-End Developer, UI/UX Developer, and Web Designer.

Join VtechLabs today and build a successful career in the booming IT industry!Gojek Clone Multi-Service Super App.pptx

Gojek Clone Multi-Service Super App.pptxV3cube

Ėý

Gojek Clone is a versatile multi-service super app that offers ride-hailing, food delivery, payment services, and more, providing a seamless experience for users and businesses alike on a single platform.DealBook of Ukraine: 2025 edition | AVentures Capital

DealBook of Ukraine: 2025 edition | AVentures CapitalYevgen Sysoyev

Ėý

The DealBook is our annual overview of the Ukrainian tech investment industry. This edition comprehensively covers the full year 2024 and the first deals of 2025. SMART SENTRY CYBER THREAT INTELLIGENCE IN IIOT

SMART SENTRY CYBER THREAT INTELLIGENCE IN IIOTTanmaiArni

Ėý

SMART SENTRY CYBER THREAT INTELLIGENCE IN IIOTTrustArc Webinar - Building your DPIA/PIA Program: Best Practices & Tips

TrustArc Webinar - Building your DPIA/PIA Program: Best Practices & TipsTrustArc

Ėý

Understanding DPIA/PIAs and how to implement them can be the key to embedding privacy in the heart of your organization as well as achieving compliance with multiple data protection / privacy laws, such as GDPR and CCPA. Indeed, the GDPR mandates Privacy by Design and requires documented Data Protection Impact Assessments (DPIAs) for high risk processing and the EU AI Act requires an assessment of fundamental rights.

How can you build this into a sustainable program across your business? What are the similarities and differences between PIAs and DPIAs? What are the best practices for integrating PIAs/DPIAs into your data privacy processes?

Whether you're refining your compliance framework or looking to enhance your PIA/DPIA execution, this session will provide actionable insights and strategies to ensure your organization meets the highest standards of data protection.

Join our panel of privacy experts as we explore:

- DPIA & PIA best practices

- Key regulatory requirements for conducting PIAs and DPIAs

- How to identify and mitigate data privacy risks through comprehensive assessments

- Strategies for ensuring documentation and compliance are robust and defensible

- Real-world case studies that highlight common pitfalls and practical solutionsEarly Adopter's Guide to AI Moderation (Preview)

Early Adopter's Guide to AI Moderation (Preview)nick896721

Ėý

Early Adopter's Guide to AI Moderation preview by User Interviews.FinTech - US Annual Funding Report - 2024.pptx

FinTech - US Annual Funding Report - 2024.pptxTracxn

Ėý

US FinTech 2024, offering a comprehensive analysis of key trends, funding activities, and top-performing sectors that shaped the FinTech ecosystem in the US 2024. The report delivers detailed data and insights into the region's funding landscape and other developments. We believe this report will provide you with valuable insights to understand the evolving market dynamics.Technology use over time and its impact on consumers and businesses.pptx

Technology use over time and its impact on consumers and businesses.pptxkaylagaze

Ėý

In this presentation, I will discuss how technology has changed consumer behaviour and its impact on consumers and businesses. I will focus on internet access, digital devices, how customers search for information and what they buy online, video consumption, and lastly consumer trends.

Understanding Traditional AI with Custom Vision & MuleSoft.pptx

Understanding Traditional AI with Custom Vision & MuleSoft.pptxshyamraj55

Ėý

Understanding Traditional AI with Custom Vision & MuleSoft.pptx | ### šÝšÝßĢ Deck Description:

This presentation features Atul, a Senior Solution Architect at NTT DATA, sharing his journey into traditional AI using Azure's Custom Vision tool. He discusses how AI mimics human thinking and reasoning, differentiates between predictive and generative AI, and demonstrates a real-world use case. The session covers the step-by-step process of creating and training an AI model for image classification and object detectionâspecifically, an ad display that adapts based on the viewer's gender. Atulavan highlights the ease of implementation without deep software or programming expertise. The presentation concludes with a Q&A session addressing technical and privacy concerns.Future-Proof Your Career with AI Options

Future-Proof Your Career with AI OptionsDianaGray10

Ėý

Learn about the difference between automation, AI and agentic and ways you can harness these to further your career. In this session you will learn:

Introduction to automation, AI, agentic

Trends in the marketplace

Take advantage of UiPath training and certification

In demand skills needed to strategically position yourself to stay ahead

â If you have any questions or feedback, please refer to the "Women in Automation 2025" dedicated Forum thread. You can find there extra details and updates.L01 Introduction to Nanoindentation - What is hardness

L01 Introduction to Nanoindentation - What is hardnessRostislavDaniel

Ėý

Introduction to NanoindentationThe Future of Repair: Transparent and Incremental by Botond DeĖnes

The Future of Repair: Transparent and Incremental by Botond DeĖnesScyllaDB

Ėý

Regularly run repairs are essential to keep clusters healthy, yet having a good repair schedule is more challenging than it should be. Repairs often take a long time, preventing running them often. This has an impact on data consistency and also limits the usefulness of the new repair based tombstone garbage collection. We want to address these challenges by making repairs incremental and allowing for automatic repair scheduling, without relying on external tools.Computational Photography: How Technology is Changing Way We Capture the World

Computational Photography: How Technology is Changing Way We Capture the WorldHusseinMalikMammadli

Ėý

Synchronous counters

- 2. Synchronous Counter ï Clock pulses are applied to the input of all flip-flops. ï Common clock trigger all flip-flops simultaneously ï T=0 or J=K=0 (flip-flop does not change state) ï T=1 or J=K=1 (flip-flop complements)

- 3. Types of Synchronous Counters ï Binary Counter ï Up-Down Binary Counter ï BCD Counter ï Binary Counter with Parallel Load

- 4. a. Binary Counter ï The flip-flop in the least significant position is complemented in every pulse. ï A flip-flop in any other position is complemented when all the bits in the lower significant positions are equal to 1. ïIf J and K = 0 (state of the counter does not change), however if it is = 1 counter is enabled.

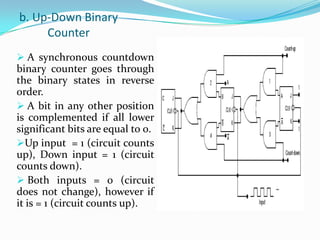

- 5. b. Up-Down Binary Counter ï A synchronous countdown binary counter goes through the binary states in reverse order. ï A bit in any other position is complemented if all lower significant bits are equal to 0. ïUp input = 1 (circuit counts up), Down input = 1 (circuit counts down). ï Both inputs = 0 (circuit does not change), however if it is = 1 (circuit counts up).

- 6. c. BCD Counter ï A BCD counts in binary-coded decimal from 0000 to 1001 and back to 0000. Because of the return to 0 after a count of 9. ï Output âYâ is equal to 1 when the present state is 1001. ï âYâ can enable the count of the next higher significant decade while the same pulse switches the present decade from 1001 to 0000. ï The unused states for minterms 10 to 15 are taken as donât-care terms. ï The simplified functions are: T Q1 = 1 T Q2 = Qâ8 Q1 T Q4 = Q2 Q1 T Q8 = Q8 Q1 + Q4 Q2 Q1 Y = Q8 Q1

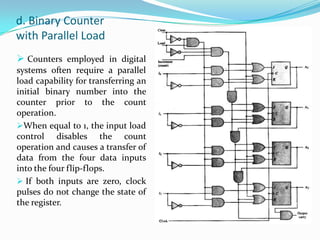

- 7. d. Binary Counter with Parallel Load ï Counters employed in digital systems often require a parallel load capability for transferring an initial binary number into the counter prior to the count operation. ïWhen equal to 1, the input load control disables the count operation and causes a transfer of data from the four data inputs into the four flip-flops. ï If both inputs are zero, clock pulses do not change the state of the register.

- 8. FUNCTION TABLE FOR THE COUNTER Clear Clock Load Count Function 0 X X X Clear to 0 1 1 X Load inputs 1 0 1 Count next binary state 1 0 0 No change ïThe four control inputs â Clear, Clock, Load, Count â determine the next state. ï Clear input is asynchronous and when equal to 0, causes the counter to be cleared. ï X symbolize donât care conditions for the other inputs. ï With the Load and Count inputs both 0, the output do not change.