Timing Analysis

16 likes6,434 views

The document discusses static timing analysis which is used to verify that logic circuits meet timing requirements. It analyzes different types of timing paths like pad-to-pad, pad-to-setup, clock-to-pad. Static timing analysis is preferred over dynamic analysis for verifying timings in large designs due to faster run times. An example shows calculating maximum frequency of operation by analyzing all path delays in a circuit.

1 of 29

Recommended

Physical design

Physical design Mantra VLSI

Ěý

VLSI Physical Design

Data preparation, import design, floorplan

Power planing

power ring, core power, IO power ring, pad, bump creattion.

Physical Verification.Sta by usha_mehta

Sta by usha_mehtaUsha Mehta

Ěý

This presentation is expert talk at Two day's International Webinar on "Testing and Verification of VLSI Design"ASIC Design Flow | Physical Design | VLSI

ASIC Design Flow | Physical Design | VLSI Jayant Suthar

Ěý

This document provides an overview of the ASIC design process, which includes the following main steps:

1. Front-end design including market research, specification, architecture, and RTL design.

2. Verification of the RTL code by verification engineers.

3. Synthesis of the RTL code into a gate-level netlist, followed by equivalence checking.

4. Physical design including placement and routing of standard cells, followed by extraction of parasitic components and timing analysis.

5. Physical verification including design rule checking and layout vs schematic checking.Clock Tree Timing 101

Clock Tree Timing 101Silicon Labs

Ěý

Silicon Labs offers the industry’s broadest portfolio of crystal oscillator, clock generator and clock buffer products and PCI Express (PCIe) clock generators and PCI Express buffers.Implementing Useful Clock Skew Using Skew Groups

Implementing Useful Clock Skew Using Skew GroupsM Mei

Ěý

Implementing useful skew through skew groups or manual buffer insertion can improve timing in a large memory block design. Skew groups define a target skew value for groups of clock pins before clock tree synthesis, resulting in a smaller clock tree, lower power increase, and less routing complexity compared to manual buffer insertion. Manual insertion precisely controls skew by adding buffers but dramatically increases clock cell count and power consumption versus skew groups. Both methods effectively improved setup timing for the memory block design.Logic synthesis with synopsys design compiler

Logic synthesis with synopsys design compilernaeemtayyab

Ěý

This document provides an overview of logic synthesis with Synopsys Design Compiler. It discusses the ASIC design flow, logic synthesis process, the Design Compiler tool, and the steps to use Design Compiler including project setup, reading the design, setting constraints, optimizing the design, and analyzing results. The goals of logic synthesis are to convert HDL to an optimized gate-level design given a library and constraints. Design Compiler is used to perform logic synthesis and optimization for area, speed or power.

Human: Thank you, that is a concise 3 sentence summary that captures the key aspects of the document.Physical design-complete

Physical design-completeMurali Rai

Ěý

This document discusses various concepts related to physical design implementation. It describes the inputs and outputs of physical design tools, important checks to perform before starting design such as clock and high fanout net budgeting, and concepts like floorplanning, placement, routing, libraries, multi-voltage design, and clock tree synthesis and optimization.Basic synthesis flow and commands in digital VLSI

Basic synthesis flow and commands in digital VLSISurya Raj

Ěý

This document discusses logic synthesis, including the basic synthesis flow and commands, synthesis script flow, technology libraries, design objects like cells and ports, timing paths, and constraints like defining clocks and input/output delays. It provides examples of setting library variables, reading and writing designs, and applying constraints to clocks and I/O. The document contains information on synthesis tools and processes at a high level.Timing and Design Closure in Physical Design Flows

Timing and Design Closure in Physical Design Flows Olivier Coudert

Ěý

A physical design flow consists of producing a production-worthy layout from a gate-level netlist subject to a set of constraints. We focus on the problems imposed by shrinking process technologies. It exposes the problems of timing closure, signal integrity, design variable dependencies, clock and power/ground routing, and design signoff. It also surveys some physical design flows, and outlines a refinement-based flow. Floor plan & Power Plan

Floor plan & Power Plan Prathyusha Madapalli

Ěý

The document discusses floor planning, which is the first step in physical design. It involves defining the size of the chip, pre-placing hard macros, I/O pads, and defining the power grid. A good floorplan partitions the design into functional blocks, arranges the blocks on the chip, places macros and I/O pads, and decides on the power distribution. Key inputs to floorplanning include the netlist, physical and timing libraries, timing constraints, and power requirements. The document then discusses various aspects of floorplanning such as die size calculations, macro placement guidelines, and different types of physical cells.VLSI-Physical Design- Tool Terminalogy

VLSI-Physical Design- Tool TerminalogyMurali Rai

Ěý

The physical design flow begins with placement which involves assigning exact locations to modules like gates and standard cells to minimize area and interconnect cost while meeting timing constraints, with the goal of enabling easier routing; placement tools take as input the netlist, floorplan, libraries, and constraints to perform global and detailed placement as well as optimization. The quality of placement significantly impacts the ability to route the design successfully.Timing analysis

Timing analysisKunal Doshi

Ěý

The paper describes the basic of Timing analysis like setup time, hold time, delays in logic circuits, timing violations and different types of timing paths like flip-flop to flip-flop path, clock gating path, asynchronous signal path, half cycle path, flip-flop to output path, input to flip-flop path and input to output path.Define Width and Height of Core and Die (http://www.vlsisystemdesign.com/PD-F...

Define Width and Height of Core and Die (http://www.vlsisystemdesign.com/PD-F...VLSI SYSTEM Design

Ěý

https://www.udemy.com/vlsi-academy

The very first step in chip design is floorplanning, in which the width and height of the chip, basically the area of the chip, is defined. A chip consists of two parts, 'core' and 'die'.

12 static timing_analysis_3_clocked_design

12 static timing_analysis_3_clocked_designUsha Mehta

Ěý

The document discusses concepts related to static timing analysis (STA) for clocked designs. It defines key timing terms like timing paths, clock skew, slack, and false paths. It explains that STA involves breaking a circuit into timing paths and calculating the delay of each path to check if timing constraints are met. Timing paths connect flip-flops and have startpoints and endpoints. Clock skew is the difference in latency for a clock signal to reach flip-flops. Slack is the difference between a path's required time and arrival time.GUI for DRV fix in ICC2

GUI for DRV fix in ICC2Prashanth Chokkarapu

Ěý

This is a custom GUI, which eases fixing violations either by adding buffer, cloning or sizing. Drop down menu item is created in ICC2 layout window. Desired terminals can be selected by dragging or adding points in rectilinear fashion and desired locations can be selected for adding new buffer. Inputs of physical design

Inputs of physical designKishore Sai Addanki

Ěý

This document discusses the key inputs required for the physical design phase of a VLSI chip, using Synopsys tools as an example. The main inputs are: (1) a gate-level netlist describing the logical connections, (2) libraries providing timing, power and physical information for standard cells and macros, (3) a technology file describing manufacturing details, (4) parasitic extraction files (TLU+) for timing analysis, and (5) constraints describing design objectives. Additional inputs include floorplanning guidelines, scenarios for optimization, and reference design methodologies. The goal of physical design is to implement the logic from the netlist while meeting area, timing and power targets.13 static timing_analysis_4_set_up_and_hold_time_violation_remedy

13 static timing_analysis_4_set_up_and_hold_time_violation_remedyUsha Mehta

Ěý

The document discusses static timing analysis concepts including set-up time, hold time, timing violations, and techniques for fixing violations. It provides examples of how delays are considered in an ideal case without set-up/hold times versus cases with set-up/hold times. Methods for calculating maximum clock frequency and identifying violations are described. Ways to address violations including adjusting buffering, cell sizing, and placement are outlined. The role of static timing analysis in ASIC design flows is also summarized.Understanding cts log_messages

Understanding cts log_messagesMujahid Mohammed

Ěý

Clock tree synthesis log messages provide information about:

1) Preprocessing steps like design updates, buffer characterization, and clock tree constraints.

2) The clock tree synthesis process which includes clustering, meeting timing targets, and reporting results.

3) Post processing steps like embedded clock tree optimization, DRC fixing, and placement legalization.Eco

EcoRajesh M

Ěý

This document discusses engineering change orders (ECOs) used to fix timing, functional, power, and clock issues after physical design and sign-off. It describes the motivation for ECOs due to tool limitations and differences between implementation and sign-off. Common ECO techniques are listed for timing (driver upsizing, buffer insertion, etc.), power (vt-swapping, downsizing, etc.), and metal-only ECOs. Timing ECO tools from Synopsys, Cadence, and other vendors are also mentioned. Upcoming ECO technologies like dynamic power optimization and automatic legalization are noted.Powerplanning

PowerplanningVLSI SYSTEM Design

Ěý

https://www.udemy.com/vlsi-academy

Usually, while drawing any circuit on paper, we have only one 'vdd' at the top and one 'vss' at the bottom. But on a chip, it becomes necessary to have a grid structure of power, with more than one 'vdd' and 'vss'. The concept of power grid structure would be uploaded soon. It is actually the scaling trend that drives chip designers for power grid structure.

Physical Design Flow Challenges at 28nm on Multi-million Gate Blocks

Physical Design Flow Challenges at 28nm on Multi-million Gate BlockseInfochips (An Arrow Company)

Ěý

This is the presentation that was shared by Nilesh Ranpura and Vineeth Mathramkote at CDNLIVE 2015. The session briefs about the implementation challenges and covers the solution approach and how to achieve resultsMulti mode multi corner (mmmc)

Multi mode multi corner (mmmc)shaik sharief

Ěý

This document discusses multi mode multi corner (MMMC) analysis for chip design. It defines that a mode is a set of design parameters like clocks and timing constraints, and a corner captures process, voltage, and temperature variations. It provides examples of multiple modes like normal, sleep, and test modes and corners for temperature, voltage, process variations, and parasitic interconnects. The document gives an example of analyzing a chip with 4 modes under 3 process-voltage-temperature corners and 3 parasitic interconnect corners, showing 9 analysis cases.Synopsys Fusion Compiler-Comprehensive RTL-to-GDSII Implementation System

Synopsys Fusion Compiler-Comprehensive RTL-to-GDSII Implementation SystemMostafa Khamis

Ěý

Fusion Compiler is the next-generation RTL-to-GDSII implementation system architected to address the complexities of advanced node designs and deliver up to 20% improved PPA while reducing Time To Results (TTR) by 2X. Dft (design for testability)

Dft (design for testability)shaik sharief

Ěý

DFT (design for testability) is a technique that facilitates making a design testable after production by adding extra logic during the design process. This extra logic helps with post-production testing. DFT is needed because manufacturing processes are not perfect and can introduce defects. Methods like adding scan chains are used, where scanned flip-flops are connected in series to form a shift register and improve controllability and observability for testing. Common fault models tested for include stuck-at faults, where a line is stuck at either a 0 or 1 value due to defects introduced during manufacturing.Digital VLSI Design : Introduction

Digital VLSI Design : IntroductionUsha Mehta

Ěý

This document discusses digital VLSI design flows. It begins by acknowledging previous work that informed the presentation. It then discusses considerations in developing an electronic system, including components of the system. It describes integrated circuits based on application, fabrication technology, device, and device count. It discusses using standard or application-specific integrated circuits. It outlines a top-down design approach and terminology used in the design flow.Chapter1.slides

Chapter1.slidesAvinash Pillai

Ěý

This document introduces VLSI physical design. It discusses how the number of transistors on chips has rapidly increased over time, from 100,000 to over 3 million. Complex chip design is now only possible using computer-aided design tools. The document outlines the different levels of abstraction in chip design from behavioral modeling down to the cell/mask level. It provides examples of logical and architectural design, and discusses the different layout styles including full-custom, gate-array, and standard-cell approaches.Complete ASIC design flow - VLSI UNIVERSE

Complete ASIC design flow - VLSI UNIVERSEVLSIUNIVERSE

Ěý

Visit https://www.vlsiuniverse.com/

https://www.vlsiuniverse.com/2020/05/complete-asic-design-flow.html

This is the standard VLSI design flow that every semiconductor company follows. The complete ASIC design flow is explained by considering each and every stage.Vlsi physical design (Back End Process)

Vlsi physical design (Back End Process)CHENCHU CHANDU PRASANTH NADELLA

Ěý

Physical Design Include Floor Planning, Placement,Routing,Power and Clock Distribution Problems in VLSIFIFOPt

FIFOPtsumeet jain

Ěý

This document describes static timing analysis of a FIFO design using Synopsys Primetime. It includes details of the FIFO design, an introduction to Primetime, the Primetime user design flow, setting up Primetime, using it for timing analysis, Verilog code for the FIFO, a script file, and expected timing report outputs. Primetime is used to perform gate-level timing analysis and check for timing violations related to setup/hold times and other constraints.More Related Content

What's hot (20)

Timing and Design Closure in Physical Design Flows

Timing and Design Closure in Physical Design Flows Olivier Coudert

Ěý

A physical design flow consists of producing a production-worthy layout from a gate-level netlist subject to a set of constraints. We focus on the problems imposed by shrinking process technologies. It exposes the problems of timing closure, signal integrity, design variable dependencies, clock and power/ground routing, and design signoff. It also surveys some physical design flows, and outlines a refinement-based flow. Floor plan & Power Plan

Floor plan & Power Plan Prathyusha Madapalli

Ěý

The document discusses floor planning, which is the first step in physical design. It involves defining the size of the chip, pre-placing hard macros, I/O pads, and defining the power grid. A good floorplan partitions the design into functional blocks, arranges the blocks on the chip, places macros and I/O pads, and decides on the power distribution. Key inputs to floorplanning include the netlist, physical and timing libraries, timing constraints, and power requirements. The document then discusses various aspects of floorplanning such as die size calculations, macro placement guidelines, and different types of physical cells.VLSI-Physical Design- Tool Terminalogy

VLSI-Physical Design- Tool TerminalogyMurali Rai

Ěý

The physical design flow begins with placement which involves assigning exact locations to modules like gates and standard cells to minimize area and interconnect cost while meeting timing constraints, with the goal of enabling easier routing; placement tools take as input the netlist, floorplan, libraries, and constraints to perform global and detailed placement as well as optimization. The quality of placement significantly impacts the ability to route the design successfully.Timing analysis

Timing analysisKunal Doshi

Ěý

The paper describes the basic of Timing analysis like setup time, hold time, delays in logic circuits, timing violations and different types of timing paths like flip-flop to flip-flop path, clock gating path, asynchronous signal path, half cycle path, flip-flop to output path, input to flip-flop path and input to output path.Define Width and Height of Core and Die (http://www.vlsisystemdesign.com/PD-F...

Define Width and Height of Core and Die (http://www.vlsisystemdesign.com/PD-F...VLSI SYSTEM Design

Ěý

https://www.udemy.com/vlsi-academy

The very first step in chip design is floorplanning, in which the width and height of the chip, basically the area of the chip, is defined. A chip consists of two parts, 'core' and 'die'.

12 static timing_analysis_3_clocked_design

12 static timing_analysis_3_clocked_designUsha Mehta

Ěý

The document discusses concepts related to static timing analysis (STA) for clocked designs. It defines key timing terms like timing paths, clock skew, slack, and false paths. It explains that STA involves breaking a circuit into timing paths and calculating the delay of each path to check if timing constraints are met. Timing paths connect flip-flops and have startpoints and endpoints. Clock skew is the difference in latency for a clock signal to reach flip-flops. Slack is the difference between a path's required time and arrival time.GUI for DRV fix in ICC2

GUI for DRV fix in ICC2Prashanth Chokkarapu

Ěý

This is a custom GUI, which eases fixing violations either by adding buffer, cloning or sizing. Drop down menu item is created in ICC2 layout window. Desired terminals can be selected by dragging or adding points in rectilinear fashion and desired locations can be selected for adding new buffer. Inputs of physical design

Inputs of physical designKishore Sai Addanki

Ěý

This document discusses the key inputs required for the physical design phase of a VLSI chip, using Synopsys tools as an example. The main inputs are: (1) a gate-level netlist describing the logical connections, (2) libraries providing timing, power and physical information for standard cells and macros, (3) a technology file describing manufacturing details, (4) parasitic extraction files (TLU+) for timing analysis, and (5) constraints describing design objectives. Additional inputs include floorplanning guidelines, scenarios for optimization, and reference design methodologies. The goal of physical design is to implement the logic from the netlist while meeting area, timing and power targets.13 static timing_analysis_4_set_up_and_hold_time_violation_remedy

13 static timing_analysis_4_set_up_and_hold_time_violation_remedyUsha Mehta

Ěý

The document discusses static timing analysis concepts including set-up time, hold time, timing violations, and techniques for fixing violations. It provides examples of how delays are considered in an ideal case without set-up/hold times versus cases with set-up/hold times. Methods for calculating maximum clock frequency and identifying violations are described. Ways to address violations including adjusting buffering, cell sizing, and placement are outlined. The role of static timing analysis in ASIC design flows is also summarized.Understanding cts log_messages

Understanding cts log_messagesMujahid Mohammed

Ěý

Clock tree synthesis log messages provide information about:

1) Preprocessing steps like design updates, buffer characterization, and clock tree constraints.

2) The clock tree synthesis process which includes clustering, meeting timing targets, and reporting results.

3) Post processing steps like embedded clock tree optimization, DRC fixing, and placement legalization.Eco

EcoRajesh M

Ěý

This document discusses engineering change orders (ECOs) used to fix timing, functional, power, and clock issues after physical design and sign-off. It describes the motivation for ECOs due to tool limitations and differences between implementation and sign-off. Common ECO techniques are listed for timing (driver upsizing, buffer insertion, etc.), power (vt-swapping, downsizing, etc.), and metal-only ECOs. Timing ECO tools from Synopsys, Cadence, and other vendors are also mentioned. Upcoming ECO technologies like dynamic power optimization and automatic legalization are noted.Powerplanning

PowerplanningVLSI SYSTEM Design

Ěý

https://www.udemy.com/vlsi-academy

Usually, while drawing any circuit on paper, we have only one 'vdd' at the top and one 'vss' at the bottom. But on a chip, it becomes necessary to have a grid structure of power, with more than one 'vdd' and 'vss'. The concept of power grid structure would be uploaded soon. It is actually the scaling trend that drives chip designers for power grid structure.

Physical Design Flow Challenges at 28nm on Multi-million Gate Blocks

Physical Design Flow Challenges at 28nm on Multi-million Gate BlockseInfochips (An Arrow Company)

Ěý

This is the presentation that was shared by Nilesh Ranpura and Vineeth Mathramkote at CDNLIVE 2015. The session briefs about the implementation challenges and covers the solution approach and how to achieve resultsMulti mode multi corner (mmmc)

Multi mode multi corner (mmmc)shaik sharief

Ěý

This document discusses multi mode multi corner (MMMC) analysis for chip design. It defines that a mode is a set of design parameters like clocks and timing constraints, and a corner captures process, voltage, and temperature variations. It provides examples of multiple modes like normal, sleep, and test modes and corners for temperature, voltage, process variations, and parasitic interconnects. The document gives an example of analyzing a chip with 4 modes under 3 process-voltage-temperature corners and 3 parasitic interconnect corners, showing 9 analysis cases.Synopsys Fusion Compiler-Comprehensive RTL-to-GDSII Implementation System

Synopsys Fusion Compiler-Comprehensive RTL-to-GDSII Implementation SystemMostafa Khamis

Ěý

Fusion Compiler is the next-generation RTL-to-GDSII implementation system architected to address the complexities of advanced node designs and deliver up to 20% improved PPA while reducing Time To Results (TTR) by 2X. Dft (design for testability)

Dft (design for testability)shaik sharief

Ěý

DFT (design for testability) is a technique that facilitates making a design testable after production by adding extra logic during the design process. This extra logic helps with post-production testing. DFT is needed because manufacturing processes are not perfect and can introduce defects. Methods like adding scan chains are used, where scanned flip-flops are connected in series to form a shift register and improve controllability and observability for testing. Common fault models tested for include stuck-at faults, where a line is stuck at either a 0 or 1 value due to defects introduced during manufacturing.Digital VLSI Design : Introduction

Digital VLSI Design : IntroductionUsha Mehta

Ěý

This document discusses digital VLSI design flows. It begins by acknowledging previous work that informed the presentation. It then discusses considerations in developing an electronic system, including components of the system. It describes integrated circuits based on application, fabrication technology, device, and device count. It discusses using standard or application-specific integrated circuits. It outlines a top-down design approach and terminology used in the design flow.Chapter1.slides

Chapter1.slidesAvinash Pillai

Ěý

This document introduces VLSI physical design. It discusses how the number of transistors on chips has rapidly increased over time, from 100,000 to over 3 million. Complex chip design is now only possible using computer-aided design tools. The document outlines the different levels of abstraction in chip design from behavioral modeling down to the cell/mask level. It provides examples of logical and architectural design, and discusses the different layout styles including full-custom, gate-array, and standard-cell approaches.Complete ASIC design flow - VLSI UNIVERSE

Complete ASIC design flow - VLSI UNIVERSEVLSIUNIVERSE

Ěý

Visit https://www.vlsiuniverse.com/

https://www.vlsiuniverse.com/2020/05/complete-asic-design-flow.html

This is the standard VLSI design flow that every semiconductor company follows. The complete ASIC design flow is explained by considering each and every stage.Vlsi physical design (Back End Process)

Vlsi physical design (Back End Process)CHENCHU CHANDU PRASANTH NADELLA

Ěý

Physical Design Include Floor Planning, Placement,Routing,Power and Clock Distribution Problems in VLSIDefine Width and Height of Core and Die (http://www.vlsisystemdesign.com/PD-F...

Define Width and Height of Core and Die (http://www.vlsisystemdesign.com/PD-F...VLSI SYSTEM Design

Ěý

Viewers also liked (20)

FIFOPt

FIFOPtsumeet jain

Ěý

This document describes static timing analysis of a FIFO design using Synopsys Primetime. It includes details of the FIFO design, an introduction to Primetime, the Primetime user design flow, setting up Primetime, using it for timing analysis, Verilog code for the FIFO, a script file, and expected timing report outputs. Primetime is used to perform gate-level timing analysis and check for timing violations related to setup/hold times and other constraints.SNUG 2011 paper

SNUG 2011 paperDavid Tester

Ěý

This document discusses the challenges of inserting tap cells in power gating designs with tapless standard cells. Special always-on tap cells are required to maintain transistor back biasing when power domains are shut off. A domain-based methodology is presented for selecting the correct tap cell type and connecting tap cells to the proper power supplies to ensure power integrity. The methodology involves scripts for domain-based tap cell logic and physical connections. An example implementation demonstrates the methodology.Aldec overview 2011-10 revised

Aldec overview 2011-10 revisedPrateek Chopra

Ěý

Aldec is a leading EDA company founded in 1984 that provides RTL simulation, verification, and emulation solutions. It has over 200 employees and 30,000 licenses worldwide. Aldec's key products include Active-HDL for simulation, Riviera-PRO for verification, ALINTTM for linting, and HES for emulation. Aldec focuses on continuous innovation to provide better performance, more features, and lower prices than competitors.System Verilog 2009 & 2012 enhancements

System Verilog 2009 & 2012 enhancementsSubash John

Ěý

This document summarizes enhancements made to System Verilog in 2009 and 2012. The 2009 enhancements included final blocks, bit selects of expressions, edge detection for DDR logic, fork-join improvements, and display enhancements. The 2012 enhancements extended enums, added scale factors to real constants and mixed-signal assertions, introduced aspect-oriented programming features, and removed X-optimism using new keywords. It also proposed signed operators and discussed some high-level problems not yet addressed.Session 9 advance_verification_features

Session 9 advance_verification_featuresNirav Desai

Ěý

The document discusses several advanced verification features in SystemVerilog including the Direct Programming Interface (DPI), regions, and program/clocking blocks. The DPI allows Verilog code to directly call C functions without the complexity of Verilog PLI. Regions define the execution order of events and include active, non-blocking assignment, observed, and reactive regions. Clocking blocks make timing and synchronization between blocks explicit, while program blocks provide entry points and scopes for testbenches.System Verilog Functional Coverage

System Verilog Functional Coveragerraimi

Ěý

This document describes a unique functional coverage flow using SystemVerilog and NTB (Vera) at ARM, Inc. in Austin, Texas. They wanted to use SystemVerilog coverage but the tool did not fully support covergroups. So they wrote coverage in SystemVerilog using covered properties and covergroups, and translated the covergroups to NTB coverage_groups. This allowed training on SystemVerilog while still using the code, and retaining options for the future when full support was added. The process of translating between the two languages and the pros and cons of each approach are discussed.tau 2015 spyrou fpga timing

tau 2015 spyrou fpga timingTom Spyrou

Ěý

This document discusses the unique challenges in static timing analysis (STA) for field programmable gate arrays (FPGAs). It notes that FPGA timing analysis must account for the programmable logic blocks and routing in the device. Specifically, it outlines three main challenges: 1) modeling the delays of look-up tables (LUTs) which can implement different logic functions based on their configuration, 2) avoiding an explosion in the number of timing modes when analyzing hierarchical or complex blocks, and 3) accurately modeling the delays of pass gate multiplexers. It provides examples and potential approaches for addressing each challenge.System verilog important

System verilog importantelumalai7

Ěý

The document discusses the building blocks of a SystemVerilog testbench. It describes the program block, which encapsulates test code and allows reading/writing signals and calling module routines. Interface and clocking blocks are used to connect the testbench to the design under test. Assertions, randomization, and other features help create flexible testbenches to verify design correctness.System Verilog Tutorial - VHDL

System Verilog Tutorial - VHDLE2MATRIX

Ěý

This document provides an overview of System Verilog concepts including simulation and synthesis, modules and primitives, styles, data types, operators, and more. Key points covered include the module concept as the basic design unit, module declaration syntax, module instantiation, different styles like structural, RTL/dataflow and behavioral, data types for nets and registers, number representation formats, and basic Verilog operators. The document serves as a tutorial introduction to essential System Verilog language constructs.system verilog

system verilogVinchipsytm Vlsitraining

Ěý

The document describes a SystemVerilog verification methodology that includes assertion-based verification, coverage-driven verification, constrained random verification, and use of scoreboards and checkers. It outlines the verification flow from design specifications through testbench development, integration and simulation, and discusses techniques like self-checking test cases, top-level and block-level environments, and maintaining bug reports.Fundamentals of HDL (first 4 chapters only) - Godse

Fundamentals of HDL (first 4 chapters only) - GodseHammam

Ěý

In electronics, a hardware description language (HDL) is a specialized computer language used to program the structure, design and operation of electronic circuits, and most commonly, digital logic circuits.System verilog verification building blocks

System verilog verification building blocksNirav Desai

Ěý

SystemVerilog introduces key concepts like program blocks, interfaces, and clocking blocks to help with verification. Program blocks separate the testbench code from the design code to avoid race conditions. Interfaces encapsulate communication between blocks and help prevent errors from manual port connections. Clocking blocks synchronize signal drivers and allow specifying timing for sampled signals. Together these features help manage complexity when verifying designs.FIFO Design

FIFO DesignArrow Devices

Ěý

The document describes the design of a FIFO (first-in first-out) buffer. It explains the FIFO interface, protocol, datapath and control path. The FIFO uses a read and write pointer to control reading and writing of data to an internal memory buffer. Status signals like full and empty are generated by comparing the read and write pointers. The design aims to ensure reliable operation by following the specified protocol of not allowing a write when full or a read when empty.Simulation PowerPoint

Simulation PowerPointMelissa Wilson

Ěý

Simulations use carefully designed scenarios to develop specific competencies that can be transferred to the real world. Simulations put students in realistic situations to gain real-world experience on complex issues in a motivational way. Simulations allow teachers to take on a different role and students to develop flexible thinking, though some simulations require money and classroom time. The document provides several resources for both free and paid simulations in subjects like science, social studies, and business.Delays in verilog

Delays in verilogJITU MISTRY

Ěý

Delays in Verilog allow modeling of timing aspects like propagation delays. There are different types of delays depending on the design approach - gate level modeling uses rise, fall, and turn-off delays while dataflow modeling uses assignment delays on nets. Behavioral modeling supports regular delays before assignments, intra-assignment delays after the equals sign, and zero delays to ensure last execution. Sequential and parallel blocks also control statement ordering.Verilog HDL

Verilog HDLMantra VLSI

Ěý

This document provides an introduction to Verilog HDL including:

- An overview of Verilog keywords, data types, abstraction levels, and design methodology.

- Details on the history of Verilog including its development over time and transitions to newer standards.

- Explanations of key Verilog concepts like modules, ports, instantiation, stimuli, and lexical conventions.

Modules are the basic building blocks, ports define module interfaces, and instantiation replicates modules. Stimuli provide test inputs and lexical conventions cover syntax rules.Fifo first in first out powerpoint ppt slides.

Fifo first in first out powerpoint ppt slides.şÝşÝߣTeam.net

Ěý

The document describes the First In First Out (FIFO) concept through diagrams and text. FIFO refers to the queue discipline where the first item inserted into the queue will be the first item removed. The document contains several diagrams illustrating queues with items being added to the front and removed from the rear to demonstrate the FIFO principle. Descriptions accompany the diagrams to explain key FIFO concepts such as enqueue, dequeue, stacks, and inventory management.First In, First Out (FIFO); Last In, Last Out (LIFO)

First In, First Out (FIFO); Last In, Last Out (LIFO)UNowAcademics

Ěý

This document discusses two methods for valuing inventory - First In, First Out (FIFO) and Last In, First Out (LIFO). FIFO matches the costs of the oldest inventory units with the sales revenue, while LIFO matches the costs of the newest inventory units with sales. The document provides examples to illustrate how inventory values would be reported under each method when a company produces and sells different quantities of inventory over time.Similar to Timing Analysis (20)

file-3.ppt

file-3.pptteja411944

Ěý

1. Static timing analysis is a methodology for verifying timing characteristics of a design without test vectors, which is faster than simulation and guarantees 100% coverage of timing paths.

2. It involves breaking a circuit into timing paths, calculating the delay of each path, and checking if paths meet timing constraints. Timing paths are grouped by controlling clocks.

3. The maximum clock frequency is determined by the timing parameters of flip-flops and gates in the circuit. Clock skew between flip-flops must be considered and cannot exceed setup/hold times.file-3.ppt

file-3.pptteja411944

Ěý

1. Static timing analysis is a methodology for verifying timing characteristics of a design without test vectors, which is faster than simulation and guarantees 100% coverage of timing paths.

2. It involves breaking a circuit into timing paths, calculating the delay of each path, and checking if delays meet constraints. Timing paths are grouped by controlling clocks.

3. The maximum clock frequency is limited by flip-flop and gate delays. Clock skew between flip-flops must be less than the minimum setup/hold times to meet timing.Te442 lecture02-2016-14-4-2016-1

Te442 lecture02-2016-14-4-2016-1colman mboya

Ěý

This document discusses timing considerations for digital electronics systems using standard integrated circuits (ICs). It covers propagation delay, which is the time it takes for a change on an input to propagate to the output. Sequential circuits like flip-flops only change value in response to a clock signal, so their timing parameters are specified relative to the rising or falling edge of the clock. The maximum clock frequency of a sequential circuit can be determined by analyzing the propagation delays of its components and ensuring all timing requirements are met.design-compiler.pdf

design-compiler.pdfFrangoCamila

Ěý

Synthesis & gate-level simulation is introduced. The key topics covered include basic concepts of logic synthesis using Design Compiler, including logic level optimization, mapping, boundary optimization, and static timing analysis. Simulation of the gate-level netlist generated after synthesis is also discussed. An example lab is outlined to synthesize a simple 8-bit microprocessor and simulate the gate-level netlist.Major project iii 3

Major project iii 3Gopal Prasad Bansal

Ěý

This document presents a major project on hierarchical timing analysis of VLSI circuits. It includes an outline covering introduction, why timing analysis is needed, basics of timing analysis, static timing analysis, timing paths, hierarchical timing analysis applications, and conclusions. The introduction discusses using static timing analysis to ensure correct timing of clocks and signals. It also explains how hierarchical timing analysis can help alleviate large runtimes from flat analysis of growing design sizes. The document then covers various topics related to timing analysis including digital circuit to timing model conversions, static timing analysis concepts, different path types, and applications of hierarchical timing analysis.Timing notes 2006

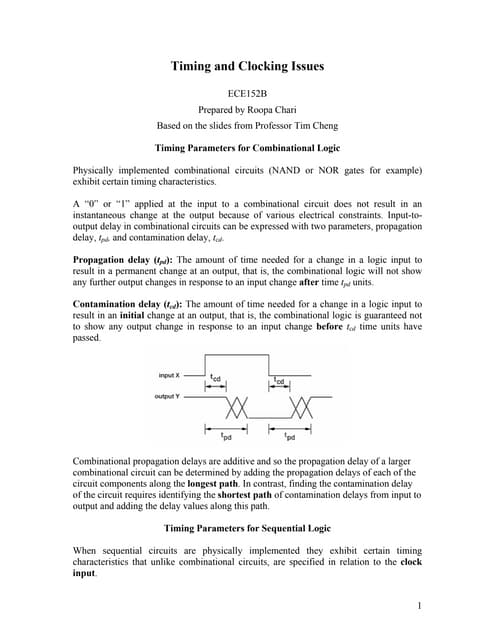

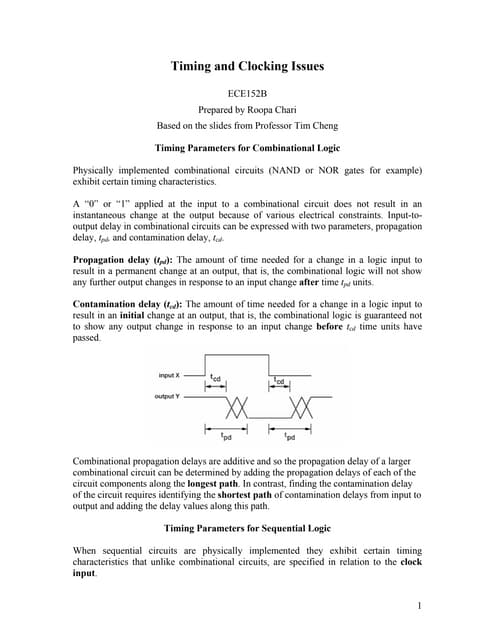

Timing notes 2006pavan kumar

Ěý

This document discusses timing parameters for combinational and sequential logic circuits. It defines propagation delay and contamination delay for combinational logic, and propagation delay, contamination delay, setup time, and hold time for sequential logic circuits like flip-flops. It also discusses determining maximum clock frequency for sequential circuits based on these timing parameters, modeling delays from gates and interconnect, using clock trees, and issues related to clock skew and jitter.Timing closure document

Timing closure documentAlan Tran

Ěý

The document discusses timing closure in FPGA design flows. It explains that timing requirements include clock period/frequency, throughput, and latency. The timing-driven design flow in Lattice Diamond is outlined, highlighting key steps like defining timing constraints, running synthesis and implementation with timing analysis, and iterating to resolve issues. Timing constraints like input/output delays and exceptions are also covered.sta slide ref.pdf

sta slide ref.pdfquandao25

Ěý

This document provides an overview of sequential clocking and static timing analysis for digital VLSI design. It discusses key timing parameters for sequential elements like setup time and hold time. It also explains how static timing analysis works by calculating arrival times and required arrival times for all nodes to find timing violations. The document notes that while static timing analysis is useful, it cannot analyze all timing issues and may report false paths. An example is provided to illustrate how arrival times, required arrival times and slack are calculated for a simple circuit. Finally, it mentions that design constraints must be specified to inform the timing analysis of requirements.Lecture-5-STA.pdf

Lecture-5-STA.pdfKarthikYogesh3

Ěý

This document provides an overview of sequential clocking and static timing analysis for digital VLSI design. It discusses key timing parameters for sequential elements like setup time and hold time. It also explains how static timing analysis works by calculating arrival times and required arrival times for all nodes to find timing violations. The document notes that while static timing analysis is useful, it cannot analyze all timing issues and may report false paths. An example is provided to illustrate how arrival times, required arrival times and slack are calculated for a simple circuit. Finally, it introduces the topic of design constraints which need to be specified to the timing analysis tool.VLSI Static Timing Analysis Setup And Hold Part 2

VLSI Static Timing Analysis Setup And Hold Part 2Amr Adel

Ěý

Understanding setup and hold timing checks and how to fix the

Topics included:

- Setup timing

- Hold timing

- 20 methods to fix timing violations. Each explained in detail

- ASIC flow, synthesis, local skew, pipelining, retiming, MCP, false paths, etc

15757597 (1).ppt

15757597 (1).pptRevathiMohan14

Ěý

This document discusses static timing analysis (STA) and dynamic timing analysis. It provides examples of using STA on a sorting circuit design to find the critical path and check that it meets the timing constraint of a 20ns clock period. STA is performed after synthesis and mapping and finds the longest path to be 9.739ns, providing over 10ns of slack compared to the timing constraint.Level sensitive scan design(LSSD) and Boundry scan(BS)

Level sensitive scan design(LSSD) and Boundry scan(BS)Praveen Kumar

Ěý

This presentation contains,

Introduction,design for testability, scan chain, operation, scan structure, test vectors, Boundry scan, test logic, operation, BS cell, states of TAP controller, Boundry scan instructions.

A Robust UART Architecture Based on Recursive Running Sum Filter for Better N...

A Robust UART Architecture Based on Recursive Running Sum Filter for Better N...Kevin Mathew

Ěý

This document describes a project to design a robust UART architecture using a recursive running sum filter for better noise performance. It discusses adding noise to communication channels to test noise performance. It then describes implementing a UART receiver using a recursive running sum filter to reduce noise while maintaining signal integrity. The UART design is tested on a Nexys3 Spartan-6 FPGA board in Xilinx ISE using VHDL. Simulation results at different noise levels show the filter is effective at reducing noise.Tugas komjar 7-yee

Tugas komjar 7-yeeramasatriaf

Ěý

The document is a report on a Wireshark lab analyzing TCP and UDP network traffic.

For the TCP analysis:

- The client IP address is 192.168.1.102 and port 1161, the server is 128.119.245.12 on port 80.

- The SYN segment has a sequence number of 0 and identifies the segment with the SYN flag.

- The SYNACK from the server acknowledges 1 and has a sequence number of 0.

- The HTTP POST has a sequence number of 1.

For the UDP analysis:

- The UDP header has 4 fields - Source Port, Destination Port, Length, and Checksum.

- The checksum covers the pseudo headerIEEE1588-v2

IEEE1588-v2Guider Lee

Ěý

This document provides an overview of IEEE 1588 precision time protocol (PTP). It describes IEEE 1588-2002 and 1588-2008 standards, including clock types, message types, best master clock algorithm, and synchronization methods. It also discusses message transport and some open source software implementations of PTP on Linux.07_Digital timing_&_Pipelining.ppt

07_Digital timing_&_Pipelining.pptBUCHUPALLIVIMALAREDD2

Ěý

This document discusses timing analysis of logic circuits. It defines propagation delay time (tp) as the time required for an output signal to change due to a change in the input signal. A timing diagram is used to graphically represent tp. The document discusses how real circuits have intrinsic resistance and capacitance that cause delay. It provides an example of calculating delay through a simple RC circuit. Combinational logic delay is represented using a cloud model. The document also discusses setup time, hold time, and register delay time for D flip-flops and how to calculate maximum switching frequency, including using pipelining to increase maximum frequency.Verilog HDL Verification

Verilog HDL Verificationdennis gookyi

Ěý

Static timing analysis (STA) determines if a circuit meets timing constraints without simulation. It computes delays for each path, finding critical paths. STA assumes no combinational feedback loops and broken register feedback paths. Paths include entry, stage, exit, and pad-to-pad. Timing constraints include clock period, setup time, hold time, input delay, output delay, and input-output delay. STA is used to verify timing but not functionality.FPGA Timing Models with electric motor system

FPGA Timing Models with electric motor systemsathyapriyar2350669

Ěý

FPGA Timing Models with electric motor systemTiming Analysis

- 1. TIMING ANALYSIS OF LOGIC CIRCUITS

- 2. Post layout simulation HDL Implementation Design Cycle DESIGN ENTRY Schematic , VHDL, Verilog, etc. Functional Simulation SYNTHESIS Test insertion Gate level simulation Implementation MAP, PLACE , ROUTE Static Timing Analysis Static Timing Analysis Libraries Constraints

- 3. The Timing Analyzer performs a static timing analysis of a mapped design A static timing analysis is a point-to-point analysis of a design network. The Timing Analyzer verifies that the delay along a given path or paths meets your specified timing requirements. It organizes and displays data that allows you to analyze the critical paths in your circuit, the cycle time of the circuit, the delay along any specified paths. Timing Analysis of Logic Circuits

- 4. Static timing analysis is performed at various stages of the design flow viz. after synthesis, after test insertion, after layout, etc. Your design's system performance is limited by some basic types of timing paths. Each of these paths goes through a sequence of logic, routing, and logic. Timing Analysis of Logic Circuits

- 5. Why Static Timing Analysis ? Verifying the timings of designs with millions of gates using dynamic timing analysis may prove to be impossible due to very high run times. Dynamic simulation relies on the quality and coverage of the test bench. Static timing analysis is very very fast as compared to dynamic analysis and verifies all parts of the gate level design. Static timing analysis does not check the functionality of the design. Extensive dynamic simulation is required to verify the functionality.

- 6. Pad to Pad A pad-to-pad path starts at an input pad of the chip, propagates through one or more levels of combinational logic, and ends at an output pad of the chip. The pad-to-pad path time is the maximum time required for the data to enter the chip, travel through logic & routing, and leave the chip. It is not controlled or affected by any clock signal.

- 7. Pad To Pad

- 8. Pad to Setup A pad-to-setup path starts at an input pad of the chip, propagates through input buffers and any number of combinatorial logic levels, and end at a D/T input to a flip-flop, latch or the receiving flip-flop’s t setup. Pad-to-set paths do not travel through flip-flops. The pad-to-setup path time is the maximum time required for the data to enter the chip, travel through logic and routing, and arrive at the input (D/T) before the clock or control signal arrives.

- 9. Pad To Setup

- 10. Clock To Pad Paths A clock-to-pad path starts at a clock input of a flip-flop, propagates through the flip-flop Q output and any number of levels of combinatorial logic, and ends at an output pad. It includes the clock-to-Q delay (Tpff) of the flip-flop and the path delay from that flip-flop to the chip output. The clock-to-pad path time is the maximum time required for the data to leave the source flip-flop, travel through logic & routing, and leave the chip.

- 11. Clock To Pad Paths

- 12. Clock To Pad Through Tristates

- 13. These are not valid clock to pad paths.

- 14. Clock To Setup - Same Clock

- 15. Rising Edge To Falling Edge Timing

- 16. Falling Edge To Rising Edge

- 17. Clock To Setup - Different Clocks

- 18. The paths ending at the clock pin of other FFs or the asynchronous pins of other FFs are not valid clock to setup paths. Clock enable pins ? They are similar to data. They will also have setup requirement.

- 19. Clock Pad To Clock Pin Of F/Fs

- 20. E.g. 1 What is the minimum clock period (Tmin) for this circuit? Hint: Evaluate all FF to FF paths

- 21. E.g. 1 contd. Path FFA to FFB TClk-Q(FFA) + Tpd(H) + Ts(FFB) = 5ns + 5ns+ 2ns = 12ns Path FFB to FFB TCLK-Q(FFB) + Tpd(F) + Tpd(H) + Ts(FFB) = 4ns + 4ns + 5ns + 2n = 15 ns So, Tmin=15 ns.

- 22. E.g. 2 Analysis of All The Paths In The Circuit

- 23. E.g. 2 Analysis of All The Paths In The Circuit Data at A, B, C and D is stable for 3 ns after the rising clock edge Data at X and Y has to be stable 3 ns before the rising clock edge. Calculate the maximum frequency of operation of the circuit. The delays are Tpd AND,OR= 1 ns, Tpd XOR= 2 ns, Tsetup= 1 ns, TclocktoQ = 3 ns.

- 24. E.g. 2 contd. Pad to Pad A to Y: (i) Tin-G4-Tout = 3+1+3=7ns (ii) Tin-G1-G4-Tout = 3+1+1+3=8ns

- 25. Pad to clock A-FF2D (i) Tin-G4-G7-TsetupFF2 =3+1+2+1=7ns (ii) Tin-G1-G4-G7-TsetupFF2 =3+1+1+2+1=8ns (iii) Tin-G5-G6-G7-TsetupFF2 =3+1+1+1+2+1=9ns C-FF2D: Tin-G3-G7-TsetupFF2 =3+1+2+1=7ns D-FF2D: Tin-G2-G5-G6-G7-TsetupFF2 =3+1+1+1+2+1=9ns C-FF2E Tin-G8-TsetupFF2 = 3+1+1=5ns D-FF2E Tin-G2-G5-G6-G8-TsetupFF2 =3+1+1+1+1+1=8ns

- 26. Clock to clock path FF1D – FF2D: (i)Tclk-QFF1-G1-G4-G7-TsetupFF2 = 3+1+1+2+1 = 8ns (ii) Tclk-QFF1-G1-G5-G6-G7-TsetupFF2 = 3+1+1+1+2+1 = 9ns (iii) Tclk-QFF1-G2-G5-G6-G7-TsetupFF2 = 3+1+1+1+2+1 = 9ns (iv)Tclk-QnFF1-G6-G7-TsetupFF2 = 3+1+2+1 = 7ns (iv)Tclk-QnFF1-G3-G7-TsetupFF2 = 3+1+2+1 = 7ns

- 27. Clock to clock path (contd.) FF1D – FF2E: (i) Tclk-QFF1-G1-G5-G6-G8-TsetupFF2 = 3+1+1+1+1+1 = 8ns (ii) Tclk-QFF1-G2-G5-G6-G8-TsetupFF2 = 3+1+1+1+1+1 = 8ns (iii)Tclk-QnFF1-G6-G8-TsetupFF2 = 3+1+1+1 = 6ns

- 28. Clock to Pad FF1 – Y: (i) Tclk-QFF1-G1-G4-Tout = 3+1+1+3 = 8ns FF2 – X (i) Tclk-QFF2-Tout = 3+3 = 6ns Maximum period between clk to clk paths is 9 ns Maximum frequency of operation = 1/9 =111.11 Mhz

- 29. THANK YOU