Decoders

11 likes8,589 views

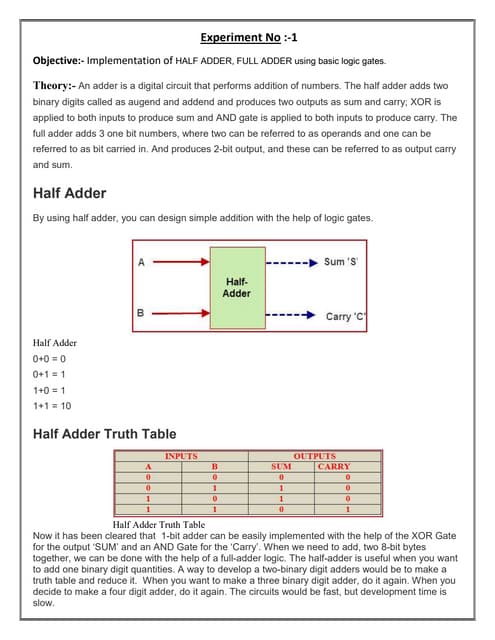

This document discusses decoders, which are circuits that take a binary input and activate one of multiple outputs. It provides examples of 2-to-4 and 3-to-8 decoders and their truth tables. Decoders are constructed using AND gates, with the number of gates equal to the number of outputs. Larger decoders can be built in parallel, balanced, or tree configurations, with balanced decoders requiring the fewest components.

1 of 21

Downloaded 196 times

Recommended

multiplexers and demultiplexers

multiplexers and demultiplexersUnsa Shakir

╠²

This document discusses multiplexers and demultiplexers. It defines them as devices that allow digital information from several sources to be routed onto a single line (multiplexers) or distributed to multiple output lines (demultiplexers). The key properties of multiplexers and demultiplexers are described, including the relationship between the number of inputs, outputs, and selection lines. Examples of implementing multiplexers and demultiplexers using logic gates are provided.Encoder & Decoder

Encoder & DecoderSyed Saeed

╠²

This document discusses decoders and encoders. It defines a decoder as a circuit that accepts a binary input and activates only one output corresponding to the input. An encoder is the inverse, converting an active input to a coded output. Various types of decoders and encoders are described, including 2-to-4 decoders, 3-to-8 decoders, priority encoders, decimal-to-BCD encoders, and octal-to-binary encoders. Truth tables and logic diagrams are provided as examples. Expansion of decoders using multiple lower-order decoders is also covered.sequential circuits

sequential circuitsUnsa Shakir

╠²

Sequential circuits have outputs determined by both the current inputs and previous outputs due to the inclusion of memory elements. Combinational circuits only have outputs determined by the current inputs. Sequential circuits contain logic gates arranged in parallel and feedback loops allowing the circuit to store past states, while combinational circuits only depend on the current input combination. There are different types of sequential circuits including those controlled by a clock signal from a clock generator that produces periodic pulses defining the circuit timing.Encoder

EncoderMahmudul Hasan

╠²

This presentation introduces encoders. It discusses that an encoder is a combinational circuit that performs the reverse operation of a decoder, with a maximum of 2n inputs and n outputs. The simplest encoder is a 2n-to-n binary encoder, where one of the 2n inputs is 1 and the output is an n-bit binary number representing the activated input. An example of an 8-to-3 binary encoder is shown, where only one of the 8 inputs can be activated at a time, and the 3 outputs represent the activated input in binary code.Sequential Logic Circuit

Sequential Logic CircuitRamasubbu .P

╠²

Sequential circuits consist of combinational logic and memory elements like latches and flip-flops. There are different types of latches and flip-flops that differ in their trigger mechanisms and outputs, including SR latches, D latches, and edge-triggered flip-flops like SR, D, and JK flip-flops. Asynchronous inputs can directly set or reset flip-flop outputs independent of the clock signal.Adder ppt

Adder pptAvinash Jadhav

╠²

This document discusses different types of digital adders. It defines an adder as a digital circuit that performs addition of numbers. It describes half adders, full adders, ripple carry adders, and look ahead carry units. For half adders, it provides the logic equations for sum and carry outputs. For full adders, it gives the logic equations for sum and carry outputs and includes the truth table. It explains that ripple carry adders use multiple full adders in sequence to add N-bit numbers, with each carry bit "ripplying" to the next full adder.Multiplexer and DeMultiplexer

Multiplexer and DeMultiplexerEstiak Khan

╠²

A multiplexer has multiple inputs and a single output line, using select lines to determine which input is connected to the output. It is used to increase the amount of data that can be sent over a network. A demultiplexer is the reverse, with one input and multiple output lines, using select lines to send a signal to one of the output lines. Both are used in communication systems, computer memory, and other applications to efficiently transmit data or connect parts of a system.Sequential circuits

Sequential circuitsParesh Parmar

╠²

This document discusses sequential circuits and their analysis. It defines sequential logic as circuits whose outputs depend not only on current inputs but also past inputs, requiring some type of memory. There are two types of sequential circuits: synchronous use a clock for synchronization, while asynchronous can change output at any time. Analysis of sequential circuits involves obtaining a description of the input-output-state sequence over time using techniques like logic diagrams, state tables, characteristic tables, and state diagrams. Various flip-flop designs are presented, including the SR latch, D latch using transmission gates, and master-slave flip-flop. Timing considerations like clock period and setup time are also covered.Shift Registers

Shift RegistersAbhilash Nair

╠²

Shift registers are digital circuits composed of flip-flops that can shift data from one stage to the next. They can be configured for serial-in serial-out, serial-in parallel-out, parallel-in serial-out, or parallel-in parallel-out data movement. Common applications include converting between serial and parallel data, temporary data storage, and implementing counters. MSI shift registers like the 74LS164 and 74LS166 provide 8-bit shift register functionality.Latches and flip flop

Latches and flip flopShuaib Hotak

╠²

This document discusses latches and flip flops, which are types of sequential logic circuits. It describes the basic components and functioning of latches like SR latches, D latches, and gated latches. For flip flops, it covers SR flip flops, D flip flops, JK flip flops, and master-slave flip flops. The key differences between latches and flip flops are that latches do not have a clock input while flip flops are edge-triggered by a clock signal. Latches and flip flops are used as basic storage elements in more complex sequential circuits and in computer components like registers and RAM.Multiplexers

MultiplexersDrSonali Vyas

╠²

A multiplexer is a device that selects one of several analog or digital input signals and forwards the selected input into a single line. It has multiple data inputs, a single output, and select lines that determine which input is directed to the output. A demultiplexer performs the opposite function, taking a single input and distributing it to one of multiple outputs based on the select lines. Multiplexers and demultiplexers come in various configurations depending on the number of inputs and outputs, such as 2:1, 4:1, 16:1 or 32:1. They are basic building blocks used in digital systems and communication networks to efficiently route signals.Combinational Circuits & Sequential Circuits

Combinational Circuits & Sequential Circuitsgourav kottawar

╠²

This document discusses and compares combinational and sequential circuits. It provides examples of common combinational circuits like half adders, full adders, decoders, and multiplexers. It also discusses sequential circuits elements like flip flops and shift registers. The document then focuses on adders in more detail, explaining half adders, full adders, and ripple carry adders through diagrams and examples.Half adder & full adder

Half adder & full adderGaditek

╠²

Group members for the project are Falah Hassan, Maidah Malik, and Maria Khan. The document discusses half adders and full adders. A half adder adds two binary digits and produces a sum and carry output. It is built from two logic gates. A full adder accepts two input bits and a carry input, and produces a sum and carry output. It is implemented using two half adders joined by an OR gate. The main difference between a half adder and full adder is that a full adder has three inputs and two outputs, allowing multiple adders to be chained to add more bits.Encoders and decoders

Encoders and decodersGaditek

╠²

Encoders and decoders are combinational logic circuits that convert between binary and encoded representations. An encoder converts data into a coded format, while a decoder converts the coded data back into its original form. Specific encoder and decoder circuits are discussed, including octal to binary encoders, priority encoders, binary decoders, BCD to decimal decoders, and BCD to seven segment decoders. Truth tables and schematic diagrams are provided to illustrate how these circuits function.SHIFT REGISTERS

SHIFT REGISTERSkumari36

╠²

Shift registers are constructed using flip-flops connected in a way to store and transfer digital data. Data is stored at the Q output of D flip-flops during a clock pulse. Shift registers allow data to be transferred between flip-flops upon a clock edge. There are four types of data movement: serial in serial out, serial in parallel out, parallel in serial out, and parallel in parallel out. Shift registers can be loaded serially or in parallel and are used in applications like pseudo random pattern generators, ring counters, and Johnson counters.Encoder and decoder

Encoder and decoderAbid Ali

╠²

An encoder is a circuit that takes a digital input and converts it to a binary code output. It performs the inverse operation of a decoder. There are different types of encoders like priority encoders, decimal to binary coded decimal encoders, and hexadecimal to binary encoders. A priority encoder gives priority to certain input lines such that if multiple lines are high, the output corresponds to the highest priority line. A decimal to BCD encoder takes a 10-bit decimal input and produces a 4-bit binary coded decimal output corresponding to each decimal value. Standard encoder integrated circuits like the 74HC147 implement common encoder functions.Multiplexers & Demultiplexers

Multiplexers & DemultiplexersJayanshu Gundaniya

╠²

Multiplexers and demultiplexers allow digital information from multiple sources to be routed through a single line. A multiplexer has multiple data inputs, select lines to choose an input, and a single output. A demultiplexer has a single input, select lines to choose an output, and multiple outputs. Bigger multiplexers and demultiplexers can be built by cascading smaller ones. Multiplexers can implement logic functions by using the select lines as variables and routing the input lines to the output.Introduction to Counters

Introduction to CountersISMT College

╠²

The document discusses synchronous and asynchronous counters. It defines a counter as a digital circuit that counts input pulses. Asynchronous counters have flip-flops that change state at different times since they do not share a common clock. Synchronous counters have all flip-flops change simultaneously due to a shared global clock, allowing them to operate at higher frequencies. The document provides examples of 2-bit, 3-bit, and 4-bit synchronous binary counters as well as a 4-bit synchronous decade counter along with their operations and timing diagrams. decoder and encoder

decoder and encoderUnsa Shakir

╠²

The document discusses encoders, decoders, multiplexers (MUX), and how they can be used to implement digital logic functions. It provides examples of using 4-to-1, 8-to-1 and 10-to-1 MUX to implement functions. It also gives examples of 4-to-2, 8-to-3 and 10-to-4 encoders. Decoder examples include a 2-to-4 and 3-to-8 binary decoder. The document explains how decoders can be used as logic building blocks to realize Boolean functions. It poses questions to be answered using terms like MUX, DEMUX, encoder, decoder.Counters

CountersKetaki_Pattani

╠²

This document discusses different types of counters used in digital circuits. It defines a counter as a sequential circuit that cycles through a sequence of states in response to clock pulses. Binary counters count in binary and can count from 0 to 2n-1 with n flip-flops. Asynchronous counters have flip-flops that are not triggered simultaneously by a clock, while synchronous counters use a common clock for all flip-flops. Other counter types include ring counters, Johnson counters, and decade counters. The document provides examples of binary, asynchronous, and synchronous counters and discusses their applications in areas like timing sequences and addressing memory.Encoder.pptx

Encoder.pptxPooja Dixit

╠²

This document discusses encoders and provides examples of 4-to-2 and 8-to-3 line encoders. It defines an encoder as a combinational circuit that performs the reverse operation of a decoder, with a maximum of 2n input lines and n output lines. Truth tables and logic circuits are given for 4-to-2 and 8-to-3 line encoders. Uses of encoders include converting decimal to binary numbers to perform binary operations like addition and subtraction in digital systems.Register in Digital Logic

Register in Digital LogicISMT College

╠²

A register is a group of flip-flops that can store multiple bits of data. There are four types of shift registers: serial-in serial-out (SISO), serial-in parallel-out (SIPO), parallel-in serial-out (PISO), and parallel-in parallel-out (PIPO). Shift registers allow data to move between flip-flops on each clock pulse. Ring counters and Johnson counters are examples of shift register counters that produce repeating output sequences.Combinational circuits

Combinational circuitsSARITHA REDDY

╠²

This document discusses combinational logic circuits such as adders, subtractors, multipliers, decoders, and multiplexers. It provides circuit diagrams and truth tables for half adders, full adders, half subtractors, full subtractors, decoders, and multiplexers. It also describes how to build binary adders and subtractors using these basic components and how multiplication of binary numbers is performed.Encoder and decoder

Encoder and decoderThen Murugeshwari

╠²

Encoders convert decimal input to binary coded decimal (BCD) output, while decoders convert BCD input to decimal output displayed on a 7-segment display. An example encoder converts decimal numbers to their BCD coded form, while an example decoder converts BCD codes into the decimal numbers they represent, which are then shown on a 7-segment LED display. The document provides examples of encodings and decoding between decimal, BCD, and 7-segment display representations and tests the reader with questions about decoding BCD inputs.Encoders and decoders

Encoders and decodersDeepikaDG1

╠²

This document discusses various encoders and decoders used in digital circuits. It describes decimal to BCD encoders that convert decimal numbers to binary coded decimal. Priority encoders are discussed that compress multiple inputs into fewer outputs based on priority. Decoders discussed include BCD to decimal decoders that convert BCD to decimal numbers, and seven segment decoders that convert codes to activate the segments of seven segment displays. Applications of encoders and decoders include data communications, compression, security, and making data human readable.Combinational circuits

Combinational circuits DrSonali Vyas

╠²

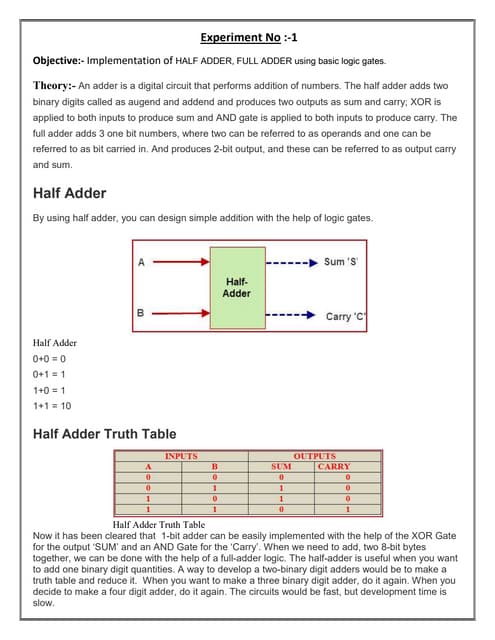

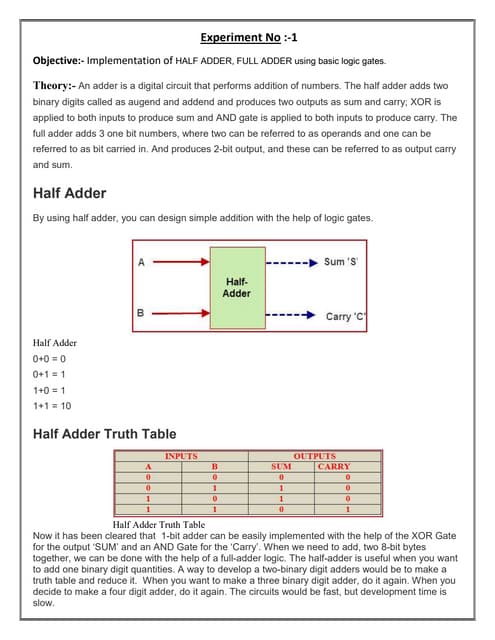

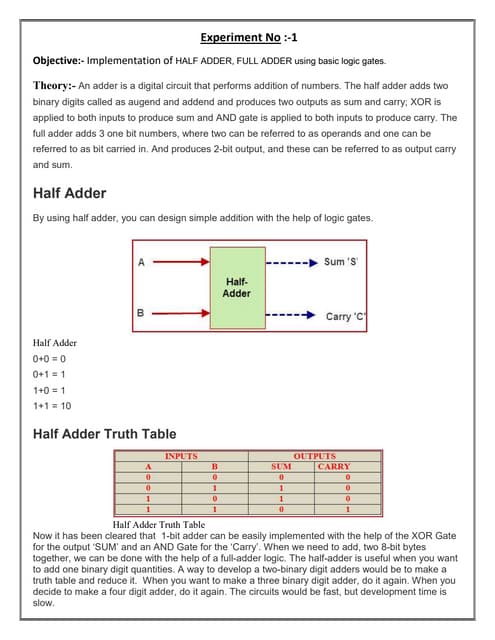

A combinational circuit is a logic circuit whose output is solely determined by the present input. It has no internal memory and its output depends only on the current inputs. A half adder is a basic combinational circuit that adds two single bits and produces a sum and carry output. A full adder adds three bits and produces a sum and carry like the half adder. Other combinational circuits discussed include half and full subtractors, decoders, encoders, and priority encoders.Registers and counters

Registers and countersHeman Pathak

╠²

1. The document discusses different types of registers, counters, and shift registers including their components, functions, and loading/shifting processes.

2. It also covers synchronous and asynchronous counters as well as ring and Johnson counters.

3. Finally, it discusses integrated circuits and different digital logic families including TTL, ECL, MOS, CMOS, and I2L.Logic gates and NAND and NOR univarsal gates

Logic gates and NAND and NOR univarsal gatesDhwanil Champaneria

╠²

This ppt contain all logic gates and NAND and NOR universal gates with their truth table useful for all students.Digital Logic Design Lectures on Flip-flops and latches and counters

Digital Logic Design Lectures on Flip-flops and latches and countersssuserb29fcb

╠²

DLD Lectures Digital Logic DesignATT SMK.pptx

ATT SMK.pptxMadhavKarve

╠²

A multiplexer is a digital circuit with multiple inputs and a single output. It selects one of the inputs using select lines and only allows one output at a time. A multiplexer can have 2, 4, 8, or more inputs depending on the number of select lines used. It is commonly used to route data within a computer from multiple sources to a single destination. Decoders are digital circuits that convert binary codes to activate a single output line. Common decoders include 2-to-4, 3-to-8, and 4-to-16 line decoders. Decoders are used whenever a specific combination of input levels needs to activate a single output. CMOS logic uses both n-type and p-type MOSMore Related Content

What's hot (20)

Shift Registers

Shift RegistersAbhilash Nair

╠²

Shift registers are digital circuits composed of flip-flops that can shift data from one stage to the next. They can be configured for serial-in serial-out, serial-in parallel-out, parallel-in serial-out, or parallel-in parallel-out data movement. Common applications include converting between serial and parallel data, temporary data storage, and implementing counters. MSI shift registers like the 74LS164 and 74LS166 provide 8-bit shift register functionality.Latches and flip flop

Latches and flip flopShuaib Hotak

╠²

This document discusses latches and flip flops, which are types of sequential logic circuits. It describes the basic components and functioning of latches like SR latches, D latches, and gated latches. For flip flops, it covers SR flip flops, D flip flops, JK flip flops, and master-slave flip flops. The key differences between latches and flip flops are that latches do not have a clock input while flip flops are edge-triggered by a clock signal. Latches and flip flops are used as basic storage elements in more complex sequential circuits and in computer components like registers and RAM.Multiplexers

MultiplexersDrSonali Vyas

╠²

A multiplexer is a device that selects one of several analog or digital input signals and forwards the selected input into a single line. It has multiple data inputs, a single output, and select lines that determine which input is directed to the output. A demultiplexer performs the opposite function, taking a single input and distributing it to one of multiple outputs based on the select lines. Multiplexers and demultiplexers come in various configurations depending on the number of inputs and outputs, such as 2:1, 4:1, 16:1 or 32:1. They are basic building blocks used in digital systems and communication networks to efficiently route signals.Combinational Circuits & Sequential Circuits

Combinational Circuits & Sequential Circuitsgourav kottawar

╠²

This document discusses and compares combinational and sequential circuits. It provides examples of common combinational circuits like half adders, full adders, decoders, and multiplexers. It also discusses sequential circuits elements like flip flops and shift registers. The document then focuses on adders in more detail, explaining half adders, full adders, and ripple carry adders through diagrams and examples.Half adder & full adder

Half adder & full adderGaditek

╠²

Group members for the project are Falah Hassan, Maidah Malik, and Maria Khan. The document discusses half adders and full adders. A half adder adds two binary digits and produces a sum and carry output. It is built from two logic gates. A full adder accepts two input bits and a carry input, and produces a sum and carry output. It is implemented using two half adders joined by an OR gate. The main difference between a half adder and full adder is that a full adder has three inputs and two outputs, allowing multiple adders to be chained to add more bits.Encoders and decoders

Encoders and decodersGaditek

╠²

Encoders and decoders are combinational logic circuits that convert between binary and encoded representations. An encoder converts data into a coded format, while a decoder converts the coded data back into its original form. Specific encoder and decoder circuits are discussed, including octal to binary encoders, priority encoders, binary decoders, BCD to decimal decoders, and BCD to seven segment decoders. Truth tables and schematic diagrams are provided to illustrate how these circuits function.SHIFT REGISTERS

SHIFT REGISTERSkumari36

╠²

Shift registers are constructed using flip-flops connected in a way to store and transfer digital data. Data is stored at the Q output of D flip-flops during a clock pulse. Shift registers allow data to be transferred between flip-flops upon a clock edge. There are four types of data movement: serial in serial out, serial in parallel out, parallel in serial out, and parallel in parallel out. Shift registers can be loaded serially or in parallel and are used in applications like pseudo random pattern generators, ring counters, and Johnson counters.Encoder and decoder

Encoder and decoderAbid Ali

╠²

An encoder is a circuit that takes a digital input and converts it to a binary code output. It performs the inverse operation of a decoder. There are different types of encoders like priority encoders, decimal to binary coded decimal encoders, and hexadecimal to binary encoders. A priority encoder gives priority to certain input lines such that if multiple lines are high, the output corresponds to the highest priority line. A decimal to BCD encoder takes a 10-bit decimal input and produces a 4-bit binary coded decimal output corresponding to each decimal value. Standard encoder integrated circuits like the 74HC147 implement common encoder functions.Multiplexers & Demultiplexers

Multiplexers & DemultiplexersJayanshu Gundaniya

╠²

Multiplexers and demultiplexers allow digital information from multiple sources to be routed through a single line. A multiplexer has multiple data inputs, select lines to choose an input, and a single output. A demultiplexer has a single input, select lines to choose an output, and multiple outputs. Bigger multiplexers and demultiplexers can be built by cascading smaller ones. Multiplexers can implement logic functions by using the select lines as variables and routing the input lines to the output.Introduction to Counters

Introduction to CountersISMT College

╠²

The document discusses synchronous and asynchronous counters. It defines a counter as a digital circuit that counts input pulses. Asynchronous counters have flip-flops that change state at different times since they do not share a common clock. Synchronous counters have all flip-flops change simultaneously due to a shared global clock, allowing them to operate at higher frequencies. The document provides examples of 2-bit, 3-bit, and 4-bit synchronous binary counters as well as a 4-bit synchronous decade counter along with their operations and timing diagrams. decoder and encoder

decoder and encoderUnsa Shakir

╠²

The document discusses encoders, decoders, multiplexers (MUX), and how they can be used to implement digital logic functions. It provides examples of using 4-to-1, 8-to-1 and 10-to-1 MUX to implement functions. It also gives examples of 4-to-2, 8-to-3 and 10-to-4 encoders. Decoder examples include a 2-to-4 and 3-to-8 binary decoder. The document explains how decoders can be used as logic building blocks to realize Boolean functions. It poses questions to be answered using terms like MUX, DEMUX, encoder, decoder.Counters

CountersKetaki_Pattani

╠²

This document discusses different types of counters used in digital circuits. It defines a counter as a sequential circuit that cycles through a sequence of states in response to clock pulses. Binary counters count in binary and can count from 0 to 2n-1 with n flip-flops. Asynchronous counters have flip-flops that are not triggered simultaneously by a clock, while synchronous counters use a common clock for all flip-flops. Other counter types include ring counters, Johnson counters, and decade counters. The document provides examples of binary, asynchronous, and synchronous counters and discusses their applications in areas like timing sequences and addressing memory.Encoder.pptx

Encoder.pptxPooja Dixit

╠²

This document discusses encoders and provides examples of 4-to-2 and 8-to-3 line encoders. It defines an encoder as a combinational circuit that performs the reverse operation of a decoder, with a maximum of 2n input lines and n output lines. Truth tables and logic circuits are given for 4-to-2 and 8-to-3 line encoders. Uses of encoders include converting decimal to binary numbers to perform binary operations like addition and subtraction in digital systems.Register in Digital Logic

Register in Digital LogicISMT College

╠²

A register is a group of flip-flops that can store multiple bits of data. There are four types of shift registers: serial-in serial-out (SISO), serial-in parallel-out (SIPO), parallel-in serial-out (PISO), and parallel-in parallel-out (PIPO). Shift registers allow data to move between flip-flops on each clock pulse. Ring counters and Johnson counters are examples of shift register counters that produce repeating output sequences.Combinational circuits

Combinational circuitsSARITHA REDDY

╠²

This document discusses combinational logic circuits such as adders, subtractors, multipliers, decoders, and multiplexers. It provides circuit diagrams and truth tables for half adders, full adders, half subtractors, full subtractors, decoders, and multiplexers. It also describes how to build binary adders and subtractors using these basic components and how multiplication of binary numbers is performed.Encoder and decoder

Encoder and decoderThen Murugeshwari

╠²

Encoders convert decimal input to binary coded decimal (BCD) output, while decoders convert BCD input to decimal output displayed on a 7-segment display. An example encoder converts decimal numbers to their BCD coded form, while an example decoder converts BCD codes into the decimal numbers they represent, which are then shown on a 7-segment LED display. The document provides examples of encodings and decoding between decimal, BCD, and 7-segment display representations and tests the reader with questions about decoding BCD inputs.Encoders and decoders

Encoders and decodersDeepikaDG1

╠²

This document discusses various encoders and decoders used in digital circuits. It describes decimal to BCD encoders that convert decimal numbers to binary coded decimal. Priority encoders are discussed that compress multiple inputs into fewer outputs based on priority. Decoders discussed include BCD to decimal decoders that convert BCD to decimal numbers, and seven segment decoders that convert codes to activate the segments of seven segment displays. Applications of encoders and decoders include data communications, compression, security, and making data human readable.Combinational circuits

Combinational circuits DrSonali Vyas

╠²

A combinational circuit is a logic circuit whose output is solely determined by the present input. It has no internal memory and its output depends only on the current inputs. A half adder is a basic combinational circuit that adds two single bits and produces a sum and carry output. A full adder adds three bits and produces a sum and carry like the half adder. Other combinational circuits discussed include half and full subtractors, decoders, encoders, and priority encoders.Registers and counters

Registers and countersHeman Pathak

╠²

1. The document discusses different types of registers, counters, and shift registers including their components, functions, and loading/shifting processes.

2. It also covers synchronous and asynchronous counters as well as ring and Johnson counters.

3. Finally, it discusses integrated circuits and different digital logic families including TTL, ECL, MOS, CMOS, and I2L.Logic gates and NAND and NOR univarsal gates

Logic gates and NAND and NOR univarsal gatesDhwanil Champaneria

╠²

This ppt contain all logic gates and NAND and NOR universal gates with their truth table useful for all students.Similar to Decoders (20)

Digital Logic Design Lectures on Flip-flops and latches and counters

Digital Logic Design Lectures on Flip-flops and latches and countersssuserb29fcb

╠²

DLD Lectures Digital Logic DesignATT SMK.pptx

ATT SMK.pptxMadhavKarve

╠²

A multiplexer is a digital circuit with multiple inputs and a single output. It selects one of the inputs using select lines and only allows one output at a time. A multiplexer can have 2, 4, 8, or more inputs depending on the number of select lines used. It is commonly used to route data within a computer from multiple sources to a single destination. Decoders are digital circuits that convert binary codes to activate a single output line. Common decoders include 2-to-4, 3-to-8, and 4-to-16 line decoders. Decoders are used whenever a specific combination of input levels needs to activate a single output. CMOS logic uses both n-type and p-type MOSSTLD-Combinational logic design

STLD-Combinational logic design Abhinay Potlabathini

╠²

The document discusses various topics related to combinational logic design including:

- The steps in the combinational logic design process including specification, formulation, optimization, technology mapping, and verification.

- Common functional blocks like decoders, encoders, multiplexers and their uses.

- Design of half adders, full adders, half subtractors, full subtractors and binary adders/subtractors.

- Implementation of logic functions using multiplexers and demultiplexers.

- Other topics like parity generators, code converters and hazards in combinational circuits.Chapter-04.pdf

Chapter-04.pdfssuserf7cd2b

╠²

This document discusses combinational circuit design and provides examples of various combinational logic circuits. It begins with an introduction that defines combinational and sequential circuits. The remainder of the document provides details on specific combinational logic circuits including half adders, full adders, subtractors, encoders, decoders, multiplexers, comparators, and code converters. Worked examples are provided for each circuit type using truth tables, Karnaugh maps, and logic diagrams. Applications of decoders for implementing functions like a full adder are also described.DLD Lecture No 22 Decoder Circuit and Types of Decoder.pptx

DLD Lecture No 22 Decoder Circuit and Types of Decoder.pptxSaveraAyub2

╠²

This document discusses different types of decoders and their implementation. It begins by defining a decoder as a combinational circuit that converts binary input to a maximum of 2^n unique output lines, with only one output active at a time. It then discusses a 3-to-8 line decoder as an example, which decodes 3 inputs into 8 outputs, with each output representing one of the minterms. The document also covers implementing decoders with NAND gates, the four types of decoders based on enable and output polarity, and techniques for constructing larger decoders.multiplexer and d-multiplexer

multiplexer and d-multiplexermalikwaqar75033149

╠²

The truth table is not complete because it is missing the encoding for when no inputs are active. A complete truth table would include a row for all zero inputs to specify the output in that case.

The output equations are:

A0 = D7

A1 = D6 + D5 + D4 + D3

A2 = D2 + D1 + D0

This encodes the highest priority input on the lowest two bits, with the next two highest priorities on the middle bit, and any active input setting the highest bit.UNIT3.3.pdf

UNIT3.3.pdfBunnyYadav7

╠²

This document discusses various digital logic components including encoders, decoders, multiplexers, and parity generators and checkers. It provides truth tables and logic diagrams for 8-to-3 encoders, 4-to-2 priority encoders, 2-to-4 decoders, 1-to-4 demultiplexers, even and odd parity generators, and even parity checkers. It also discusses implementing logic functions using multiplexers and decoders and gives examples of realizing functions with an 8x1 multiplexer. The document provides information on the basic operations of these components and their use in digital circuits.Ceng232 Decoder Multiplexer Adder

Ceng232 Decoder Multiplexer Addergueste731a4

╠²

The document discusses decoders, multiplexers, and programmable logic. It begins by explaining what decoders and multiplexers are, providing examples of 2-to-4 and 3-to-8 decoders. It then discusses how decoders and multiplexers can be used to implement arbitrary logic functions. The document also covers variations of decoders, building decoders from smaller components, and using multiplexers to efficiently implement functions in a sum of minterms form.encoder

encoder AshikUlMoula

╠²

This presentation discusses encoders. It defines an encoder as a combinational circuit that performs the reverse operation of a decoder, with a maximum of 2n inputs and n outputs. The simplest encoder is a 2n-to-n binary encoder, where only one of the 2n inputs is 1 at a time. Encoders convert a 1-out-of-2n input code to a binary output code, while decoders do the opposite. An example of an 8-to-3 binary encoder is shown, along with its truth table and simplified logic implementation using OR gates.Switching theory unit 2

Switching theory unit 2Dr. SURBHI SAROHA

╠²

This document provides an overview of switching theory unit 2, which covers combinational logic circuits and their design procedures. It discusses various combinational logic components like adders, subtractors, multiplexers, demultiplexers, encoders, and decoders. It provides block diagrams, truth tables, and logic expressions for designing these components. The key topics covered include the characteristics of combinational circuits, the 4-step design procedure for any combinational circuit, implementation of full adders and subtractors, working of multiplexers and demultiplexers of different sizes, and working of encoders and decoders.digital electronics..

digital electronics..Saurav Roy

╠²

This presentation introduces digital logic circuits such as encoders, decoders, multiplexers, demultiplexers and logic gates. It is presented by a group consisting of 5 members whose names and student IDs are listed. The topics covered include the definitions of complements, combinational logic circuits, encoder and decoder functions, how multiplexers and demultiplexers work, and the truth tables of common logic gates.08 decoder

08 decoderAamina Aslam

╠²

The document describes decoders and encoders. It begins by explaining what a decoder is, providing examples of 2-to-4 and 3-to-8 decoders. It then discusses how decoders can be used to implement general logic and combinational circuits using decoders and OR gates. The document proceeds to describe specific decoder chips like the 74x139 and 74x138 decoders. It also discusses using 3-state buffers with decoders and building decoders from smaller decoders. The document then shifts to discussing encoders, 7-segment decoders, truth tables, and K-maps in the design of decoders and encoders. It concludes by discussing priority encoders and the 74x148 priority encoder chip.Encoder_decoder_si.pdf

Encoder_decoder_si.pdfsimmis5

╠²

The document discusses different types of encoders and decoders used in digital circuits. It describes encoders that convert parallel inputs into binary codes, such as 4-to-2 and priority encoders. It also explains decoders that perform the reverse operation of encoders, such as 2-to-4 and 3-to-8 decoders that convert binary codes into activated outputs. Priority, BCD, and 7-segment decoders are discussed along with their applications in digital systems.Digital Logic Design Lecture on Counters and

Digital Logic Design Lecture on Counters andssuserb29fcb

╠²

Digital Logic Design Lecture on Counters and REgisters

Computer Organization And Architecture lab manual

Computer Organization And Architecture lab manualNitesh Dubey

╠²

The document discusses the implementation of various logic gates and flip-flops. It describes half adders and full adders can be implemented using XOR and AND gates. Binary to gray code and gray to binary code conversions are also explained. Circuit diagrams for 3-8 line decoder, 4x1 and 8x1 multiplexer are provided along with their truth tables. Finally, the working of common flip-flops like SR, JK, D and T are explained through their excitation tables.Encoder-and-decoder.pptx

Encoder-and-decoder.pptxKamranAli649587

╠²

Encoders convert input information like keyboard entries or switch states into binary codes for processing by digital systems. Decoders then convert the binary codes back into a format for output devices. Common examples include ASCII encoding text and BCD encoding decimals. Encoders have mutually exclusive inputs and output priority encoded binary codes. Decoders convert binary codes into at most one active output at a time.Lecture 8 Decoders & Encoders (combinational circuits)

Lecture 8 Decoders & Encoders (combinational circuits)andrewzimba02

╠²

explaining the logic circuits on decoders and encodersDigital logic-formula-notes-final-1

Digital logic-formula-notes-final-1Kshitij Singh

╠²

The document discusses number systems and coding schemes. It describes how to convert between decimal, binary, octal, hexadecimal and other number systems. It also discusses various coding schemes like binary coded decimal, excess-3 code, gray code, alphanumeric codes and complements. The key points are:

1) A number system with base 'r' contains 'r' different digits from 0 to r-1. Decimal to other bases conversions involve dividing the integer part by the base and multiplying the fractional part by the base.

2) Coding schemes discussed include binary coded decimal (BCD), excess-3 code, gray code, alphanumeric codes like EBCDIC.

3) Complements like 1's complementRecently uploaded (20)

How Engineering Model Making Brings Designs to Life.pdf

How Engineering Model Making Brings Designs to Life.pdfMaadhu Creatives-Model Making Company

╠²

This PDF highlights how engineering model making helps turn designs into functional prototypes, aiding in visualization, testing, and refinement. It covers different types of models used in industries like architecture, automotive, and aerospace, emphasizing cost and time efficiency.US Patented ReGenX Generator, ReGen-X Quatum Motor EV Regenerative Accelerati...

US Patented ReGenX Generator, ReGen-X Quatum Motor EV Regenerative Accelerati...Thane Heins NOBEL PRIZE WINNING ENERGY RESEARCHER

╠²

Preface: The ReGenX Generator innovation operates with a US Patented Frequency Dependent Load Current Delay which delays the creation and storage of created Electromagnetic Field Energy around the exterior of the generator coil. The result is the created and Time Delayed Electromagnetic Field Energy performs any magnitude of Positive Electro-Mechanical Work at infinite efficiency on the generator's Rotating Magnetic Field, increasing its Kinetic Energy and increasing the Kinetic Energy of an EV or ICE Vehicle to any magnitude without requiring any Externally Supplied Input Energy. In Electricity Generation applications the ReGenX Generator innovation now allows all electricity to be generated at infinite efficiency requiring zero Input Energy, zero Input Energy Cost, while producing zero Greenhouse Gas Emissions, zero Air Pollution and zero Nuclear Waste during the Electricity Generation Phase. In Electric Motor operation the ReGen-X Quantum Motor now allows any magnitude of Work to be performed with zero Electric Input Energy.

Demonstration Protocol: The demonstration protocol involves three prototypes;

1. Protytpe #1, demonstrates the ReGenX Generator's Load Current Time Delay when compared to the instantaneous Load Current Sine Wave for a Conventional Generator Coil.

2. In the Conventional Faraday Generator operation the created Electromagnetic Field Energy performs Negative Work at infinite efficiency and it reduces the Kinetic Energy of the system.

3. The Magnitude of the Negative Work / System Kinetic Energy Reduction (in Joules) is equal to the Magnitude of the created Electromagnetic Field Energy (also in Joules).

4. When the Conventional Faraday Generator is placed On-Load, Negative Work is performed and the speed of the system decreases according to Lenz's Law of Induction.

5. In order to maintain the System Speed and the Electric Power magnitude to the Loads, additional Input Power must be supplied to the Prime Mover and additional Mechanical Input Power must be supplied to the Generator's Drive Shaft.

6. For example, if 100 Watts of Electric Power is delivered to the Load by the Faraday Generator, an additional >100 Watts of Mechanical Input Power must be supplied to the Generator's Drive Shaft by the Prime Mover.

7. If 1 MW of Electric Power is delivered to the Load by the Faraday Generator, an additional >1 MW Watts of Mechanical Input Power must be supplied to the Generator's Drive Shaft by the Prime Mover.

8. Generally speaking the ratio is 2 Watts of Mechanical Input Power to every 1 Watt of Electric Output Power generated.

9. The increase in Drive Shaft Mechanical Input Power is provided by the Prime Mover and the Input Energy Source which powers the Prime Mover.

10. In the Heins ReGenX Generator operation the created and Time Delayed Electromagnetic Field Energy performs Positive Work at infinite efficiency and it increases the Kinetic Energy of the system.Mathematics behind machine learning INT255 INT255__Unit 3__PPT-1.pptx

Mathematics behind machine learning INT255 INT255__Unit 3__PPT-1.pptxppkmurthy2006

╠²

Mathematics behind machine learning INT255 Unit II: Design of Static Equipment Foundations

Unit II: Design of Static Equipment FoundationsSanjivani College of Engineering, Kopargaon

╠²

Design of Static Equipment, that is vertical vessels foundation.Best KNow Hydrogen Fuel Production in the World The cost in USD kwh for H2

Best KNow Hydrogen Fuel Production in the World The cost in USD kwh for H2Daniel Donatelli

╠²

The cost in USD/kwh for H2

Daniel Donatelli

Secure Supplies Group

Index

ŌĆó Introduction - Page 3

ŌĆó The Need for Hydrogen Fueling - Page 5

ŌĆó Pure H2 Fueling Technology - Page 7

ŌĆó Blend Gas Fueling: A Transition Strategy - Page 10

ŌĆó Performance Metrics: H2 vs. Fossil Fuels - Page 12

ŌĆó Cost Analysis and Economic Viability - Page 15

ŌĆó Innovations Driving Leadership - Page 18

ŌĆó Laminar Flame Speed Adjustment

ŌĆó Heat Management Systems

ŌĆó The Donatelli Cycle

ŌĆó Non-Carnot Cycle Applications

ŌĆó Case Studies and Real-World Applications - Page 22

ŌĆó Conclusion: Secure SuppliesŌĆÖ Leadership in Hydrogen Fueling - Page 27

15. Smart Cities Big Data, Civic Hackers, and the Quest for a New Utopia.pdf

15. Smart Cities Big Data, Civic Hackers, and the Quest for a New Utopia.pdfNgocThang9

╠²

Smart Cities Big Data, Civic Hackers, and the Quest for a New Utopiadecarbonization steel industry rev1.pptx

decarbonization steel industry rev1.pptxgonzalezolabarriaped

╠²

Webinar Decarbonization steel industryautonomous vehicle project for engineering.pdf

autonomous vehicle project for engineering.pdfJyotiLohar6

╠²

autonomous vehicle project for engineeringIndustrial Construction shed PEB MFG.pdf

Industrial Construction shed PEB MFG.pdfPLINTH & ROOFS

╠²

"Zen and the Art of Industrial Construction"

Once upon a time in Gujarat, Plinth and Roofs was working on a massive industrial shed project. Everything was going smoothlyŌĆöblueprints were flawless, steel structures were rising, and even the cement was behaving. That is, until...

Meet Ramesh, the Stressed Engineer.

Ramesh was a perfectionist. He measured bolts with the precision of a Swiss watchmaker and treated every steel beam like his own child. But as the deadline approached, RameshŌĆÖs stress levels skyrocketed.

One day, he called Parul, the total management & marketing mastermind.

¤øæ Ramesh (panicking): "Parul maŌĆÖam! The roof isn't aligning by 0.2 degrees! This is a disaster!"

¤żö Parul (calmly): "Ramesh, have you tried... meditating?"

¤Äż Ramesh: "Meditating? MaŌĆÖam, I have 500 workers on-site, and you want me to sit cross-legged and hum ŌĆśOmŌĆÖ?"

¤ōó Parul: "Exactly. Mystic of Seven can help!"

Reluctantly, Ramesh agreed to a 5-minute guided meditation session.

¤Æ© He closed his eyes.

¤¦śŌĆŹŌÖé’ĖÅ He breathed deeply.

¤öö He chanted "Om Namah Roofaya" (his custom version of a mantra).

When he opened his eyes, a miracle happened!

¤Ä» His mind was clear.

¤ōÅ The roof magically aligned (okay, maybe the team just adjusted it while he was meditating).

¤śü And for the first time, Ramesh smiled instead of calculating load capacities in his head.

Ō£© Lesson Learned: Sometimes, even in industrial construction, a little bit of mindfulness goes a long way.

From that day on, Plinth and Roofs introduced tea breaks with meditation sessions, and productivity skyrocketed!

Moral of the story: "When in doubt, breathe it out!"

#PlinthAndRoofs #MysticOfSeven #ZenConstruction #MindfulEngineeringOptimization of Cumulative Energy, Exergy Consumption and Environmental Life ...

Optimization of Cumulative Energy, Exergy Consumption and Environmental Life ...J. Agricultural Machinery

╠²

Optimal use of resources, including energy, is one of the most important principles in modern and sustainable agricultural systems. Exergy analysis and life cycle assessment were used to study the efficient use of inputs, energy consumption reduction, and various environmental effects in the corn production system in Lorestan province, Iran. The required data were collected from farmers in Lorestan province using random sampling. The Cobb-Douglas equation and data envelopment analysis were utilized for modeling and optimizing cumulative energy and exergy consumption (CEnC and CExC) and devising strategies to mitigate the environmental impacts of corn production. The Cobb-Douglas equation results revealed that electricity, diesel fuel, and N-fertilizer were the major contributors to CExC in the corn production system. According to the Data Envelopment Analysis (DEA) results, the average efficiency of all farms in terms of CExC was 94.7% in the CCR model and 97.8% in the BCC model. Furthermore, the results indicated that there was excessive consumption of inputs, particularly potassium and phosphate fertilizers. By adopting more suitable methods based on DEA of efficient farmers, it was possible to save 6.47, 10.42, 7.40, 13.32, 31.29, 3.25, and 6.78% in the exergy consumption of diesel fuel, electricity, machinery, chemical fertilizers, biocides, seeds, and irrigation, respectively. Multi objective genetic approach with Ranking

Multi objective genetic approach with Rankingnamisha18

╠²

Multi objective genetic approach with Ranking google_developer_group_ramdeobaba_university_EXPLORE_PPT

google_developer_group_ramdeobaba_university_EXPLORE_PPTJayeshShete1

╠²

EXPLORE 6 EXCITING DOMAINS:

1. Machine Learning: Discover the world of AI and ML!

2. App Development: Build innovative mobile apps!

3. Competitive Programming: Enhance your coding skills!

4. Web Development: Create stunning web applications!

5. Blockchain: Uncover the power of decentralized tech!

6. Cloud Computing: Explore the world of cloud infrastructure!

Join us to unravel the unexplored, network with like-minded individuals, and dive into the world of tech!US Patented ReGenX Generator, ReGen-X Quatum Motor EV Regenerative Accelerati...

US Patented ReGenX Generator, ReGen-X Quatum Motor EV Regenerative Accelerati...Thane Heins NOBEL PRIZE WINNING ENERGY RESEARCHER

╠²

Optimization of Cumulative Energy, Exergy Consumption and Environmental Life ...

Optimization of Cumulative Energy, Exergy Consumption and Environmental Life ...J. Agricultural Machinery

╠²

Decoders

- 1. DECODERS PRESENTED BY GHOLAMREZA KAKAMANSHADI PANJAB UNIVERSITY, CHD, INDIA JUL,2013

- 2. Definition: ŌĆó An important part of the system which selects the cells to be read from and written into is the decoder. ŌĆō Accepts a value and decodes it ŌĆó Output corresponds to value of n inputs ŌĆó It also is called many-to-one decoder, a decoder matrix or simply a decoder.

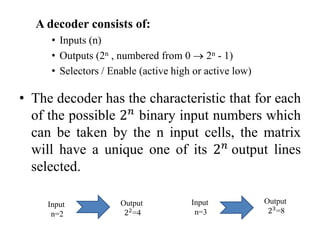

- 3. A decoder consists of: ŌĆó Inputs (n) ŌĆó Outputs (2n , numbered from 0 ’é« 2n - 1) ŌĆó Selectors / Enable (active high or active low) ŌĆó The decoder has the characteristic that for each of the possible 2 Øæø binary input numbers which can be taken by the n input cells, the matrix will have a unique one of its 2 Øæø output lines selected. Input n=2 Output 22=4 Input n=3 Output 23 =8

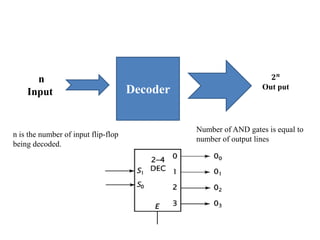

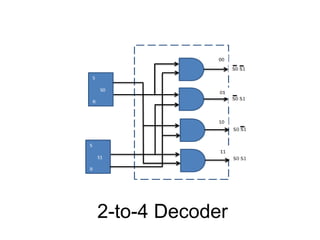

- 4. n Input Ø¤É ØÆÅ Out putDecoder n is the number of input flip-flop being decoded. Number of AND gates is equal to number of output lines

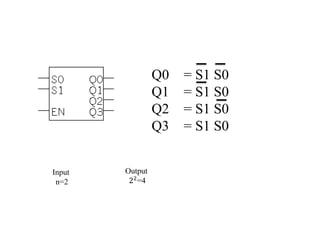

- 5. Q0 = S1 S0 Q1 = S1 S0 Q2 = S1 S0 Q3 = S1 S0 Input n=2 Output 22 =4

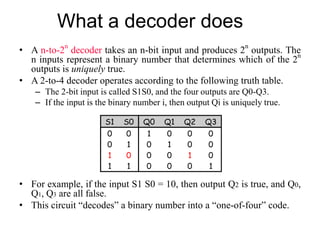

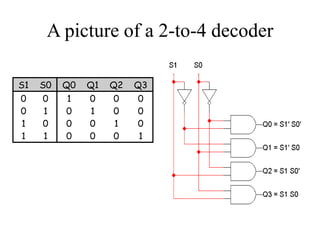

- 6. What a decoder does ŌĆó A n-to-2 n decoder takes an n-bit input and produces 2 n outputs. The n inputs represent a binary number that determines which of the 2 n outputs is uniquely true. ŌĆó A 2-to-4 decoder operates according to the following truth table. ŌĆō The 2-bit input is called S1S0, and the four outputs are Q0-Q3. ŌĆō If the input is the binary number i, then output Qi is uniquely true. ŌĆó For example, if the input S1 S0 = 10, then output Q2 is true, and Q0, Q1, Q3 are all false. ŌĆó This circuit ŌĆ£decodesŌĆØ a binary number into a ŌĆ£one-of-fourŌĆØ code. S1 S0 Q0 Q1 Q2 Q3 0 0 1 0 0 0 0 1 0 1 0 0 1 0 0 0 1 0 1 1 0 0 0 1

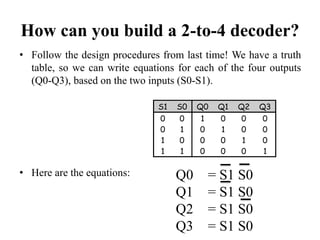

- 7. How can you build a 2-to-4 decoder? ŌĆó Follow the design procedures from last time! We have a truth table, so we can write equations for each of the four outputs (Q0-Q3), based on the two inputs (S0-S1). ŌĆó Here are the equations: S1 S0 Q0 Q1 Q2 Q3 0 0 1 0 0 0 0 1 0 1 0 0 1 0 0 0 1 0 1 1 0 0 0 1 Q0 = S1 S0 Q1 = S1 S0 Q2 = S1 S0 Q3 = S1 S0

- 8. A picture of a 2-to-4 decoder S1 S0 Q0 Q1 Q2 Q3 0 0 1 0 0 0 0 1 0 1 0 0 1 0 0 0 1 0 1 1 0 0 0 1

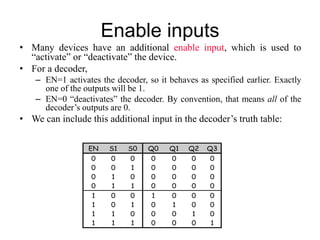

- 10. Enable inputs ŌĆó Many devices have an additional enable input, which is used to ŌĆ£activateŌĆØ or ŌĆ£deactivateŌĆØ the device. ŌĆó For a decoder, ŌĆō EN=1 activates the decoder, so it behaves as specified earlier. Exactly one of the outputs will be 1. ŌĆō EN=0 ŌĆ£deactivatesŌĆØ the decoder. By convention, that means all of the decoderŌĆÖs outputs are 0. ŌĆó We can include this additional input in the decoderŌĆÖs truth table: EN S1 S0 Q0 Q1 Q2 Q3 0 0 0 0 0 0 0 0 0 1 0 0 0 0 0 1 0 0 0 0 0 0 1 1 0 0 0 0 1 0 0 1 0 0 0 1 0 1 0 1 0 0 1 1 0 0 0 1 0 1 1 1 0 0 0 1

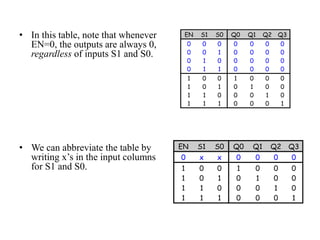

- 11. ŌĆó In this table, note that whenever EN=0, the outputs are always 0, regardless of inputs S1 and S0. ŌĆó We can abbreviate the table by writing xŌĆÖs in the input columns for S1 and S0. EN S1 S0 Q0 Q1 Q2 Q3 0 0 0 0 0 0 0 0 0 1 0 0 0 0 0 1 0 0 0 0 0 0 1 1 0 0 0 0 1 0 0 1 0 0 0 1 0 1 0 1 0 0 1 1 0 0 0 1 0 1 1 1 0 0 0 1 EN S1 S0 Q0 Q1 Q2 Q3 0 x x 0 0 0 0 1 0 0 1 0 0 0 1 0 1 0 1 0 0 1 1 0 0 0 1 0 1 1 1 0 0 0 1

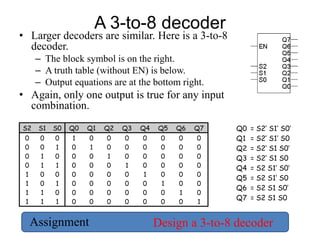

- 12. A 3-to-8 decoder ŌĆó Larger decoders are similar. Here is a 3-to-8 decoder. ŌĆō The block symbol is on the right. ŌĆō A truth table (without EN) is below. ŌĆō Output equations are at the bottom right. ŌĆó Again, only one output is true for any input combination. S2 S1 S0 Q0 Q1 Q2 Q3 Q4 Q5 Q6 Q7 0 0 0 1 0 0 0 0 0 0 0 0 0 1 0 1 0 0 0 0 0 0 0 1 0 0 0 1 0 0 0 0 0 0 1 1 0 0 0 1 0 0 0 0 1 0 0 0 0 0 0 1 0 0 0 1 0 1 0 0 0 0 0 1 0 0 1 1 0 0 0 0 0 0 0 1 0 1 1 1 0 0 0 0 0 0 0 1 Q0 = S2ŌĆÖ S1ŌĆÖ S0ŌĆÖ Q1 = S2ŌĆÖ S1ŌĆÖ S0 Q2 = S2ŌĆÖ S1 S0ŌĆÖ Q3 = S2ŌĆÖ S1 S0 Q4 = S2 S1ŌĆÖ S0ŌĆÖ Q5 = S2 S1ŌĆÖ S0 Q6 = S2 S1 S0ŌĆÖ Q7 = S2 S1 S0 Design a 3-to-8 decoderAssignment

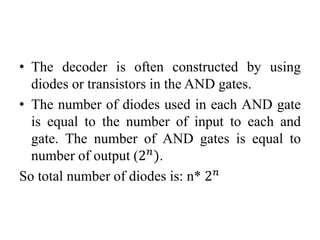

- 13. ŌĆó The decoder is often constructed by using diodes or transistors in the AND gates. ŌĆó The number of diodes used in each AND gate is equal to the number of input to each and gate. The number of AND gates is equal to number of output (2 Øæø ). So total number of diodes is: n* 2 Øæø

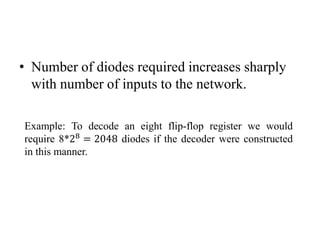

- 14. ŌĆó Number of diodes required increases sharply with number of inputs to the network. Example: To decode an eight flip-flop register we would require 8*28 = 2048 diodes if the decoder were constructed in this manner.

- 15. ŌĆó Several types of structures are often used in building of decoder networks. Example: ’üČ Parallel decoder ’üČ Balanced decoder ’üČ Tree decoder

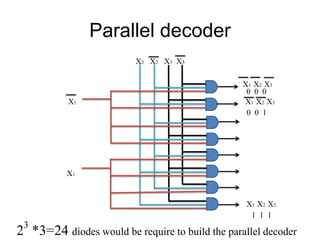

- 16. Parallel decoder X2 X2 X3 X3 X1 X1 X1 X2 X3 X1 X2 X3 X1 X2 X3 0 0 0 0 0 1 1 1 1 23 *3=24 diodes would be require to build the parallel decoder

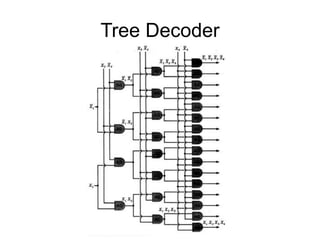

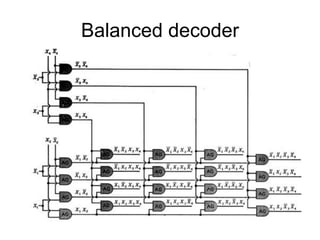

- 17. ŌĆó In tree network decoders there is four flip- flops and so has 24 =16 output lines. An examination will show that 56 diodes are required to build it. There is another type of decoder which is called a balanced decoder network. This network requires only 48 diodes. And it shown that this type of decoder network requires the minimum number of diodes.

- 18. Tree Decoder

- 19. Balanced decoder

- 20. ŌĆó The difference in the number of diodes or decoding elements to build a network such as balance decoders compared with parallel or tree decoders becomes more significant as the number of flip-flops to decoded increases. ŌĆó Parallel decoder network has the advantage of being fastest and most regular in construction of the three types.

- 21. The End