Osnovna logicka kola

- 1. OSNOVNA LOGIČKA KOLA I NJIHOVE REALIZACIJE

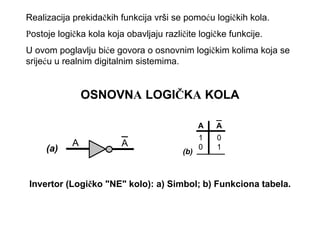

- 2. Realizacija prekidačkih funkcija vrši se pomoću logičkih kola. Postoje logička kola koja obavljaju različite logičke funkcije. U ovom poglavlju biće govora o osnovnim logičkim kolima koja se srijeću u realnim digitalnim sistemima. OSNOVNA LOGIČKA KOLA A A 1 0 A A 0 1 (a) (b) Invertor (Logičko "NE" kolo): a) Simbol; b) Funkciona tabela.

- 3. A A B A.B AB (a) B 0 0 0 0 1 0 1 0 0 (c) A B 1 1 1 (b) Logičko kolo "I": a) Simbol; b) Funkciona tabela; c) Ilustracija. A A +B A B A+B B (a) 0 0 0 0 1 1 A 1 0 1 1 1 1 (c) (b) B Logičko kolo "ILI": a) Simbol; b) Funkciona tabela; c) Ilustracija.

- 4. A B A.B 0 0 1 0 1 1 A A. B 1 0 1 (a) B (b) 1 1 0 Logičko kolo "NI": a) Simbol; b) Funkciona tabela. A B A+B 0 0 1 A 0 1 0 A+ B 1 0 0 B 1 1 0 (a) (b) Logičko kolo "NILI": a) Simbol); b) Funkciona tabela.

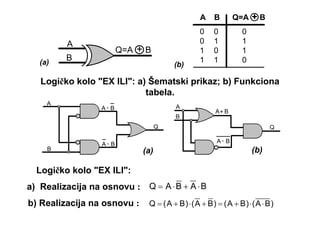

- 5. A B Q=A +B 0 0 0 A 0 1 1 Q=A + B 1 0 1 (a) B 1 1 0 (b) Logičko kolo "EX ILI": a) Šematski prikaz; b) Funkciona tabela. A A. B A A+ B B Q Q A. B A. B B (a) (b) Logičko kolo "EX ILI": a) Realizacija na osnovu : Q = A ⋅ B + A ⋅ B b) Realizacija na osnovu : Q = ( A + B) ⋅ ( A + B) = ( A + B) ⋅ ( A ⋅ B)

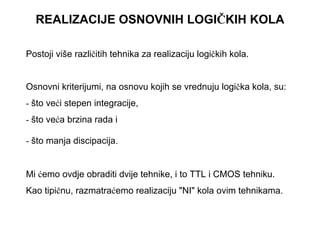

- 6. REALIZACIJE OSNOVNIH LOGIČKIH KOLA Postoji više različitih tehnika za realizaciju logičkih kola. Osnovni kriterijumi, na osnovu kojih se vrednuju logička kola, su: - što veći stepen integracije, - što veća brzina rada i - što manja discipacija. Mi ćemo ovdje obraditi dvije tehnike, i to TTL i CMOS tehniku. Kao tipičnu, razmatraćemo realizaciju "NI" kola ovim tehnikama.

- 7. Standardno TTL "NI" kolo sa dva ulaza. VCC =5V R C4 RC2 300 Ω 1,4K R B1 4K T4 A D T1 T2 B NI T3 R E2 1K Tranzistor T1 sa slike je dvoemitorski i može se ekvivalentirati sa dva tranzistora kojima su baze i kolektori međusobno spojeni.

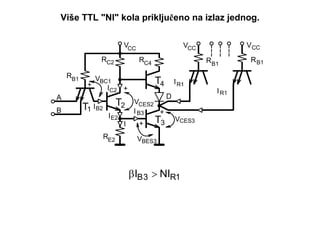

- 8. Više TTL "NI" kola priključeno na izlaz jednog. VCC VCC V CC RC2 RC4 R B1 R B1 RB1 VBC1 + T4 I R1 IC2 + I R1 A D T1 I B2 T2 VCES2 B I B3 + I E2 I + T3 VCES3 RE2 VBES3 βIB 3 > NIR1

- 9. CMOS kola Najpogodnija, za kola sa vrlo visokim stepenom integracije (VLSI), su tzv. CMOS kola, koja koriste komplementarne MOSFET-ove. ulaz izlaz +V DD +V DD G1 G2 MF2 +VDD n n p p n MF1 S1 p D1 D2 S2 (a) (b) CMOS Invertor: a) Struktura; b) Šema sa do sada korišćenim i alternativnim simbolima za MOSFET. Visok stepen +VDD integracije. 1 0 Ilustrativna šema CMOS invertora.

- 10. vi VDD =10V Vp vu 4 6 Prenosna karakteristika CMOS invertora. U praktičnim realizacijama teži se da prelazna oblast bude što kraća. Uvijek se usvaja neki napon iznad kojeg se nalazi nivo logičke jedinice i, veoma često, se ista vrijednost usvaja za gornju granicu logičke nule. Ovaj napon se naziva napon praga logičkog kola (Vp) i obično je, kod CMOS kola, jednak polovini napona napajanja logičkog kola (VDD/2). Ulazne struje kod ovih kola praktično su jednake nuli. Naponi, koji se koriste za napajanje CMOS kola, kreću se između 3V i 15V. U cilju zaštite kola od statičkog elektriciteta, dodaju se tzv. zaštitne diode.

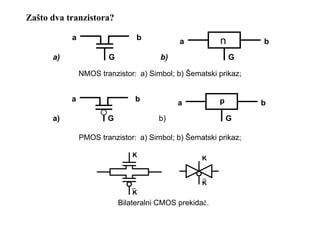

- 11. Zašto dva tranzistora? a b a n b a) G b) G NMOS tranzistor: a) Simbol; b) Šematski prikaz; a b a p b a) G b) G PMOS tranzistor: a) Simbol; b) Šematski prikaz; K K K K Bilateralni CMOS prekidač.

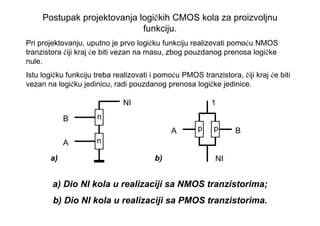

- 12. Postupak projektovanja logičkih CMOS kola za proizvoljnu funkciju. Pri projektovanju, uputno je prvo logičku funkciju realizovati pomoću NMOS tranzistora čiji kraj će biti vezan na masu, zbog pouzdanog prenosa logičke nule. Istu logičku funkciju treba realizovati i pomoću PMOS tranzistora, čiji kraj će biti vezan na logičku jedinicu, radi pouzdanog prenosa logičke jedinice. NI 1 B n A p p B A n a) b) NI a) Dio NI kola u realizaciji sa NMOS tranzistorima; b) Dio NI kola u realizaciji sa PMOS tranzistorima.

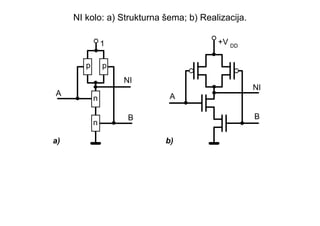

- 13. NI kolo: a) Strukturna šema; b) Realizacija. 1 +V DD p p NI NI A A n B B n a) b)

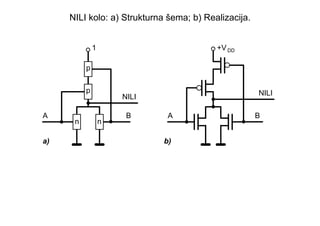

- 14. NILI kolo: a) Strukturna šema; b) Realizacija. 1 +V DD p p NILI NILI A B A B n n a) b)

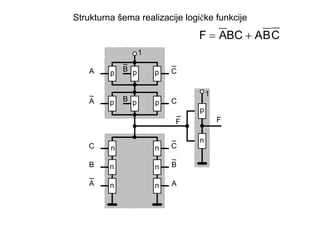

- 15. Strukturna šema realizacije logičke funkcije F = ABC + ABC 1 A B p p C p 1 A p B p p C p p F F n C n n C B n n B A n n A

- 16. Realizacija logičke funkcije u CMOS tehnologiji. +V DD F = ABC + ABC F F C C B B A A